- •Лекция 9

- •Счетчики

- •Типы счетчиков по способу построения

- •Типы счетчиков по способу счета

- •Счетчики на JK-триггерах

- •Счетная последовательность и диаграмма состояний

- •Нахождение функции на входах триггеров

- •Таблица возбуждения JK- триггера

- •Таблица переходов состояний

- •Составление карт Карно для счетчиков

- •Применение карт Карно для определения сигналов на входах

- •Функции на входах триггеров

- •Последовательность действий для построения счетчика

- •Счетчики на D-триггерах

- •Реализация счетчика на D- триггерах

- •Счетчики на RS-триггерах

- •Синхронные двоичные счетчики

- •Асинхронные счетчики

- •Языки высокого уровня Verilog и VHDL

- •Основные правила описания аппаратуры на языке Verilog

- •Основные правила описания аппаратуры на языке Verilog

- •Описание элемента 2И-НЕ на языке Verilog

- •Описание БЭ на языке Verilog

- •Описание D-триггера на языке

- •Описание сложных логических схем на языке Verilog

- •Тест программы сложных логических схем

- •Задания на лабораторную работу

Применение карт Карно для определения сигналов на входах

С BA |

00 |

01 |

11 |

10 |

С BA |

00 |

01 |

11 |

10 |

0 |

0 |

0 |

1 |

0 |

0 |

х |

х |

х |

х |

1 |

х |

х |

х |

х |

1 |

0 |

0 |

1 |

0 |

С |

BA |

00 |

01 |

JС =AB |

С |

BA |

00 |

01 |

KС=AB |

||||

11 |

10 |

11 |

10 |

||||||||||

|

|

0 |

|

0 |

1 |

х |

х |

|

0 |

х |

х |

1 |

0 |

|

|

1 |

|

0 |

1 |

х |

х |

|

1 |

х |

х |

1 |

0 |

|

BA |

|

JB =A |

|

|

BA |

|

KB =A |

|

||||

С |

00 |

01 |

11 |

10 |

С |

00 |

01 |

11 |

10 |

||||

JA=1 |

0 |

1 |

х |

х |

1 |

KA=10 |

х |

1 |

1 |

х |

|||

|

|

1 |

|

1 |

х |

х |

1 |

|

1 |

х |

1 |

1 |

х |

Функции на входах триггеров

•Таким образом из таблицы переходов состояний и из карт Карно получили:

a)JA=KA=1

b)JB=KB=A

c)JC=KC=AB

•Схема имеет вид:

Последовательность действий для построения счетчика

1.Нарисовать таблицу переходов состояний

2.Нарисовать карту Карно для сигналов на входах каждого триггера

3.Получить минимизированные функции для сигналов на входах триггеров

4.Нарисовать результирующую логическую схему счетчика

Счетчики на D-триггерах

•Используется

процедура, отработанная для JK- триггеров, с тем условием, что измениться таблица возбуждения

•Все триггеры должны управляться одним и тем же управляющим сигналом

Q → Q+ |

D |

0 → 0 |

0 |

1 → 1 |

1 |

0 → 1 |

1 |

1 → 0 |

0 |

С

DC

С

DA

Составление карт Карно для счетчика на D-триггерах

|

|

|

|

|

|

|

BA |

00 |

|

|

ABC |

|

|

|

01 |

11 |

||||

0 |

0 |

0 |

1 |

|||

1 |

1 |

1 |

0 |

|||

|

|

|

|

|

|

|

BA 00 |

|

BC |

|

|

||

01 |

11 |

|||||

0 |

1 |

0 |

0 |

|||

1 |

1 |

0 |

0 |

|||

10

0

1

10

1

1

С BA |

00 |

01 |

11 |

10 |

||||

|

|

|

||||||

0 |

0 |

1 |

0 |

|

1 |

|||

|

DB 1 |

0 |

1 |

0 |

|

1 |

||

|

|

|

|

|

|

|

|

|

|

AC |

|

|

|

|

|

|

|

|

AВ |

AВ |

||||||

|

A |

|||||||

|

|

|

|

|

|

|

||

•DC=ABC+AC+BC

•DB=AB+AB

•DA=A

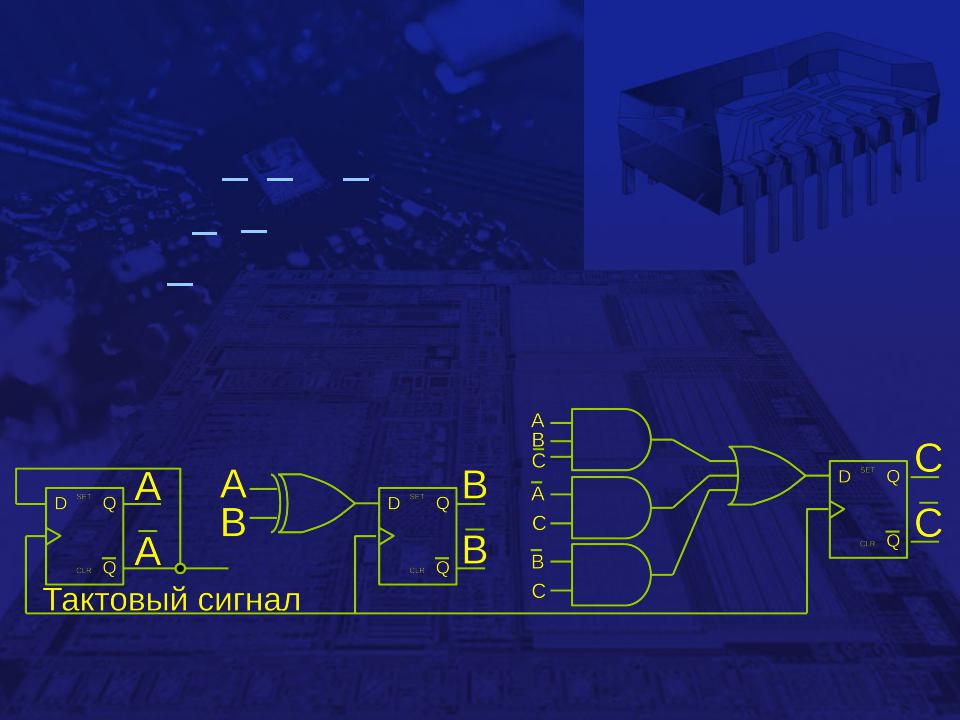

Реализация счетчика на D- триггерах

•DC=ABC+AC+BC

•DB=AB+AB

•DA=A

Счетчики на RS-триггерах

•Счетчики создаются аналогично созданию счетчиков на JK- и на D- триггерах, с учетом своей таблицы возбуждения

•Необходимо не забывать про запрещенные состояния

•Запрещенные состояния в карту Карно не записываются

Синхронные двоичные счетчики

•Обратного счета

•Реверсивные

•С произвольным коэффициентом счета

•Неполные

•Комбинированные

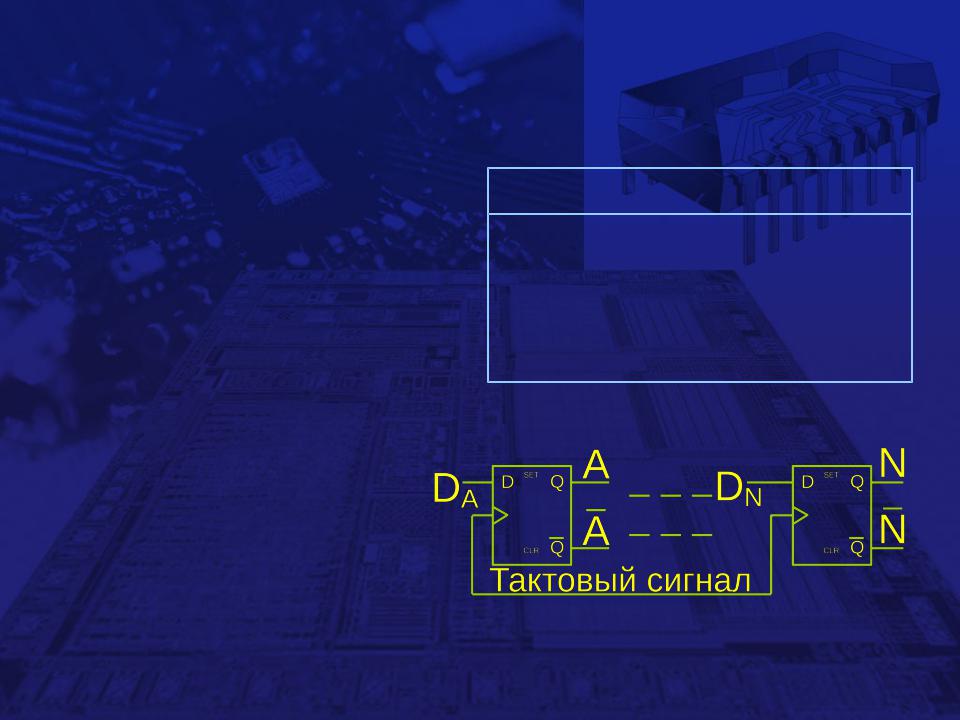

Асинхронные счетчики

•Если тактовый сигнал на один из триггеров

является выходным сигналом другого триггера, то счетчик является асинхронным

•Подумайте! Какую счетную последовательность осуществляет данный счетчик

Языки высокого уровня Verilog и VHDL

•Verilog и VHDL – это современные стандартные языки описания аппаратуры (не только цифровой, но и аналоговой (VHDL-AMS и Verilog-A))

•Похожесть:

–VHDL → ADA, PASCAL

–Verilog → C, С++

•Оба языка имеют больше общего чем различий