- •Лекция 15

- •Необходимость

- •Цели и задачи

- •Способ обнаружения неисправностей

- •Категории неисправностей

- •Типы логических неисправностей

- •Константные неисправности с залипанием в 1 или в 0

- •Константные неисправности с

- •Константные неисправности типа обрыв

- •Неисправности типа замыкание

- •Моделирование неисправностей

- •Модель 2х-входового вентиля И

- •Количество неисправностей

- •Множественные неисправности

- •Места возникновения неисправностей

- •Тестирование ИС

- •Методы поиска неисправностей

- •Прямой проход активизации пути

- •Обратный проход активизации пути

- •Упрощение поиска неисправностей

- •Алгоритм Рота

- •Поиск неисправностей по D- алгоритму

- •Эквивалентные неисправности

- •Не обнаруживаемые неисправности

- •Причина не обнаружения неисправностей

- •Тестирование последовательных схем

- •Метод сканирования пути

- •Модель Мура для тестирования по методу сканирования пути

- •Проверка работоспособности последовательных схем

- •Тестирование триггеров

- •Тестирование комбинационной логики следующего состояния

- •Тестирование комбинационной логики текущего состояния

- •Встроенное самотестирование

- •Периферийное сканирование

Алгоритм Рота

•Использование D подразумевает, что ни один нормальный сигнал в схеме нельзя назначать как D.

•На выход схемы передается сигнал D или его инверсия, и таким образом проверяется наличие неисправностей

Поиск неисправностей по D- алгоритму

•Каждый вентиль на пути до первичного выхода должен быть активизирован

•Если схема имеет неисправность внутри, то:

–Сначала устанавливаются состояния для получения D на выходе

–А затем состояния, для обнаружения неисправности

Эквивалентные неисправности

•Эквивалентные неисправности – это неисправности, которые детектируются одними и теми же тестовыми воздействиями (тестовыми векторами)

•Если существует хотя бы один тестовый вектор, обнаруживающий одну

неисправность и не обнаруживающий другую, то неисправности не эквивалентны

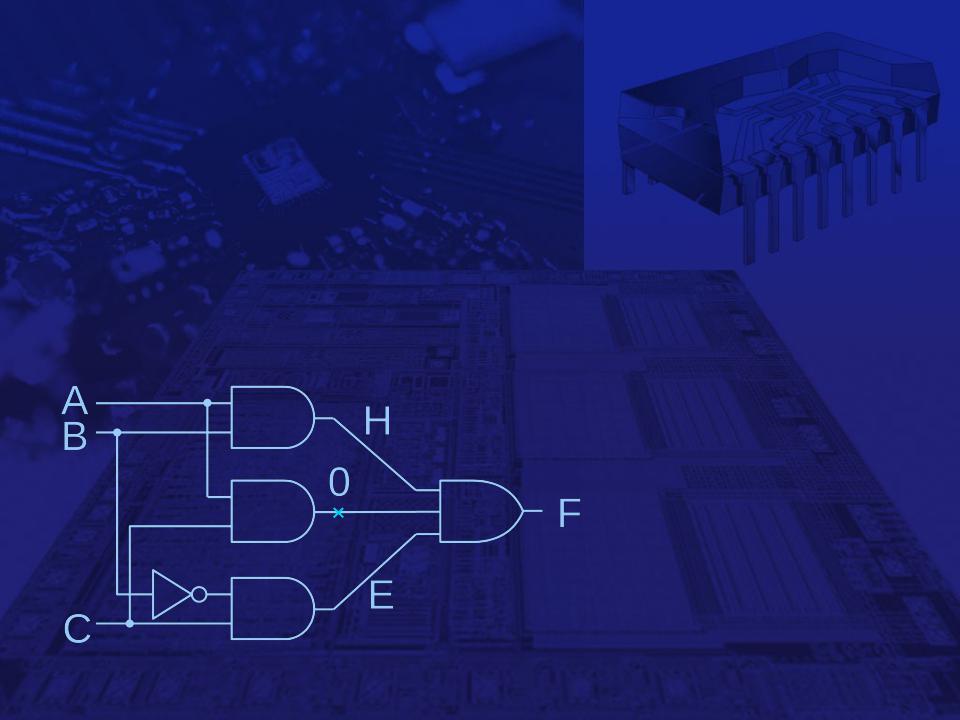

Не обнаруживаемые неисправности

•Существуют схемы, в которых нельзя однозначно сказать о наличии или отсутствии некоторых неисправностей:

•А=С=1;

•H=E=0 →

•B=0 для H=0

•B=1 для E=0

•Невозможно!!!

Причина не обнаружения неисправностей

•Избыточность схемы – фактор в результате которого схемы не чувствительны к тестирования

•F=AB+AC+BC=AB+BC

|

|

|

|

|

|

А ВС 00 |

01 |

ВС |

10 |

||

11 |

|||||

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

1 |

|

|

|

АС |

|

|

АВ |

Тестирование последовательных схем

•Для тестирования последовательных схем необходимо:

–Установить схему в известное состояние

–После подачи сигналов состояние должно измениться в другое известное состояние

•При этом оба состояния (текущее и следующее) должны поддаваться наблюдению

Метод сканирования пути

•Используется для обнаружения переменных состояний

•Режимы работы схемы:

–Нормальный режим – схема работает согласно ТЗ

–Режим сканирования пути – триггеры подключаются как сдвиговый регистр с последовательным входом и последовательным выходом

Модель Мура для тестирования по методу сканирования пути

Проверка работоспособности последовательных схем

•Тестирование триггеров

•Тестирование комбинационной логики следующего состояния

•Тестирование комбинационной логики текущего состояния

Тестирование триггеров

•Осуществляется через тестирование регистра сдвига

•Mode_select=1

•Через мультиплексор триггеры подключаются последовательно и выстраиваются в сдвиговый регистр, по которому двигается известная последовательность кода и проводится его сравнение с кодом, полученным на выходе