- •Лекция 7

- •Комбинационные схемы

- •Дешифратор

- •Дешифратор

- •Дешифратор из 3 линий в 8 обозначение и принцип работы

- •Дешифратор из 3 линий в 8 функции и реализация

- •Применение дешифраторов

- •Реализация комбинационной логической функции

- •Демультиплексор

- •Функциональная схема демультиплексора

- •Мультиплексор

- •Функциональная схема мультиплексора из 8 линий в 1

- •Применение мультиплексоров

- •Арифметические схемы

- •Сложение

- •Полусумматор

- •Полный сумматор

- •Суммирование двух n-битных чисел

- •Реализация полусумматора и сумматора

- •Вычитание

- •Вычитание пары двоичных чисел

Мультиплексор

•Мультиплексор – это устройство, которое позволяет выбирать только один из набора входных сигналов и передавать его на единственный выход

•Мультиплексор – устройство обратное демультиплексору

•Мультиплексор называется селектором данных или мультиплексором из N линий в 1

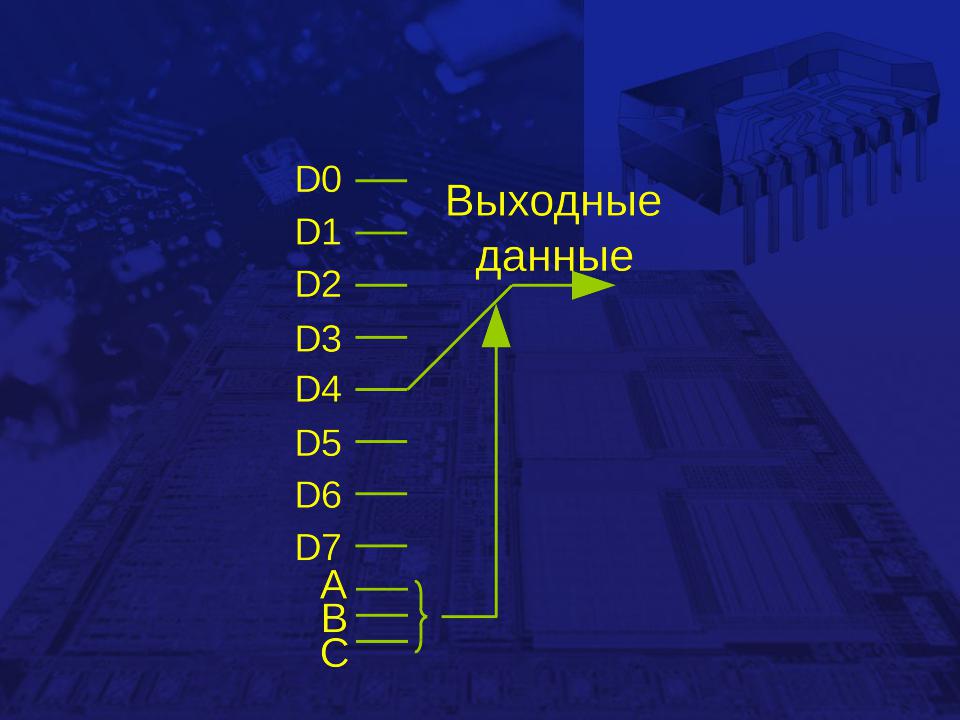

Функциональная схема мультиплексора из 8 линий в 1

Применение мультиплексоров

•Дешифратор адреса (передача на выход значений в заданном адресе или модуле)

•Схема управления шиной данных (передача по одной линии данных из нескольких различных модулей)

•Реализация логических функций (осуществляется при установке на входы высоких уровней напряжения и выборе его сигналами управления)

Арифметические схемы

•Для выполнения различных арифметических операций компьютеры должны содержать специальные логические схемы

•Арифметические схемы требуются и в других цифровых схемах

•Основные арифметические операции:

сложение и вычитание

Сложение

•На первой лекции было рассмотрено арифметическое сложение двухзначных чисел

•Для реализации такого сложения необходимо устройство, способное складывать два младших значащих двоичных разряда слагаемых чисел

•Таким устройством является

полусумматор (half adder)

Полусумматор

•Полусумматор содержит 2 входа и 2 выхода, и реализует следующую функцию:

A |

B |

Сумма |

Перенос |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

•Кроме того, необходима схема, которая суммировала бы два следующих двоичных

числа и бит переноса от предыдущего разряда – полный сумматор (full adder)

Полный сумматор

•Полный сумматор имеет 3 входа и 2 выхода и имеет таблицу истинности:

A |

B |

Свх |

Свых |

Сумма |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

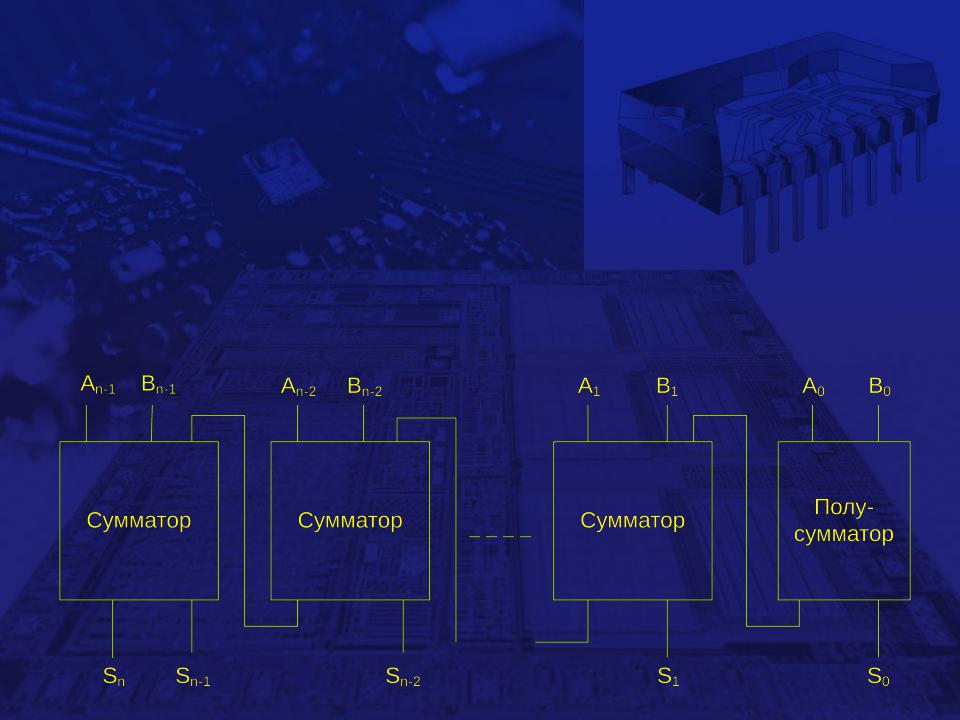

Суммирование двух n-битных чисел

•Для суммирования потребуется 1 полусумматор и n-1 полных сумматоров

•Схема носит название параллельного сумматора (parallel adder)

Реализация полусумматора и сумматора

Вычитание

•Вычитание числа В из числа А выполняется путем суммирования отрицательного числа В в дополнительном коде (инверсия всех битов с добавлением 1) с числом А.

•Прибавление 1 бита к инверсному значению числа В легко осуществить используя в схеме параллельного сумматора вместо полусумматора полный сумматор