Деформирование длительности выходных сигналов

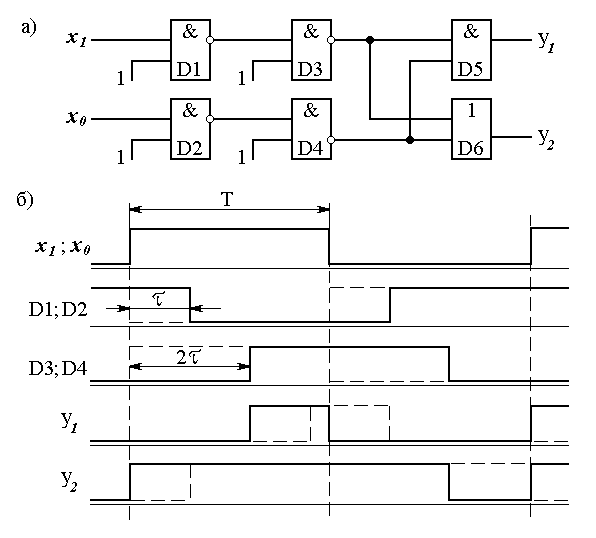

Если сигналы в схеме распространяются по цепочкам, задержки в которых различны, то это приводит к смещению сигналов относительно друг друга во времени. В свою очередь, это может вызвать уменьшение длительности сигнала “1” на выходе элемента И и увеличение - на выходе ИЛИ. На рис. 5 приведены схема и временные диаграммы, поясняющие деформирование длительности выходных сигналов при переключении инерционных логических элементов.

Рис. 5. Деформирование длительности выходных сигналов

У выходных сигналову1и

у2

в начале и в конце будут зоны неопределенности

длительностью по 3τ

каждая. В частном случае при τ=

0 выходные сигналы у1и

у2

почти повторяют входные. Однако если

задержки

τ

максимальны,

то на входах элементов D5 и D6 они могут

появиться с разбросом по времени на 2τ.

Понятие одновременности расплывается

и становится относительным. В худшем

случае сигнал у1будет

иметь длительность Т

– 2τ,

а у2

- Т + 2τ

, причем фронты (спады) этих сигналов

могут быть сдвинуты по отношению к

входным сигналам на 3τ.

Возможны и любые промежуточные формы

рассмотренных частных случаев, причем

предугадать характер деформирования

заранее невозможно. Если цепочка до

входов элементов D5 и D6 содержит k

элементов, то во всех рассмотренных

случаях вместо двойки в качестве

множителя при τ

войдет k.

У разработчика нет никаких официальных

документов, позволяющих проигнорировать

любой из возможных эффектов, и он вынужден

проектировать схему так, чтобы ни один

из них не привел к сбою в работе. Если

на выходе схемы требуется получить

импульс с длительностью Т,

то длительность импульса на входе

цепочки должна быть на kτ

больше. Аналогично нужно обеспечивать

на выходе схемы и минимальную длительность

паузы и максимальную длительность

импульса, если это требуется. Двухстороннего

допуска на длительность импульса, менее

жесткого, чем ±kτ,

требовать нельзя.

выходных сигналову1и

у2

в начале и в конце будут зоны неопределенности

длительностью по 3τ

каждая. В частном случае при τ=

0 выходные сигналы у1и

у2

почти повторяют входные. Однако если

задержки

τ

максимальны,

то на входах элементов D5 и D6 они могут

появиться с разбросом по времени на 2τ.

Понятие одновременности расплывается

и становится относительным. В худшем

случае сигнал у1будет

иметь длительность Т

– 2τ,

а у2

- Т + 2τ

, причем фронты (спады) этих сигналов

могут быть сдвинуты по отношению к

входным сигналам на 3τ.

Возможны и любые промежуточные формы

рассмотренных частных случаев, причем

предугадать характер деформирования

заранее невозможно. Если цепочка до

входов элементов D5 и D6 содержит k

элементов, то во всех рассмотренных

случаях вместо двойки в качестве

множителя при τ

войдет k.

У разработчика нет никаких официальных

документов, позволяющих проигнорировать

любой из возможных эффектов, и он вынужден

проектировать схему так, чтобы ни один

из них не привел к сбою в работе. Если

на выходе схемы требуется получить

импульс с длительностью Т,

то длительность импульса на входе

цепочки должна быть на kτ

больше. Аналогично нужно обеспечивать

на выходе схемы и минимальную длительность

паузы и максимальную длительность

импульса, если это требуется. Двухстороннего

допуска на длительность импульса, менее

жесткого, чем ±kτ,

требовать нельзя.

Сказанное позволяет сделать вывод, что деформирование выходного сигнала может настолько уменьшить длительность уровней “1” и “0”, что элементы D5 и D6 могут стать для них фильтрами, то есть полностью нарушить логику работы схемы. Итак, деформирование выходного сигнала может привести к исчезновению алгоритмически верного сигнала.

Статические риски сбоя

На

рис. 6 показана работа элементовИ

и ИЛИ

при подаче на их входы двух последовательных

во времени наборов Х1

= x1x0=

01

и Х2

= x1x0=

10.

Значение сигнала у1для

элемента И

на этих наборах должно оставаться

постоянным и равным 0,

а у2

– равным

1.

Это выполняется для случаев разброса

во времени моментов переключения

переменных

x1

и

x0,

показанных на рис. 6, а

и г.

На

рис. 6 показана работа элементовИ

и ИЛИ

при подаче на их входы двух последовательных

во времени наборов Х1

= x1x0=

01

и Х2

= x1x0=

10.

Значение сигнала у1для

элемента И

на этих наборах должно оставаться

постоянным и равным 0,

а у2

– равным

1.

Это выполняется для случаев разброса

во времени моментов переключения

переменных

x1

и

x0,

показанных на рис. 6, а

и г.

Рис. 6. Разброс во времени моментов переключения

Если же этот разброс соответствует рис. 6, б и в, то видно, что на выходе схемы И появится логический сигнал 1 длительностью Δτ1, а на выходе схемы ИЛИ - сигнал 0 длительностью Δτ2. Эти ложные сигналы и являются рисками сбоя, причем видно, что они могут быть, а могут и отсутствовать. Все дальнейшие примеры будут иллюстрироваться временными диаграммами для наихудшего случая, когда риск сбоя обязательно имеет место.

Риск сбоя называется статическим, если у(X1) = y(Х2), где y - булева функция. Риск сбоя называется статическим в нуле S0, если у(X1) = y(Х2) = 0. Риск сбоя называется статическим в единице S1, если у(X1) = y(Х2) = 1. Итак, на рис. 6, б имеет место статический риск сбоя в нуле S0, а на рис. 6, в - статический риск сбоя в единице S1.

Существенно, что полученные помехи S0 и S1 (иногда их называют “иголками”, “мерцаниями”, “глитчами” (англ. glitch)) - это не пренебрежимо короткий всплеск напряжения малой амплитуды. При достаточно большой разности Δτ помеха будет иметь длительность, во много раз превышающую время переключения элемента, и амплитуду, равную номинальному сигналу. Это уже полноценный сигнал, на который могут реагировать последующие элементы (входы синхронизации, установки в 0 или 1, загрузки данных и т. п.). Такие помехи - страшная вещь для цифровых схем, тем более, что их практически невозможно увидеть на осциллографе, и разработчик просто не будет знать об их существовании. Они могут сужаться до полного исчезновения, но могут и расширяться, проходя через логические цепи.