- •Московский государственный институт электронной техники (технический университет)

- •Теоретические сведения

- •Основные операции получения кремниевых пластин диаметром 100 - 150 мм

- •Основные параметры пластин кремния для производства ис

- •Основные сведении of) элементах структур полупроводниковых ис и бис

- •Зависимость цвета термически выращенной Пленки двуокиси кремния от ее толщийы

Московский государственный институт электронной техники (технический университет)

А.В.Заводян

х . ' .

Изучение планарно-эпитаксиальной технологии изготовления микросхем на биполярных транзисторах

Лабораторная работа № 4

Методические указания к лабораторному практикуму по курсу "ТИКИМС"

Под редакцией профессора Л.А.Коледова

Москва 1998

Министерство общего и профессионального образования Российской Федерации

Московский государственный институт электронной техники (Технический университет)

А.В.Заводян

Изучение планарно-эпитаксиальной технологии изготовления микросхем на биполярных транзисторах

Лабораторная работа № 4

Методические указания к лабораторному практикуму по курсу -ТИКИМС"

Под редакцией профессора Л.А,Коледова Утверждено редакционно-шцпсльским советом института

Мои г.;» \{W

УДК 621.382.8

Рецензент канд. техн. наукВ.ПМривалов

Заводян А.В.

Изучение планарно-эпитаксиальной технологии изготовления микросхем на биполярных транзисторах. Лабораторная работа № 4. Методические указания к лабораторному практикуму по курсу "ТИКИМС" /Под ред. Л.А.Коледова. -М.: МИЭТ, 1998. - 88с.: ил.

Изложены сведения, касающиеся изготовления полупроводниковых микросхем, включая перспективные технологии. Рассмотрены методы контроля качества выполнения отдельных технологических операций.

Предназначены для студентов старших курсов, обучающихся по специальности "Конструирование и производство ЭВС", при освоении и закреплении лекционного курса "ТИКИМС". Могут быть полезны студентам других специальностей, изучающим дисциплины "Микроэлектроника", "Спецэлектроника", "Технологические основы микроэлектроники" и т.п.

© МИЭТ, 1998

Цель работы: 1)изучить технологические операции производства полупроводниковых микросхем, а также их последовательность при изготовлении полупроводниковых микросхем на биполярных транзисторах, 2)ознакомиться с оборудованием и материалами, применяемыми при производстве полупроводниковых микросхем; 3)ознакомиться с методами измерения параметров слоев полупроводниковых микросхем;

4)научиться определять толщину пленок двуокиси кремния, эпитакси-альных и диффузионных слоев.

Продолжительность работы - 4 ч.

Теоретические сведения

Общая технологическая схема процессов производства полупроводниковых микросхем (или интегральных схем (ИС)) включает подготовительные процессы, формирование структуры ИС, в том числе межсоединений ее элементов, и заключительные процессы.

К подготовительным процессам относятся изготовление требуемого комплекта фотошаблонов и ряд заготовительных операций: подготовка полупроводниковых подложек (пластин), корпусов ИС и др.

Формирование структуры полупроводниковой ИС происходит по планарно-эпитаксиальной технологии, заключающейся в создании элементов ИС в приповерхностных слоях полупроводниковой пластины с одной (рабочей) стороны при использовании эпитаксиального наращивания тонкого слоя кремния и групповой обработки пластин. Причем отдельные процессы групповой обработки, например фотолитография, диффузия примесей, окисление, очистка поверхности пластины, носят циклический характер, т.е. обычно многократно повторяются при синтезе структуры полупроводниковых ИС и каждая последовательность процессов формирует определенную часть структуры ИС. Изменение количества таких последовательностей дает возможность получать полупроводниковые ИС различной сложности. При этом физико-химическая сущность повторяющихся процессов часто остается неизменной, а меняются только технологические режимы, фотошаблоны. используемые для фотолитографии, и некоторые материалы технологических сред*. Формирование структуры ИС заканчивается получением

* Под технологической средой следует понимать совокупность технологических материалов и воздействий, обеспечивающих требуемую реализацию синтеза объекта производства.

межсоединений элементов и защитой (кроме выводных контактных площадок) полупроводниковой ИС пассивирующим покрытием.

Заключительные процессы обычно представляют собой совокупность индивидуальных обработок объекта производства, включая контроль функциональных параметров ИС и разбраковку кристаллов, разделение пластин на кристаллы, сборку и монтаж кристаллов в корпусах, герметизацию, выходной контроль, механические и климатические испытания, покраску корпусов ИС (при необходимости), маркировку, лакировку (при необходимости) и упаковку готовых ИС

Изготовление полупроводниковых подложек

В настоящее время основная часть монокристаллических полупроводников производится в виде слитков определенного диаметра, являющихся заготовками в производстве подложек (пластин). Для изготовления полупроводниковых ИС на биполярных транзисторах с изоляцией элементов обратносмещенными р - ппереходами обычно используют пластины, получаемые из кремниевых слитков марки КДБ К) (кремний дырочного типа проводимости, с номинальным удельным сопротивлением 10Ом-см, легированный бором), ориентированных по кристаллографическим плоскостям [111)либо [100| Изготовление полупроводниковых пластин включает следующие основные технологические этапы, предварительную подготовку слитка, разделение его на пластины, формирование фасок, шлифование пластин, их химическое травление, полирование и очистку.

Предварительная подготовка слитка заключается в калибровке его наружного диаметра до заданного размера способом наружного круглого шлифования в несколько проходов алмазными кругами на металлической связке (сначала используют алмазные круги зернистостью 160 -250мкм. затем 40 - 63мкм). После калибровки на слитке выполняют также шлифованием (со связанным или свободным абразивом) базовый срез (для базирования пластин на операциях фотолитографии) и дополнительные срезы (один или два для обозначения кристаллографической ориентации пластин и типа проводимости полупроводниковых материалов, причем для слитков марки КДБ 10с кристаллографической ориентацией [111]дополнительные срезы не делают). Ширина базового и дополнительных срезов и их взаиморасположение регламентированы и зависят от диаметра слитка. После шлифования слиток травят в поли-

рующей смеси азотной, плавиковой и уксусной кислот, удаляя нарушенный слой (обычно его толщина составляет 0,2 - 1,0мм).

Разделение слитков на пластины осуществляется чаще всего резкой алмазными кругами (плоскими, кольцеобразными) с внутренней режущей кромкой (для слитков диаметром до 100мм) либо алмазной бесконечной ленточной пилой (для слитков диаметром более 100мм). При резке кремния размер алмазных зерен основной фракции порошка для режущей кромки составляет 40 - 60мкм. Резку слитка почти всегда ведут вдоль определенной кристаллографической плоскости, поэтому перед наклеиванием слитка на оправку на специальном оборудовании оптическими или рентгеновскими методами определяют отклонение кристаллографической плоскости от торца слитка.

Снятие фасок с кромок пластин производят: для удаления сколов на острых кромках, возникающих при резке и шлифовании; для предотвращения возможного образования сколов в процессе проведения операций по формированию структуры ИС. поскольку сколы и острые кромки являются концентраторами напряжений и потенциальными источниками структурных дефектов в пластинах; для предотвращения образования на кромках пластин утолщений слоев технологических материалов (например, фоторезистов), которые после затвердевания нарушают плоскостность поверхностей пластин. В производстве чаще всего используют способ формирования фасок профильным алмазным кругом.

Основным назначением шлифования полупроводниковых пластин является исправление погрешностей их геометрической формы после резки. В зависимости от зернистости используемого абразива, режимов обработки и качества получаемой поверхности пластины различают предварительное (черновое) и окончательное (чистовое) шлифование На практике используют шлифование свободным (шлифовальник и абразив автономны) и связанным (с применением алмазного круга) абразивом

Химическим травлением (обычно двух- или трехкратным для всего технологического цикла изготовления подложек) удаляют нарушенные приповерхностные слои. после чего полируют одну или обе стороны пластин.

Полирование исправляет дефекты геометрической формы пластин, возникающие из-за неравномерности травления. Обычно применяют

механическое полирование с использованием абразивов (порошков алмазов, оксидов хрома, церия и др.). Некоторые сведения об основных операциях получения кремниевых пластин представлены в табл 1

Очистка поверхности полупроводниковых пластин после их изготовления необходима для удаления твердых включений абразивов, органических пленок (масел от машинной обработки, жиров, восков и смол. следы которых остаются после креплений слитков, пластин и при различных их обработках), ионных и атомных загрязнений, остающихся на пластинах от инструментов и материалов технологических сред.

Для получения качественных ИС необходимы однородные пластины с поверхностью, свободной от дефектов и загрязнений. Приповерх-ностные слои пластин не должны иметь нарушений кристаллической структуры. Очень жесткие требования предъявляются к геометрическим характеристикам пластин, особенно к их плоскостности, которая имеет определяющее значение при фотолитографии. Основные параметры пластин кремния, выпускаемых отечественной промышленностью, представлены в табл. 2

Основные ')тапы планарно-эпитаксиальной технологии

Создание структуры кремниевой ИС на биполярных транзисторах с изоляцией элементов обратносмещенными р - ппереходами представляет собой простейший вариант реализации планарно-эпитаксиальной технологии, используемой для производства полупроводниковых ИС малой и средней степени интеграции и реже БИС.

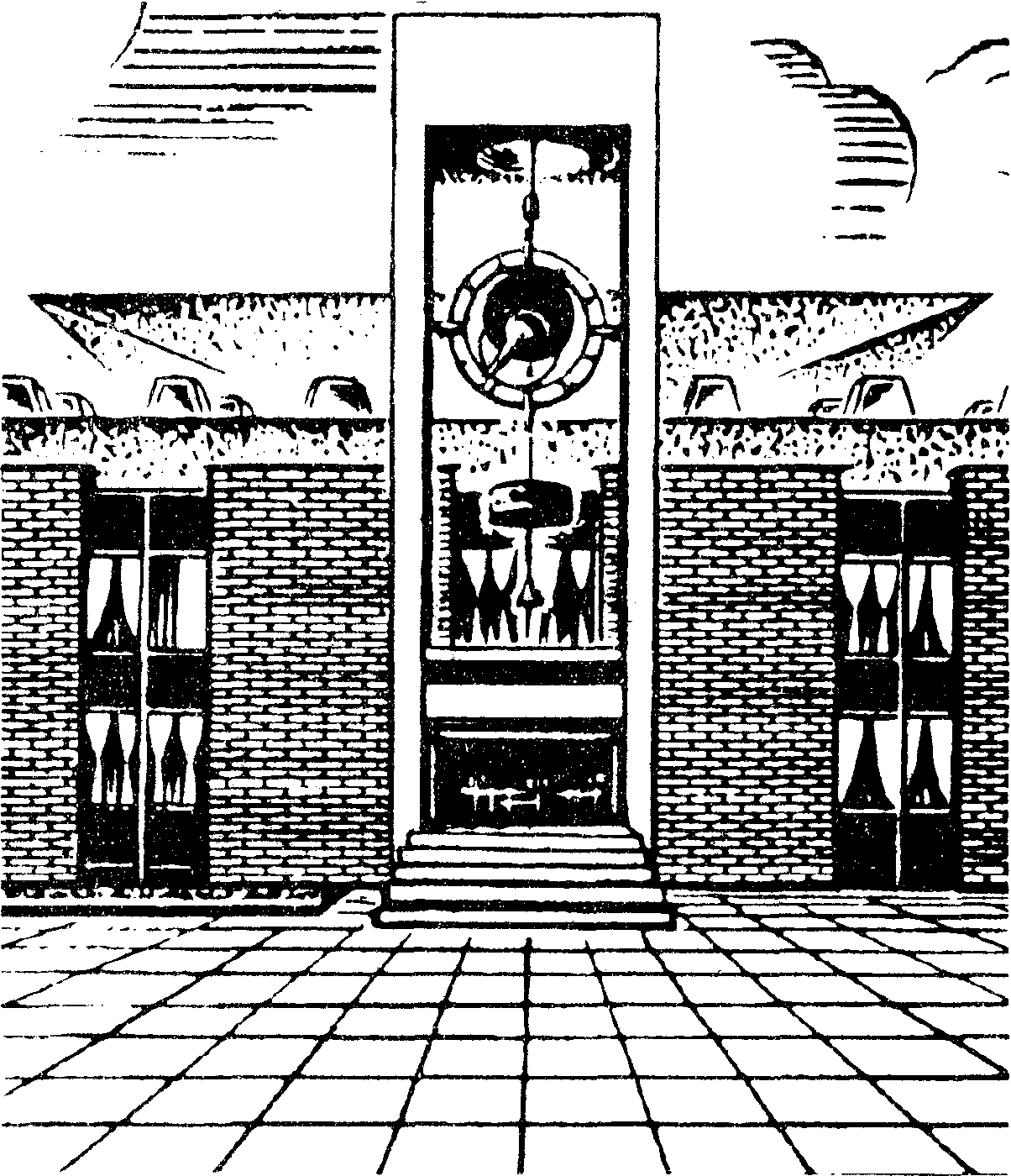

Основные этапы планарно-эпитаксиальной технологии включают следующие технологические процессы: подготовку поверхности пластин кремния к выполнению конкретной операции, окисление пластин, фотолитографию, диффузию примесей в кремний (а для БИС может применяться сочетание диффузии (диффузионного легирования) и ионного легирования кремния), эпитаксиальное наращивание кремния. формирование одного или нескольких слоев металлизации, нанесение диэлектрических покрытий (рис. 1и 2)

Таблица 1