- •Полупроводниковые запоминающие устройства

- •Обозначение микросхем памяти

- •1. Постоянные запоминающие устройства

- •Программируемые постоянные запоминающие устройства

- •Репрограммируемые постоянные запоминающие устройства

- •Программируемые логические матрицы

- •2. Оперативные запоминающие устройства

- •Статические запоминающие устройства

- •Динамические запоминающие устройства

- •3. Микросхемы памяти в составе микропроцессорной системы

- •Увеличение разрядности ячейки памяти (слова)

Программируемые логические матрицы

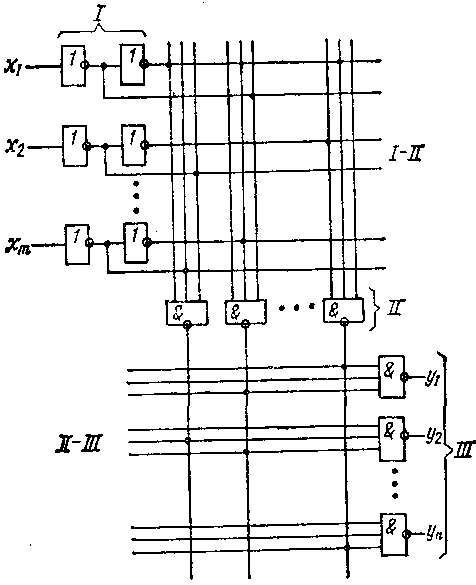

При организации устройств такого типа с одной стороны, сохраняется принцип построения КЦУ, основанный на применении ограниченного числа логических элементов с минимальной избыточностью, с другой стороны, сохраняются преимущества постоянных ЗУ, связанные с регулярной структурой элементов и программируемостью связей между ними для конкретных задач. Это решение реализовано в одной из разновидностей ПЗУ, получивших название программируемых логических матриц (ПЛМ).

О сновой

ПЛМ. являетсянабор

нескольких

уровней логических

элементов заданного базиса.

На

каждом уровне используются однотипные

элементы с одинаковым числом

входов, поэтому создается структура

элементов со многими признаками

регулярности. Между уровнями элементов

вводятся системы (матрицы) горизонтальных

и

вертикальных (линий),

на

пересечении которых при программировании

в нужных местах выполняются электрические

соединения. Это можно делать либо на

этапе изготовления

(как

в

ПЗУ), либо введением плавких перемычек

(как в ППЗУ). На рис. 9 приведен пример

структуры,

иллюстрирующей основные принципы

построения

ПЛМ. Входные элементы, относящиеся к

уровню I,

используются для получения двух разных

значений входных

сигналов и обеспечивают необходимую

нагрузочную

способность. Логические элементы И-НЕ

на уровнях

II

и III

обеспечивают

необходимое преобразование

кодов в соответствии с конкретной

реализацией соединений

в матрицах I—II

и II—III.

Можно

показать, что для каждого выходного

сигнала У обеспечивается преобразование

входных сигналов X

в соответствии с

совершенной

дизъюнктивной нормальной формой (СДНФ).

Если на каждом из

уровней используется достаточное число

логических элементов с соответствующим

числом входов, то

на выходе могут быть реализованы любые

комбинации кодов. ПЛМ находят широкое

применение для построения различных

устройств управления. На их основе

совместно с триггерами, регистрами и

счетчиками

могут быть созданы разнообразные

цифровые автоматы.

сновой

ПЛМ. являетсянабор

нескольких

уровней логических

элементов заданного базиса.

На

каждом уровне используются однотипные

элементы с одинаковым числом

входов, поэтому создается структура

элементов со многими признаками

регулярности. Между уровнями элементов

вводятся системы (матрицы) горизонтальных

и

вертикальных (линий),

на

пересечении которых при программировании

в нужных местах выполняются электрические

соединения. Это можно делать либо на

этапе изготовления

(как

в

ПЗУ), либо введением плавких перемычек

(как в ППЗУ). На рис. 9 приведен пример

структуры,

иллюстрирующей основные принципы

построения

ПЛМ. Входные элементы, относящиеся к

уровню I,

используются для получения двух разных

значений входных

сигналов и обеспечивают необходимую

нагрузочную

способность. Логические элементы И-НЕ

на уровнях

II

и III

обеспечивают

необходимое преобразование

кодов в соответствии с конкретной

реализацией соединений

в матрицах I—II

и II—III.

Можно

показать, что для каждого выходного

сигнала У обеспечивается преобразование

входных сигналов X

в соответствии с

совершенной

дизъюнктивной нормальной формой (СДНФ).

Если на каждом из

уровней используется достаточное число

логических элементов с соответствующим

числом входов, то

на выходе могут быть реализованы любые

комбинации кодов. ПЛМ находят широкое

применение для построения различных

устройств управления. На их основе

совместно с триггерами, регистрами и

счетчиками

могут быть созданы разнообразные

цифровые автоматы.

Рис. 9

2. Оперативные запоминающие устройства

Полупроводниковые ЗУ подразделяются на ЗУ с произвольной выборкой и ЗУ с последовательным доступом. ЗУПВ подразделяются на:

статические оперативные запоминающие устройства (СОЗУ);

динамические оперативные запоминающие устройства (ДОЗУ).

ЗУ с последовательным доступом подразделяются на:

регистры сдвига;

приборы с зарядовой связью (ПЗС).

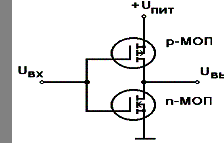

В основе большинства современных ОЗУ лежат комплиментарные МОП ИМС (КМОП), которые отличаются малой потребляемой мощностью. Это достигается применением пары МОП транзисторов с разным типом канала: n-МОП и p-МОП. Как видно на рис. 10, в КМОП инверторе как при низком, так и при высоком уровне сигнала на входе один из транзисторов закрыт. Поэтому потребление энергии происходит только при переключении "1"R"0" (и обратно).

Рис. 10. Схема КМОП инвертора.

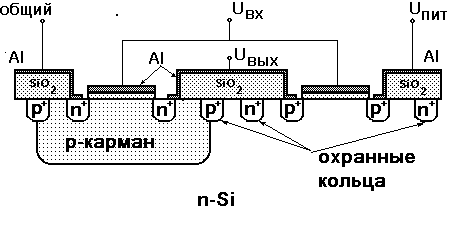

Чтобы реализовать на подложке n-типа не только p-канальный транзистор, но и n-канальный, последний изготавливается в так называемом "кармане", как показано на рис. 11

Рис. 11. Конструкция инвертора на КМОП транзисторах.

Аналогично на четырех МОП транзисторах (2 n-МОП и 2 p-МОП, включенных параллельно и последовательно) можно построить и другие базовые логические элементы "И" и "ИЛИ" и, соответственно, на их основе строятся все другие более сложные логические схемы.

Как известно, быстродействие МОП транзисторов в первую очередь ограничивается большой входной емкостью затвор-исток (подложка). Уменьшение геометрических размеров приборов (площади затвора и длины канала) при увеличении степени интеграции увеличивает граничную частоту.