LR_1-2

.pdf

ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ РЯЗАНСКИЙ ГОСУДАРСТВЕННЫЙРАДИОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

КАФЕДРА ЭВМ

А.В.Кистрин

СХЕМОТЕХНИКА

ЭВМ

Методические указания к лабораторным работам

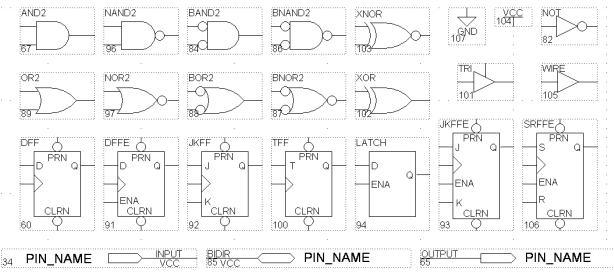

Библиотека prim

Рязань 2011

Работа 1. Исследование комбинационных схем в САПР MaxPlus2

Система автоматизированного проектирования (САПР) MaxPlus2 (Multiple Array Matrix Programmable Logic User) предназначена для проектирования цифровых устройств на современной элементной базе - программируемых логических интегральных схемах (ПЛИС) фирмы Altera. Данная САПР будет использоваться для моделирования цифровых устройств при их изучении.

После запуска программы (файл max2win) открывается окно менеджера

MAX+plus II Manager (рис. 1.1). Пакет MaxPlus2 состоит из 11 интегрированных модулей, предназначенных для выполнения определенных функций. Доступ к любому модулю пакета обеспечивает пункт меню MAX+plus II.

Hierarchy Display - Обзор иерархии - отображает все файлы текущего проекта в виде дерева, позволяет открыть для просмотра и редактирования любой файл, запустив для этого соответствующий программный модуль.

Graphic Editor - Графический редактор - позволяет создавать и редактировать проект в виде схемы.

Symbol Editor - Символьный редактор - позволяет редактировать графическое изображение существующих символов, и создавать новые.

Text Editor - Текстовый редактор - позволяет создавать и редактировать текстовые файлы проекта, используемые другими приложениями MAX+PLUS II. Он позволяет вводить проекты в виде описания на языках Verilog, VHDL, AHDL.

Waveform Editor - Сигнальный редактор, предназначен для создания временных диаграмм тестовых входных сигналов и для просмотра результатов моделирования устройств. Разработанные диаграммы (входные векторы) сохраняются в файле с расширением .scf (Simulator Cannel File). Кроме того, он позволяет вводить исходные данные для проектирования функционального модуля в виде временных диаграмм в файле с расширением .wdf (Waveform Design File).

Floorplan Editor - Поуровневый планировщик, редактор разводки кристалла ПЛИС. Compiler - Компилятор - обрабатывает логические проекты.

Simulator - Симулятор – программа для моделирование проекта (). Timing Analyzer - Анализатор временных параметров сигналов в схеме.

Programmer Программатор - позволяет программировать ПЛИС фирмы Altera. Message Processor Генератор предупреждающих сообщений о состоянии проекта.

Разрабатываемое в САПР устройство называют «проект». Каждому проекту соответствует несколько файлов с одинаковыми именами и различными расширениями.

Ввод данных проекта можно выполнить одним из трех способов.

1)В виде схемы посредством графического редактора Graphic Editor. Файл проекта в этом случае имеет расширение *.gdf (Graphic Design File).

2)В виде текстового описания на одном из HDL языков. Файл описания на языке Altera HDL имеет расширение *.tdf (Text Design File), а на языке Verilog - *.v.

3)В виде заданных временных диаграмм, создаваемых в редакторе Waveform Editor в виде файла с расширением *.wdf (Waveformt Design File).

Задание 1.1. Базовые логические элементы. Для ознакомления с САПР рассмотрим процесс выполнения проекта простейшего устройства, содержащего 4-входовые базовые логические элементы, на входы которых поступают одинаковые сигналы. Требуется промоделировать выходные сигналы ка-

ждого элемента. Выполним ввод проекта, моделирование, анализ результатов.

Для начала работы в САПР MaxPlus2 необходимо выполнить следующие действия.

1)Создать каталог для хранения проектов.

2)Запустить MaxPlus2, Командой File / New создать новый файл, для которого выбрать тип - графический, и расширение .gdf (Рис. 1.2). В результате будет запущен графический редактор и создан файл без име-

ни (Untitled_1.gdf).

3)Записать файл в созданный каталог командой File/Save As с

Рис. 1.2. Типы файлов указанием имени. Выбранное имя будут иметь все файлы проекта для исследуемого устройства, и символ, созданный впоследствии. Для при-

2

мера выберем имя «log_el.gdf».

3)Указать текущий файл, как ведущий файл проекта, с которым предполагается далее работать,

командой: «File/Project/Set Project To Current File».

4)В качестве примера ввести схему (Рис. 1.5) в графическом редакторе.

5)Запустить компилятор « MAX+plus II/ Compiler», выбрать из меню Processing тип моделирования - функциональное (или временное), нажать кнопку «Start» и завершить компиляцию.

6)Создать символ для разработанной схемы командой: «File/Create Default Symbol». Имя символа назначается автоматически по имени файла проекта.

Команды «File/Open» и «Set Project To Current File» позволяют запускать ранее созданные проекты для продолжения работы.

При запуске существующего проекта командой «File/Open» открывается окно для выбора типа открываемого файла, его расширения и имени. Файл будет открыт в окне программного модуля, использованного при создании указанного файла. Для продолжения работы открытый файл необходимо ука-

зать как ведущий командой «File/Project/Set Project To Current File».

Ввод схемы в графическом редакторе. Процесс ввода схемы в графическом редакторе содержит ввод символов элементов и их соединение. Символы элементов содержатся в библиотеках. В окне «Enter Symbol» (рис. 1.3) показаны доступные библиотеки «Symbol Libraries» и символы пользователя «Symbol Files».

Окно «Enter Symbol» открывается из меню: «Symbol / Enter Symbol», либо двойным щелчком левой кнопки на свободном месте схемы.

|

1) Библиотека примитивов (..\prim) содержит, простейшие базовые |

|

элементы цифровых устройств, символы портов ввода / вывода, шин пи- |

|

тания и земли (приведены на титульном листе). |

|

2) Библиотека макрофункций (..\mf), содержит элементы средней |

|

степени интеграции. |

|

3) Библиотека параметризированных модулей (..\lpm), содержащая |

|

функциональные блоки большой степени интеграции с возможностью из- |

|

менения параметров по желанию пользователя. |

|

4) Библиотека моделей логических элементов старого типа - ТТЛ |

Рис. 1.3. Библиотеки САПР |

(..\edif). Описание всех элементов приведено в Help. |

Для ввода символа необходимо двойным щелчком выбрать биб- |

|

|

лиотеку. Затем выбрать символ в библиотеке, или ввести имя символа в |

строке Symbol Name и нажать ОК. Можно ввести символ ранее созданного модуля из окна Symbol Files. Соединение элементов схемы выполняются посредством инструментов панели рисования (Рис.

1.4). Назначение кнопки, выбранной указателем, отображается в строке состояния в нижней части экра-

на. |

1 - выбор объекта (элемента, или фрагмента схемы) для его перемещения и копиро- |

|

1 |

||

вания. Это основной режим при вводе и редактировании схем. Переход в этот режим из |

||

2 |

||

любого другого выполняет клавиша Ecs. В этом режиме можно выделять символы, про- |

||

3 |

||

водники или фрагменты схемы при нажатой левой кнопке манипулятора, а затем переме- |

||

4 |

||

щать, удалять (Del), копировать (Ctrl-C) и вставлять (Ctrl-V) выделенные элементы. Пере- |

||

5 |

||

мещение элемента схемы может осуществляться как при включенном, так и при выклю- |

||

6 |

||

ченном режиме обеспечения неразрывности цепей, связывающих символы (кнопки 11 и |

||

7 |

||

12). Правая кнопка мыши открывает контекстное меню функций, доступных для выделен- |

||

8 |

||

ного элемента. 2 - ввод поясняющего текста. 3 - ввод ортогональных линий (проводников |

||

9 |

||

и шин). Проводники изображаются тонкой непрерывной линией, а шины - широкой лини- |

||

10 |

||

ей. Тип линии выбирают из списка на панели инструментов. 4 - ввод линий с произволь- |

||

11 |

||

12 |

ным углом. 5 - ввод дуг. 6 - ввод окружностей. 7-8 – изменение масштаба изображения. 9- |

|

отображение всего листа схемы. |

||

Рис.1.4. |

10 - Установка, или удаление точки соединения пересекающихся проводников, что |

|

Панель |

изменяет статус точки пересечения цепей на противоположный. |

|

рисования |

11-12 - Rubberbanding - «резиновые проводники» - включение или выключение ре- |

|

|

жима, обеспечивающего неразрывность цепей (шин) при перемещениях элементов. Режим, |

3

включаемый кнопкой 12, позволяет «разобрать» схему на отдельные элементы, из которых можно построить новый вариант.

Копирование элемента схемы, кроме «Ctrl-C» и «Ctrl-V», можно также осуществить следующим образом. Необходимо поместить курсор на тело элемента и нажать левую кнопку манипулятора, выбранный элемент будет иметь красный контур. Не отпуская левую кнопку, нажать на клавиатуре клавишу Ctrl, при этом около выбранного элемента появится символ «+». Не отпуская нажатые клавиши, переместить копию элемента в нужную зону схемы, Отпустить нажатые клавиши. Данный способ удобен при вводе терминалов ввода – вывода.

Графический редактор позволяет осуществлять два способа соединения элементов.

1)Физическое соединение цепей посредством проводников, или шины.

2)Логическое соединение - присваиванием одинаковых имен.

Для физического соединения выводов символов проводником, или шиной, необходимо подвести курсор к выводу символа, нажать левую кнопку манипулятора и, удерживая ее, провести линию до другого, соединяемого вывода. Курсор в этом случае принимает вид крестика.

Для ввода имени необходимо выбрать цепь (проводник, или шину), поместить курсор на тело цепи и щелкнуть левой кнопкой манипулятора. Выбранная цепь будет иметь красный контур, а курсор примет вид мигающего черного квадратика, что является приглашением к вводу текста. С клавиатуры ввести имя цепи и нажать клавишу Enter. Имя нельзя присвоить выводу элемента, к которому не подключена никакая цепь. Проводники с одинаковыми именами будут считаться соединенными.

Входные и выходные сигналы подключаются к схеме через терминалы Input и Output, которые должны иметь уникальные имена. Любая схема обязательно должна содержать хотя бы один терминал

Input и хотя бы один Output, задающие вход и выход схемы. Для ввода имени необходимо поместить курсор на текст «PIN_NAME», выбрать эту зону двойным щелчком левой кнопки манипулятора, ввести с клавиатуры имя вывода (старое имя будет автоматически стерто), нажать клавишу Enter на клавиатуре. Если существует другой примитив типа Input или Output, расположенный ниже данного примитива, курсор автоматически установится для ввода соответствующего имени.

Для редактирования имени цепи, или порта необходимо поместить курсор в зону редактируемого имени и двойным щелчком левой кнопки манипулятора выбрать эту зону. Используя клавиши перемещения курсора на клавиатуре, подвести курсор к редактируемому символу, ввести новое имя, нажать клавишу Enter.

При вводе заданной схемы выясняется, что 4-входовой элемент XOR в библиотеке prim отсутствует, требуемая операция реализована на 2-входовых элементах (Рис. 1.5.).

Входной терминал « d[3..0] » является параллельным портом, или разъемом для подключения шины. В квадратных скобках через две точки указан диапазон индексов, на первом месте - индекс старшего разряда. Проводник старшего разряда будет иметь имя « d3 », а младшего - « d0 ». Проводники терминала подключены к входам всех логических элементов параллельно посредством логического соединения (одинаковых имен).

После ввода схемы необходимо выполнить компиляцию, выбирая из меню MAX+plus II/ Compiler. Затем (не нажимая кнопку «Start»), из меню Processing необходимо выбрать тип моделирования (функциональное, или временное). Кнопка «Start» и завершает компиляцию.

После удачной компиляции схему можно представить в виде символа командой File/Create Default Symbol, что позволит использовать данную схему как модуль в иерархической структуре.

4

Моделирование в сигнальном редакторе. Для моделирования введенной схемы необходимо: 1) запустить сигнальный редактор командой: « MAX+plus II / Waveform Editor»;

12) сохранить открывшийся файл с именем проекта командой «Save As»;

23) создать входные тестовые сигналы;

34) запустить имитатор командой: « MAX+plus II / Simulator».

Поясним выполнение указанных действий.

После запуска сигнального редактора открывается безымянный файл. Его необходимо сохранить командой Save As с именем проекта и расширением .scf. Для данной работы

4имя файла должно быть log_el.scf.

5В левой части окна сигнального редактора (рис. 1.7) расположена панель инструмен-

6тов редактирования временных диаграмм (рис. 1.6). Рассмотрим назначение кнопок.

71 -выбор временной диаграммы, или ее части для перемещения, копирования, или

8удаления. Переход в этот режим выполняет клавиша Esc. 2 – ввод поясняющего текста.

93 – создание и редактирование временной диаграммы, путем перемещения фронтов

10импульсов курсором манипулятора при нажатой левой кнопке. Установка указателя на на-

11чало временной диаграммы и перемещение его вправо при нажатой левой кнопке, добавля-

12ет к временной диаграмме интервал с инверсным значением логического сигнала.

134,5 –масштаб временных диаграмм. 6 – просмотр диаграмм во весь экран.

147 - 10 – установка статических уровней для выделенной части временной диаграммы

15(0,1,Х,Z). 11 – инвертирование выделенного сигнала.

Рис1.6. |

12 – подключение синхросигнала к выделенной диаграмме, или ее части. 13 – под- |

|

ключение прямоугольных импульсов. 14 – подача кода на шину. 15 ввод имени состояний |

||

Панель |

||

сигнала для цифрового автомата. |

||

редакти- |

||

Для выбора и ввода контрольных точек необходимо установить курсор в столбце |

||

рования |

||

«Name» (рис. 1.7) временных диаграмм, нажать правую кнопку манипулятора, в открыв- |

||

сигналов |

||

шемся меню выбрать «Enter Nodes from SNF». В следующем окне следует нажать кнопку |

||

|

«List». Из списка всех доступных (Available) узлов исследуемой схемы, перечисленных в |

левом списке, следует выбрать требуемые узлы, переслать их в список выделенных узлов, который расположен справа, и нажать кнопку ОК. В простейшем случае можно переслать все узлы из левого списка в правый.

Важным моментом при моделировании является создание тестовых сигналов, позволяющих выполнить полную проверку правильности функционирования устройства. Этот выбор предполагает по-

|

лучение определенного результата, основанного на |

|

|

знании работы устройства. |

|

|

При моделировании данной схемы необходимо |

|

|

получить подтверждение того, что выходные сигналы |

|

|

различных логических элементов принимает соответ- |

|

|

ствующие значения при определенных сигналах d0, |

|

|

d1, d2, d3. Формирование сигналов на входах d3..d0 |

|

|

проще всего достигается путем объединения этих сиг- |

|

|

налов в шину «d», и подключения к шине выходного |

|

|

кода двоичного счетчика. За полный цикл счетчика |

|

|

происходит перебор всех возможных комбинаций |

|

|

двоичных кодов. |

|

Рис. 1.7. Результат моделирования схемы |

Для формирования временных диаграмм для |

|

входных сигналов необходимо щелчком левой кнопки |

||

|

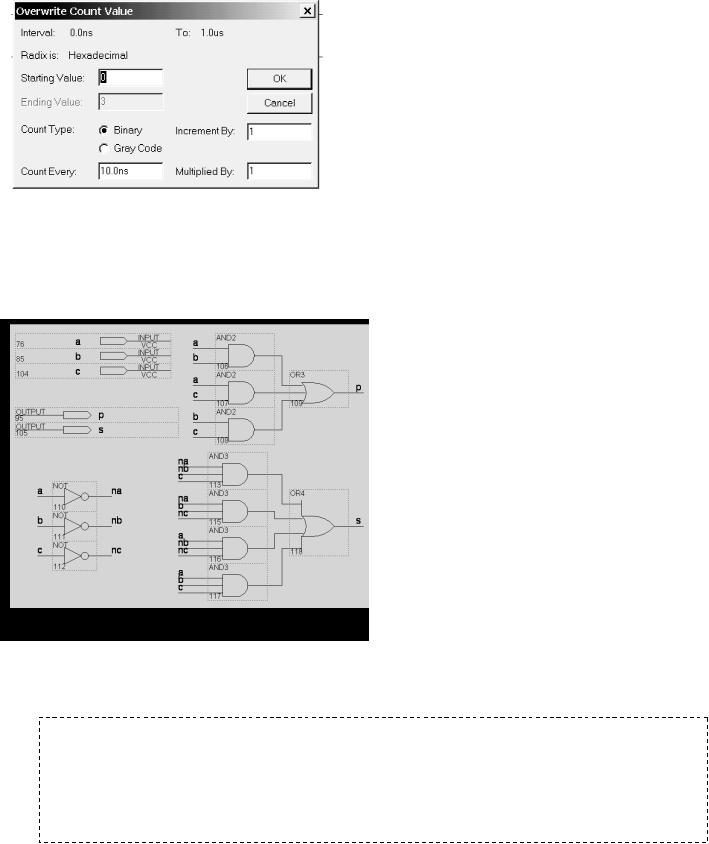

выделить шину, установив курсор на терминал шины. Сигнал в форме прямоугольных импульсов выбирается кнопкой 13, а параметры импульсов устанавливаются в окне «Overwrite Count Value» (рис. 1.8), где можно задать: начальное значение логического сигнала - Starting Value; конечное значение - Ending Value; приращение кода для шины - Increment By, а также масштабный множитель Multiplied By. Если в схеме несколько шин, то для первой из них можно выбрать параметры по умолчанию, а для других выбрать больший масштабный множитель.

Параметр «Interval», по умолчанию равный 1 мкс, определяет длительность моделирования. Его можно изменять, выбирая пункт меню File/End Time. Параметр «Count Every» определяет период тактовых импульсов счетчика, формирующего прямоугольные импульсы, и может быть скорректирован в

5

данном окне, либо выбором из меню Options/Grid Size. Тактовые импульсы определяют шаг сетки (Grid) на временных диаграммах. Фронты импульсов можно привязать (Snap) к сетке.

Для изменения формы сигналов необходимо вначале выделить временную диаграмму, или ее часть. Диаграмма выделяется щелчком левой кнопки на символе сигнала в столбце «Name», а часть диаграммы - перемещением курсора в области изображения графиков при нажатой левой кнопке. Изменение вида диаграммы выполняется при нажатой кнопке 3.

При выделении шины курсором становятся активными кнопки 12, 13, позволяющие задать код на шине - постоянный, или изменяющийся линейно. Двойной щелчок по символу терминала открывает окно для выбора системы счисления, в которой отображаются коды на шине. Правая кнопка открывает для выделенной шины

Рис. 1.8. Окно параметров импульсов контекстное меню, позволяющее отобразить сигналы на шине в виде диаграмм для отдельных проводников

(функция Ungroup), либо в виде кодов (выделить провод-

ники шины и выбрать функцию Enter Group).

Расположение временных диаграмм в окне сигнального редактора (Рис. 1.8) можно изменять, устанавливая указатель курсора на символ порта, и перемещая его при нажатой левой кнопке.

Последний этап моделирования – запуск имитатора из меню MAX+plus II/simulator, или кнопкой на панели инструментов. В результате моделирования появятся временные диаграммы для выходных сигналов, соответствующие заданным входным сигналам.

Анализ результатов моделирования. 1. Очевидные правила определения значе-

ний выходного сигнала логических элементов: схема «И» формирует на выходе сигнал «1», если на все входы подан сигнал «1»; схема «ИЛИ» формирует сигнал «0», если на все входы подан сигнал «0»;

схема «Сумма по модулю 2» формирует сигнал «1», если сумма сигналов, равных «1» нечетна.

2. Для того, чтобы один из входов элемента

(например, d0) был активным, и передавал измене- Рис. 1.9. Схема сумматора ния сигнала на выход, на остальные входы необхо-

димо подать: для элемента «И» - «1»; для элемента «ИЛИ» - «0»; для элемента «Сумма по модулю 2» - любое значение.

3. Элементы «И» и «ИЛИ» можно использовать в схемах стробирования сигналов, а элемент «Сумма по модулю 2» в качестве управляемого инвертора.

Для всех заданий отчет должен содержать описание всех этапов синтеза и моделирования.

1.Постановка задачи, функциональное назначение устройства, входные и выходные сигналы

2.Таблица истинности, логические уравнения, минимизация уравнений.

3.Схема устройства в графическом редакторе (или текст описания на языке Verilog).

4.Разработка и описание тестовых сигналов.

5.Описание работы устройства, анализ результатов моделирования.

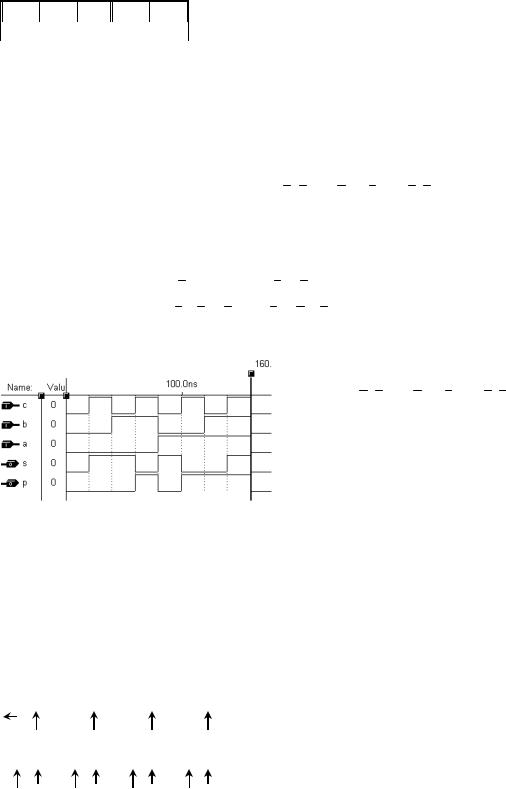

Задание 1.2. Оодноразрядный комбинационный сумматор. Рассмотрим синтез схемы, созда-

ние проекта, исследование работы, анализ результатов.

1. Постановка задачи, функциональное назначение устройства, входные и выходные сигналы. Одноразрядный сумматор выполняет арифметическое суммирование кодов чисел. В каждом разряде производится суммирование трех цифр:: первого и второго слагаемых данного разряда (a) и (b), и

6

переноса из соседнего младшего разряда (c). Выходами схемы являются сумма для данного разряда(s) и перенос в следующий разряд (p). Включая параллельно несколько подобных схем можно получить сумматор с произвольным числом разрядов (с последовательным переносом).

2. Таблица истинности, логические уравнения, минимизация. При составлении таблицы истинности учитываем, что все слагаемые равно-

a |

b |

c |

p |

s |

значны. Значения переноса и суммы образуют двухразрядное двоичное |

||||||

0 |

0 |

0 |

0 |

0 |

число, равное количеству единиц во входных сигналах. |

||||||

0 |

0 |

1 |

0 |

1 |

Логическое уравнение в совершенной дизъюнктивной нормальной |

||||||

0 |

1 |

0 |

0 |

1 |

форме (СДНФ) содержит дизъюнкцию конституент единицы, представ- |

||||||

0 |

1 |

1 |

1 |

0 |

ляющих собой элементарные произведения (конъюнкцию) всех аргумен- |

||||||

1 |

0 |

0 |

0 |

1 |

тов, взятых с инверсиями или без, и равных единице только на одном на- |

||||||

1 |

0 |

1 |

1 |

0 |

боре аргументов. Инверсия ставится над аргументом, равным нулю на |

||||||

1 |

1 |

0 |

1 |

0 |

данном наборе. |

||||||

1 |

1 |

1 |

1 |

1 |

p |

|

b c a |

|

c a b |

|

a b c; |

a |

b |

c |

|||||||||

s a b c a b c a b c a b c

Уравнение в совершенной конъюнктивной нормальной форме (СКНФ) содержит конъюнкцию конституент нуля, представляющих собой дизъюнкцию всех аргументов, взятых с инверсиями или без, и равных нулю только на одном наборе аргументов, над аргументом, равным на данном наборе единице, ставится инверсия.

p (a b c) (a b c) (a b c) (a b c);

s (a b c) (a b c) (a b c) (a b c)

В результате минимизации для данного примера получим минимальную дизъюнктивную нормальную форму (МДНФ):

p a b a c b c;

s a b c a b c a b c a b c

Заметим, что уравнение, записанное в МКНФ несложно получить из уравнения в МДНФ.

3. Схема устройства строится по минимизированным логическим уравнениям. В соответствии с постановкой задачи схема содержит три входных и два выходных терминала (a,b,c,p,s). Для формирования выходного сигнала «s» необхо-

Рис. 1. 10. Моделирование сумматора димы инверсные значения входных сигналов, для их формирования используются инверторы (элементы NOT). В схеме использовано логическое соединение проводников. Проводники, имеющие одинаковые имена, соедине-

ны (Рис. 1.9). После удачной компиляции создайте символ.

4.Разработка тестовых сигналов. Входные сигналы сумматора - слагаемые - равнозначны. Для полного тестирования устройства необходимо выполнить перебор всех возможных комбинаций сигналов. Для этого на входы необходимо подать импульсы «Clk» с различными значениями множителя

«Multiplied By», например, 1, 2, 4 (Рис. 1. 10).

5.Анализ результатов. Формирование выходных сигналов соответствует таблице истинности.

co |

q3 |

|

|

|

|

q2 |

|

|

|

|

q1 |

|

|

|

q0 |

|

Задание 1.3. Полусумматор - устройство для суммирования |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

двух одноразрядных двоичных чисел a и b и формирования суммы s |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

и переноса в следующий разряд p, в соответствии с уравнениями: |

|||||

|

p |

q |

|

|

p |

q |

|

|

p |

q |

|

|

p |

q |

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

p a b; |

s a b a b a b; |

|||||||||||||||||||||||||||

|

a |

b |

|

|

a |

b |

|

|

a |

b |

|

|

a |

b |

|

||||||||||||||

|

|

|

|

|

|

|

|

Выполните синтез схемы, создание проекта и символа, ис- |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

d3 |

|

|

|

|

d2 |

|

|

|

|

d1 |

|

|

|

|

d0 |

|

|

ci |

следование работы, анализ результатов. |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Задание 1.4. Инкрементор - выполняет прибавление едини- |

|||||

Рис. 1.11. Инкрементор |

цы к входному коду (Рис. 1.11). Для каждого разряда входного кода |

|

используется полусумматор. Входами инкрементора являются 4-разрядный код «d[3..0]», к которому прибавляется сигнал «ci»(Carry In). При ci = 0 инкремента нет. Выходной код обозначен «q[3..0]», выходной перенос – «co». Бит выходного переноса «co» и 4-разрядный выходной код «q» образуют 5- разрядное число.

Выполните синтез схемы, создание проекта и символа, исследование работы, анализ результатов.

7

Задание 1.5. Создайте проект 4-разрядного сумматора, используя символы одноразрядного сумматора, созданного в задании 1.2. Входной 4-разрядный код обозначте«d[3..0]», входной перенос - «ci», выходной код - «q[3..0]», выходной перенос – «co». Бит выходного переноса «co» и 4-разрядный выходной код «q» образуют 5-разрядное число. Создайте символ.

Здание 1.6. Составьте схему формирователя признаков данных, представленных в виде 1 байта: признак нуля z = 1, если все разряды данных равны нулю; признак знака числа s = 1, если число отрицательное; признак четности p = 1, если сумма бит в двоичной записи числа четна. Создайте символ. В отчете приведите таблицы истинности, логические уравнения, схемы, анализ результатов моделирования.

Задание 1.7. Проведите синтез и моделирование 5–входовой комбинационной схемы, сигнал на выходе которой равен «1» при значениях входного кода, приведенных в таблице (в 16-ричной системе).

Бригада |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

Коды |

00 |

01 |

02 |

03 |

04 |

05 |

06 |

07 |

08 |

05 |

01 |

02 |

|

09 |

08 |

0B |

0C |

0D |

0E |

0A |

0C |

0C |

0А |

0В |

0F |

|

0B |

15 |

16 |

17 |

18 |

19 |

0F |

10 |

11 |

12 |

13 |

10 |

|

14 |

0A |

1E |

1A |

1D |

1F |

1A |

1B |

1C |

1D |

1E |

18 |

Задание 1.8. Разработайте комбинационную схему, формирующую на выходе признак х=1 в случае, когда входной код, 1 тетрада, принадлежит заданному диапазону. В таблице указаны нижняя и верхняя границы диапазона. В отчете приведите таблицу истинности, логическое уравнение, схему, фрагмент временной диаграммы.

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

5 |

1 |

2 |

9 |

8 |

0B |

0C |

0D |

0E |

0A |

0C |

0C |

0А |

0В |

8 |

|

|

|

|

|

|

|

|

|

|

|

|

Контрольные вопросы

1.Перечислите функциональные возможности, укажите назначение кнопок панели инструментов менеджера проектов, графического редактора, сигнального редактора системы MAX+PLUS.

2.Укажите назначение кнопок панели рисования графического редактора, сигнального редактора.

3.Как выполняется ввод и редактирование цепей, примитивов Input и Output, элементов схемы.

4.Каким образом создаются тестовые сигналы и файл временных диаграмм.

5.Из каких этапов состоит синтез комбинационных схем.

6.Опишите порядок выполнения проекта в системе MAX+PLUS II.

7.Сумматор. Функциональное назначение, область применения, назначение выводов, схема.

8.Полусумматор. Функциональное назначение, область применения, назначение выводов, схема.

9.Инкрементор. Функциональное назначение, область применения, назначение выводов, схема.

10.Какие функции выполняют команды «File/Open» и «Set Project To Current File»?

11.Создайте проект по заданию преподавателя.

12.По материалам работы составьте тестовую задачу, не похожую на задачи соседних бригад.

Работа 2. Описание комбинационных схем на языке Verilog

Специфика языков описания аппаратуры - HDL (Hardware Description Language) состоит в отображении процессов, протекающих в реальной электронной схеме параллельно и непрерывно. Рассмотрим основные средства языка Verilog, принадлежащие к подмножеству, поддерживаемому системой проектирования MaxPlus 2.

Алфавит языка — набор символов для построения конструкций языка, воспринимаемых компилятором — содержит: латинские буквы (регистр имеет значение !); цифры и специальные символы.

Идентификатор должен начинаться с буквы, или символа подчеркивания, может содержать цифры, знаки подчеркивания и доллара. Допускаются идентификаторы расширенного типа (escaped), они начинаются с символа «\» и заканчивающиеся пробелом. В качестве идентификатора нельзя использовать ключевые слова и обозначения элементов языка Verilog (см. Help).

Комментарий - строка, начинающаяся с двух символов косая черта «//». Фрагмент в скобках /* */ - также комментарий, его используют при отладке для «закомментирования» - временного

исключения фрагментов программы из компиляции.

8

Запись констант содержит: число (это количество разрядов), одинарную кавычку, основание системы счисления (буква b, o, d, h для 2-, 8-, 10-, 16-ричной систем счисления) и цифры в указанной системе. Число без указания разрядности и системы счисления принимается как десятичное. Отрицательные числа задаются знаком «минус» перед разрядностью числа в самом начале записи.

Сигналы в схеме бывают двух типов - цепи (wire) и регистры (reg), разрядность по умолчанию - 1 бит. Сигналы могут принимать одно из четырех значений: 0, 1, z, х. Значение «z» означает, что источник сигнала отключен, а «х» - что выход не определен, и может принимать любое значение 0 или 1.

Цепь wire моделирует провод, к которому непрерывно прилагается воздействие от источника сигнала, называемого драйвер (driver). Все сигналы описываемых устройств по умолчанию устанавливаются типа «wire». Все входные сигналы устройств должны иметь тип «wire».

Регистр reg способен хранить присвоенное значение, это элемент памяти, подобен переменной в программировании. Тип «reg» указывают для выходных сигналов схем с элементами памяти.

Вектор (шина) описывается указанием диапазона (Range). В квадратных скобках через двоеточие указывают индексы в убывающем порядке, первый индекс соответствует старшему разряду вектора. По умолчанию вектор - беззнаковое скалярное (scalared) целое, в котором по умолчанию разрешен доступ к отдельным битам. Для запрещения доступа к битам необходимо записать «vectored». Если перед указанием диапазона записать «signed», то будем иметь число в дополнительном коде со знаком.

Операторы в языке Verilog существуют двух типов: параллельные и последовательные. Разделитель всех операторов – точка с запятой. Символы пробела, табуляции, возврата каретки транслятор игнорирует, если они не нарушают целостность ключевых слов. Операторы бывают с одним, двумя и тремя операндами. В унарных операторах символ операции записывают слева от операнда, а в бинарных и в тернарном – между операндами.

Параллельные операторы используют для описания комбинационных схем без элементов памяти, Они выполняют непрерывное присваивание. Изменение выходного сигнала происходит при

И& изменении любого из входных сигналов. Выходные сигналы имеют

тип «wire».

Запись параллельного оператора начинаются с ключевого слова «assign» (назначить), затем записывается имя выходного сигнала, знак равенства, а затем непосредственно операторы, формирующие выходной сигнал (арифметические, логические, или условного назначения).

Арифметические операторы – бинарные, перечислены в по-

рядке убывания приоритета. Порядок операций можно изменить, используя круглые скобки.

Операторы отношения и сравнения сравнивают два опе-

ранда и выдают значение в виде однобитовой логической переменной, которая обычно используется в условных операторах и при поведенческом описании. При выполнении условия выдается «1». Если

хотя бы один операнд не определен, то и результат примет неопределенное значение «х». В случае неодинаковой разрядности операндов, более короткий из них дополняется слева нулями.

Логические преобразования сигнала в языке Verilog выполняют три типа операторов с названиями: поразрядные, свертки, логические.

Поразрядные операторы – бинарные, содержат два операнда. Сигналы могут быть векторами, тогда логическая операция выполняется поразрядно. Векторы могут иметь различную разрядность, если разрядность одного операнда меньше, чем другого, то недостающие разряды заполняются нулями.

Операторы свертки, называют также операторами приведения. Это унарные операторы, использующие те же символы, что и поразрядные операторы (кроме оператора инверсии «~»). Они выполняются над единственным, многоразрядным операндом побитно, шаг за шагом, формируя на выходе

9

одноразрядный результат. Этот тип операторов позволяет формировать признаки данных. Так, например, для многоразрядного вектора d, признак p1 = &d будет равен единице, если все биты вектора равны единице, признак p2 = |d будет равен нулю, если все биты вектора равны нулю, а p3 = ^d примет значение «1», если количество единиц в векторе d нечетно.

Третий тип называют именно «логические операторы» Это бинарные операторы И, ИЛИ, а также унарный оператор НЕ. Результат операции – однобитная переменная, равная нулю, если результат операции есть ноль. Эти операции используют для формирования условий в условных переходах.

Оператор объединения, позволяет из исходных векторов сформировать вектор суммарной разрядности. Исходные векторы записываются в фигурных скобках через запятую. Объединенный вектор будет иметь суммарную разрядность, он может быть записан справа и слева от знака равенства в операторе присваивания.

Оператор непрерывного условного присваивания имеет форму записи: «assign q = s ? a : b»,

читается так: if s is true then q = a , else q = b. В качестве условия «s» в данном операторе может использоваться выражение, формирующее одноразрядный логический сигнал «1» или «0», а вместо переменных «а» и «b» могут быть операторы, в том числе и условный оператор, заключенные в скобки.

assign |

Переменная |

= |

Условие |

? |

Ветвь ДА |

: |

Ветвь НЕТ |

; |

Последовательное, или процедурное присваивание используется для описания схем с элемен-

тами памяти, формирует выходной сигнал типа «reg», что необходимо указывать в описаниях сигналов. Оператор содержит ключевое слово «always», символ @, список чувствительности в круглых скобках, и блок «begin - end», или оператор, вычисляющий значение сигнала. Ключевое слово «always» (всегда) – обозначает повторение присваивания при возникновении события. Символ @ эквивалентен понятию «событие». Список чувствительности – это перечисление через запятую, или знак дизъюнкции, всех сигналов, изменение которых вызывает повторение процесса присваивания. Если список чувствительности содержит все переменные, используемые в операторе, то оператор может содержать только слово «always». Последовательное присваивание «always» обеспечивают широкие возможности описания, так как кроме рассмотренных арифметических и логических операций допускается применение блоков «be- gin-end», в которых могут использоваться последовательные операторы условного перехода «if» и ва-

рианта «case».

В списке чувствительности можно указать срабатывание по фронту, или спаду сигнала. Фронт сигнала обозначается «posedge», спад - «negedge», от слов «positive», «negative», и «edge» - край.

Блокирующее (blocking) последовательное присваивание обозначатся символом «=», запрещает исполнение других присваиваний до своего завершения. Неблокирующее процедурное присваивание (unblocking procedural) обозначается символами «=>» разрешает выполнение других присваиваний до своего выполнения, используется для описания регистровых структур с обратными связями.

Оператор условного перехода «if» относится к последовательным операторам, используется совместно с ключевым словом «always». Условие - переменная, или выражение, записывается в круглых скобках. При записи условия равенства в операции сравнения следует использовать два знака равенства «==». Ветвь ДА, выполняется, если условие истинно, и в результате его вычисления получено некоторое число (например, 1). Ветвь НЕТ, выполняется, если результат вычисления условия равен 0, или содержит значения x, z. Заметим, в записи оператора слово «then» отсутствует.

always |

if |

( |

Условие |

) |

Ветвь ДА |

; |

else |

Ветвь НЕТ |

; |

Оператор варианта «case» относятся к последовательным операторам, используется совместно с присваиванием «always», и позволяют выбрать один из возможных путей исполнения алгоритма в зависимости от значения селектора.

Переменная, которой присваивается значения, должна быть определена как регистр.

always |

case |

( |

Селектор |

) |

1 |

вариант селектора |

: |

Первое присваивание |

; |

|

|

|

|

|

2 |

вариант селектора |

: |

Второе присваивание |

; |

|

|

|

|

|

|

default |

: |

Присваивание по умолчанию |

; |

|

endcase |

|

|

|

|

|

|

||

Модуль описания на языке Verilog содержит элементы: заголовок, описание портов, описание устройства, завершение. Описание устройства может быть структурным, в виде набора модулей, или поведенческим.

10