- •Компьютерная Схемотехника

- •Компьютерная Схемотехника

- •ДВОИЧНЫЕ СЧЕТЧИКИ И СЧЕТЧИКИ НА ИХ ОСНОВЕ

- •ВЫЧИТАЮЩИЙ ДВОИЧНЫЙ СЧЕТЧИК

- •На рис. приведен фрагмент РЕВЕРСИВНОГО СЧЕТЧИ-КА. Этот счетчик может работать как суммирующий при

- •Общим недостатком всех счетчиков с последовательным переносом (в литературе встречается также название «асинхронные

- •СЧЕТЧИКИ С ПРОИЗВОЛЬНЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

- •Кодовые комбинации счетчика на 14

- •После записи в триггер Т5 «нуля» устанавливаются в «0» все триггеры счетчика (Т1..Т4)

- •Значения прямых выход. триг.

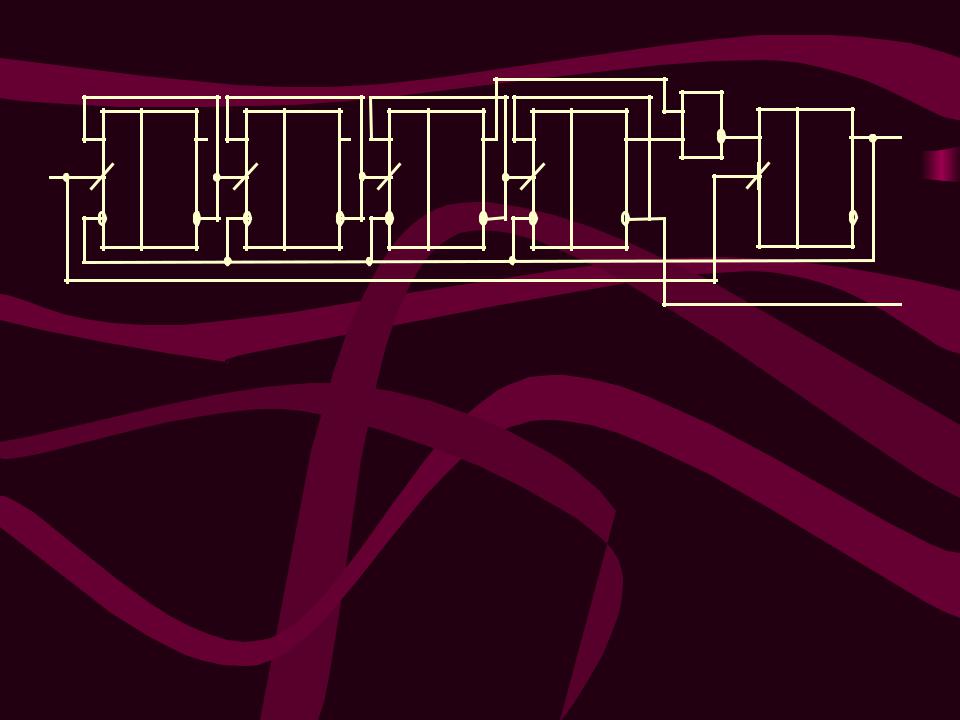

- •J-K-триггеры имеют только по одному входу J- и K-. Логические функции для управления

- •ПАРАЛЛЕЛЬНЫЕ И ПОСЛЕДОВАТЕЛЬНЫЕ РЕГИСТРЫ

- •ПАРАЛЛЕЛЬНЫЕ РЕГИСТРЫ

- •ПОСЛЕДОВАТЕЛЬНЫЕ РЕГИСТРЫ

- •После подачи «n» тактовых импульсов n-битовый последовательный код вдвигается полностью в регистр и

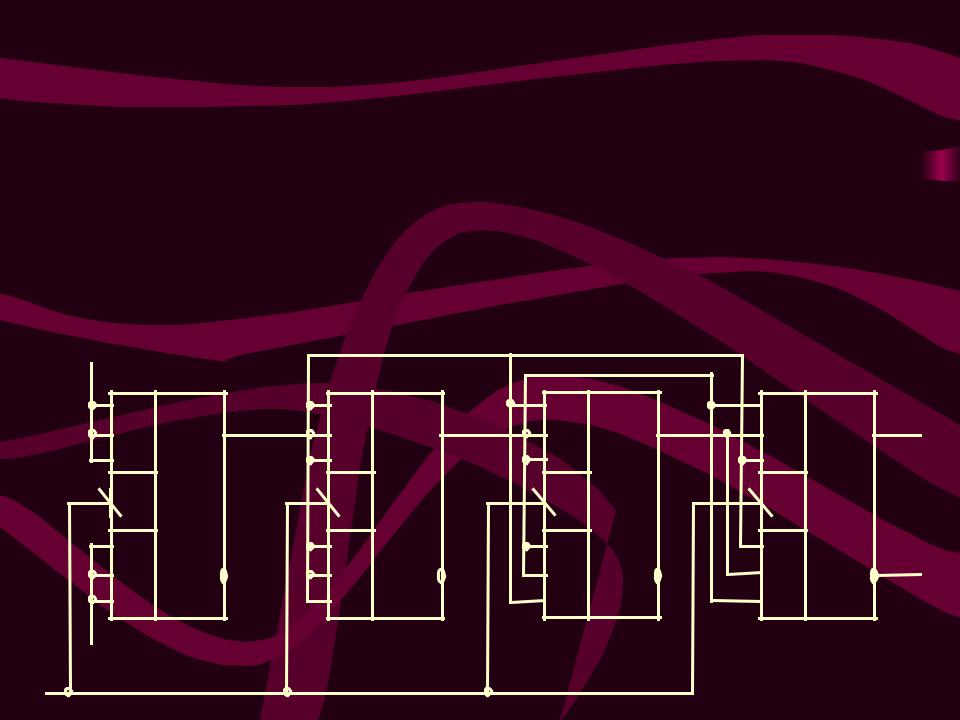

- •В некоторых схемах совмещаются функции параллельного и последовательного регистров. На рис. приведена схема

- •КОЛЬЦЕВЫЕ СЧЕТЧИКИ

- •Максимальный коэффициент пересчета кольцевых счетчиков равен числу «закольцованных» триггеров.

- •Неприятной особенностью кольцевых счетчиков является возможность сбоев, вызванных появлением лишних или исчезновением нужных

- •Вопросы для экспресс-контроля

- •ЛЕКЦИЯ ОКОНЧЕНА

Компьютерная Схемотехника |

2012 |

ДВОИЧНЫЕ СЧЕТЧИКИ и СЧЕТЧИКИ НА ИХ ОСНОВЕ

РЕГИСТРЫ и КОЛЬЦЕВЫЕ СЧЕТЧИКИ

ХНУРЭ, факультет КИУ, каф ЭВМ, Тел. 70-21-354. Доц. Торба А.А.

Компьютерная Схемотехника |

2012 |

ОСНОВНЫЕ ТЕМЫ ЛЕКЦИИ

•СУММИРУЮЩИЙ СЧЕТЧИК

•ВЫЧИТАЮЩИЙ СЧЕТЧИК

•РЕВЕРСИВНЫЙ СЧЕТЧИК

•СЧЕТЧИКИ С ПРОИЗВОЛЬНЫМ КОЭФФИ- ЦИЕНТОМ ДЕЛЕНИЯ

•ПАРАЛЛЕЛЬНЫЕ РЕГИСТРЫ

•ПОСЛЕДОВАТЕЛЬНЫЕ РЕГИСТРЫ

•КОЛЬЦЕВЫЕ СЧЕТЧИКИ

ДВОИЧНЫЕ СЧЕТЧИКИ И СЧЕТЧИКИ НА ИХ ОСНОВЕ

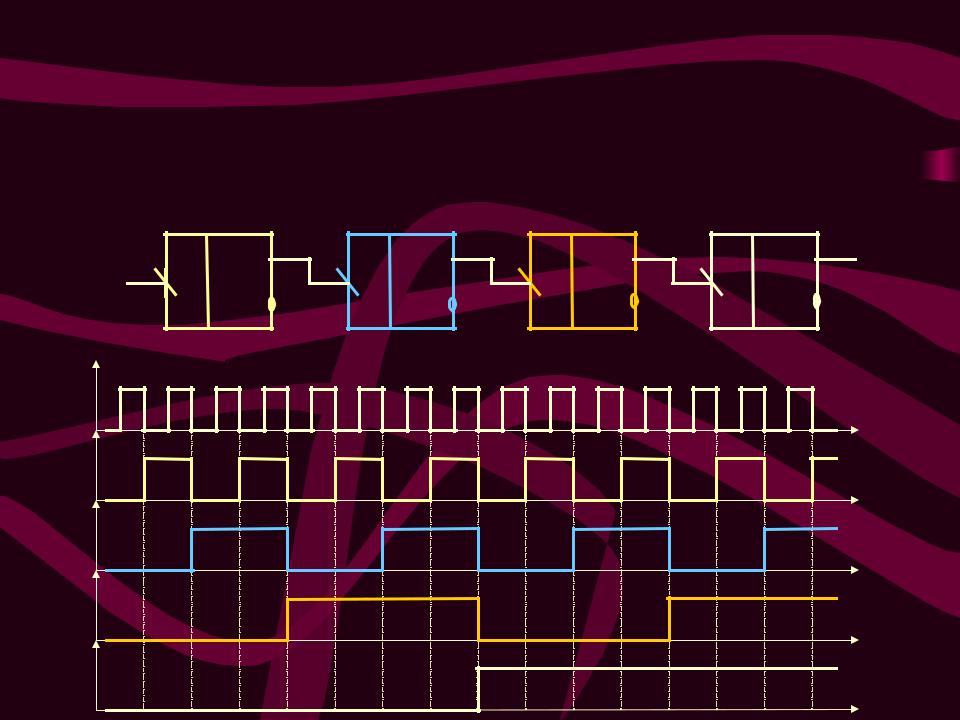

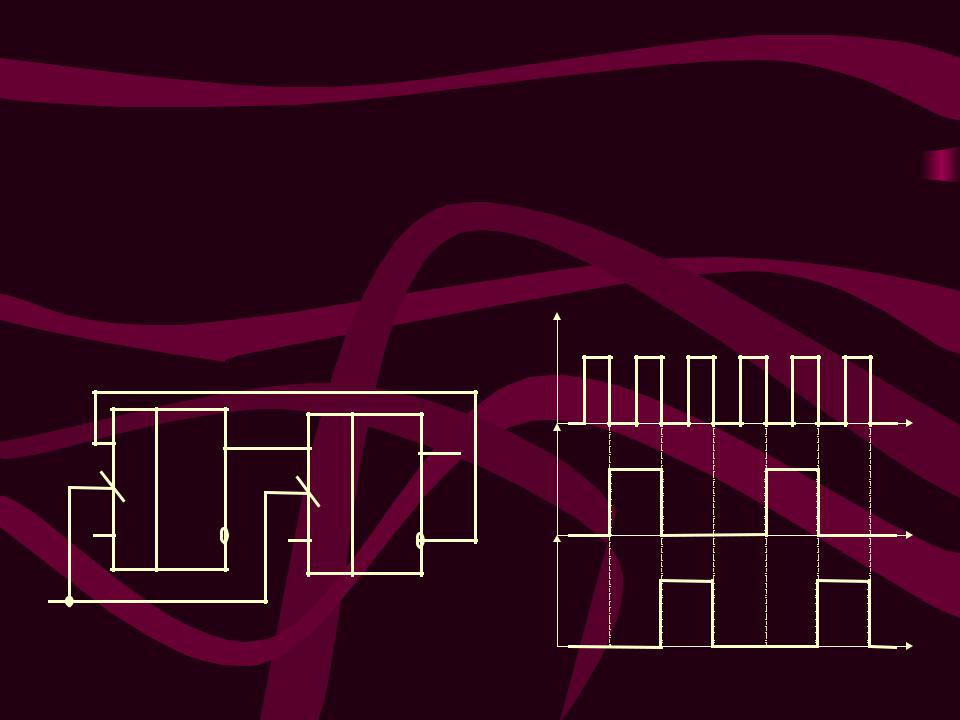

Простейший двоичный счетчик может быть реализован путем последовательного соединения счетных Т-триггеров

Вход |

C1 |

|

C |

T1 |

|

Q1 |

C |

T2 |

|

Q2 |

C |

T3 |

Q3 |

C |

T4 |

Q4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

С1 |

0 |

1 |

|

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

ВЫЧИТАЮЩИЙ ДВОИЧНЫЙ СЧЕТЧИК

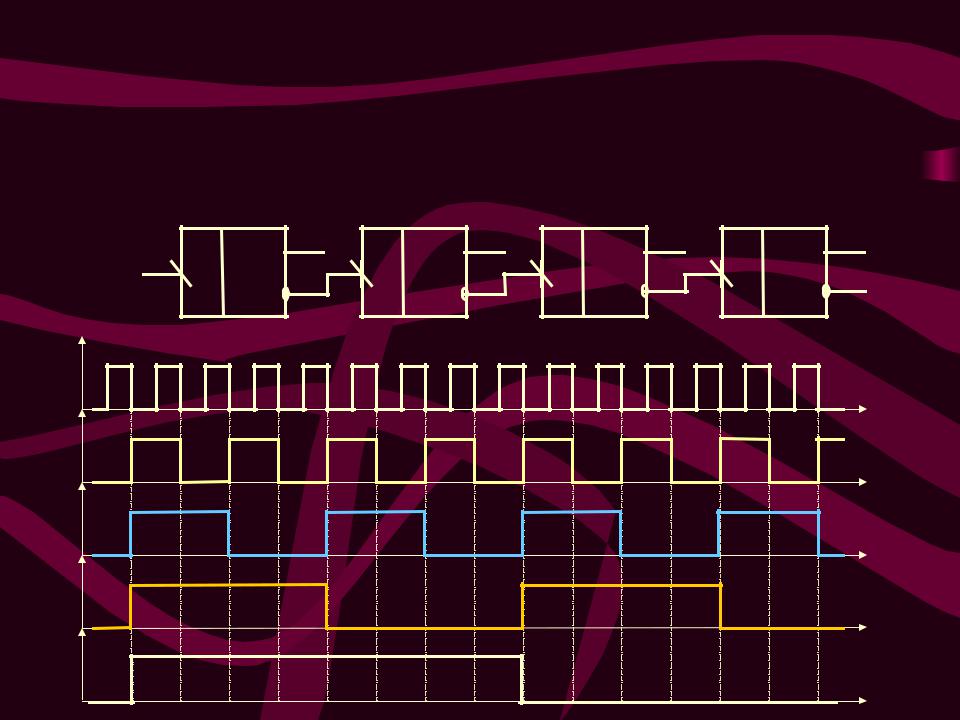

На основе Т-триггеров можно построить ВЫЧИТАЮЩИЙ ДВОИЧНЫЙ СЧЕТЧИК, если на вход следующего триггера подавать сигналы с инверсного выхода предыдущего триггера

Вход |

|

C1 |

C |

T1 |

Q1 |

C |

T2 |

Q2 |

|

C |

T3 |

Q3 |

C |

T4 |

Q4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

С1 |

0 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

На рис. приведен фрагмент РЕВЕРСИВНОГО СЧЕТЧИ-КА. Этот счетчик может работать как суммирующий при подаче на управляющий вход «D/~U» низкого логического уровня или как вычитающий, если подать на управляющий вход высокий логический уровень.

Переключение режимов реверсивного счетчика осуществляется мультиплексорами «2 на 1».

В большинстве случаев счетчики имеют цепи установки всех триггеров в исходное состояние (на рис. показана цепь асинхронного сброса всех триггеров в нулевое состояние).

|

|

|

Q1 |

|

|

|

Q2 |

|

Q3 |

C1 |

C |

T1 |

X0 |

MS |

C |

T2 |

X0 MS |

C |

T3 |

|

|

X1 |

|

|

X1 |

|

|||

|

R |

|

A |

|

R |

|

A |

R |

|

|

|

|

|

|

|

|

|

||

D/~U |

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

Общим недостатком всех счетчиков с последовательным переносом (в литературе встречается также название «асинхронные счетчики») являются большие и неравномер- ные задержки распространения входного сигнала до всех выходов триггеров. Особенно большие задержки распростра- нения сигнала заметны на выходе последнего триггера.

Для выравнивания временных задержек всех триггеров применяют счетчики с параллельным переносом, которые называются также «синхронными счетчиками».

+1

|

& |

T1 Q1 |

& |

T2 Q2 |

& |

T3 Q3 |

& |

T4 Q4 |

|

J |

|

J |

|

J |

|

J |

|

|

C |

|

C |

|

C |

|

C |

|

|

& |

|

& |

|

& |

|

& |

|

|

K |

|

K |

|

K |

|

K |

|

C |

+1 |

|

|

|

|

|

|

|

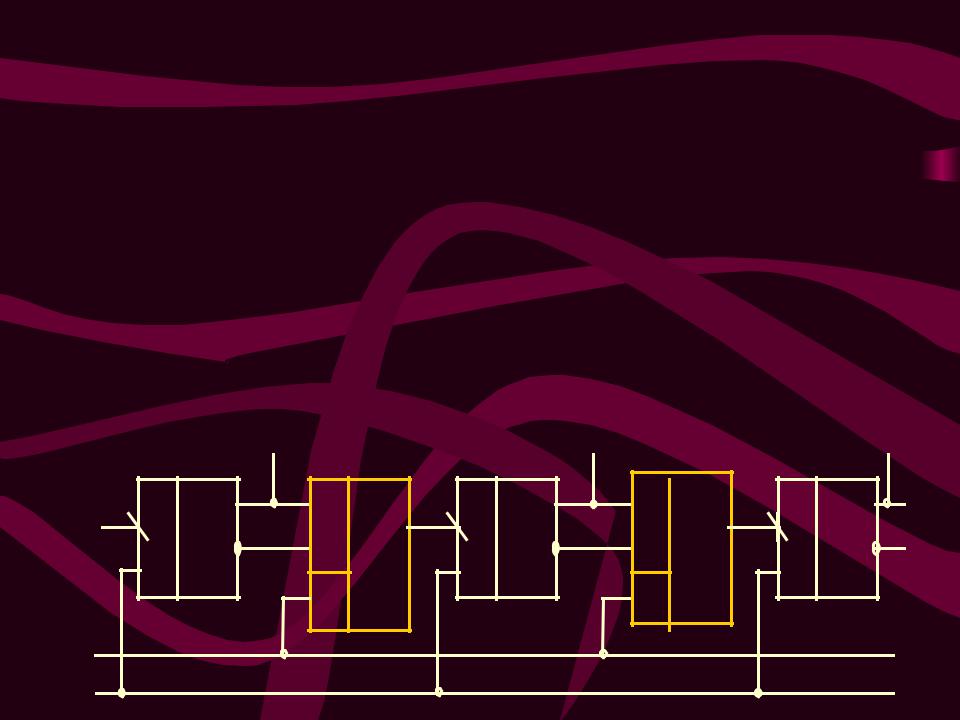

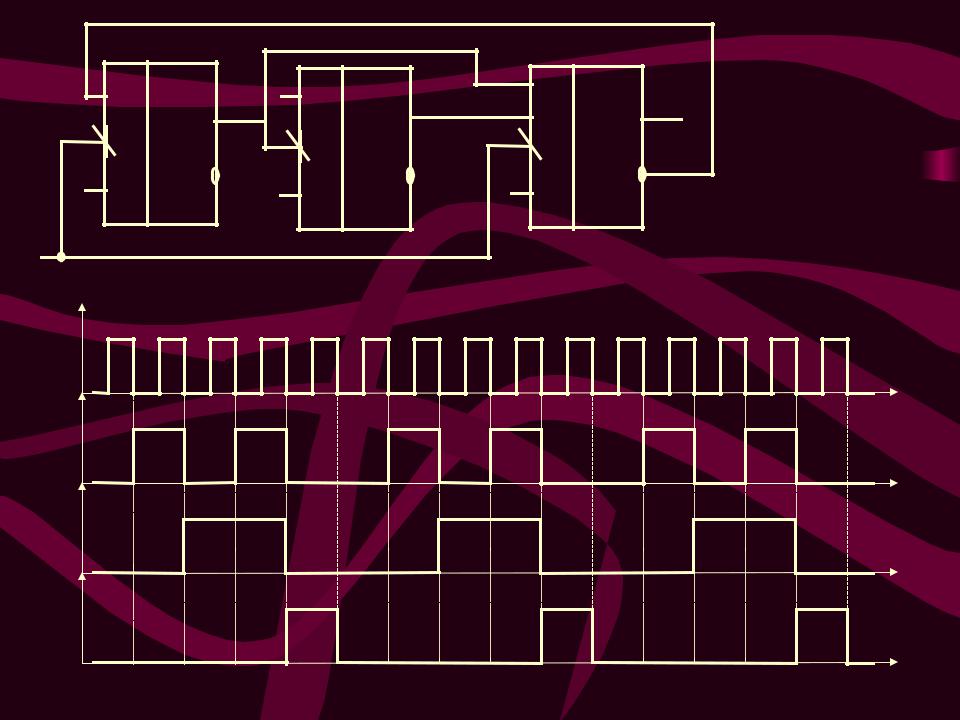

СЧЕТЧИКИ С ПРОИЗВОЛЬНЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

На практике часто возникает потребность реализации счетчиков с коэффициентами деления, отличными от 2n. На рис. приведена схема счетчика с коэффициентом деления k=3 и его временные диаграммы.

|

|

|

С1 |

0 |

1 |

2 |

0 |

1 |

2 |

|

J T1 Q1 |

J T2 Q2 |

Q1 |

|

|

|

|

|

t |

|

C |

C |

|

|

|

|

|

|

|

C |

+1 K |

+1 K |

Q2 |

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

J |

T1 |

Q1 +1 |

J |

T2 |

Q2 |

|

& |

T3 |

Q3 |

Делитель |

|

|

C |

|

|

C |

|

|

|

J |

|

|

на 5 |

|

|

|

|

|

|

|

C |

|

|

|||

C |

+1 |

K |

|

+1 |

K |

|

|

+1 |

K |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

С1 |

0 |

1 |

2 |

3 |

4 |

0 |

1 |

2 |

3 |

4 |

0 |

1 |

2 |

3 |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

t

|

Синтез делителя на k = 14 |

|

определяем количество триггеров - n: |

, |

n ] log (k - 2) [ |

(знак ]...[ - означает ближайшее большее целое), |

|

• |

; n ] log (14 - 2) [ 4 |

переводим в двоичный код число «k-2»;

; |

14 - 2 12(10) 1100(2) |

в счетчике с количеством триггеров n выделяем разряды,

которым в двоичном коде числа «k–2» соответствуют единицы; с выходов этих триггеров подаем сигналы на элемент Шеффера; выходной сигнал этого элемента является информационным для дополнительного D-триггера; сигнал с выхода D-триггера подается на входы асинхронного сброса всех триггеров счетчика.

|

0 |

|

0 |

1 |

1 |

|

C |

D |

T1 |

D T2 |

D T3 |

D T4 |

& A D T5 ~F/14 |

C |

|

C |

C |

C |

C |

|

|

|

|||||

|

R |

|

R |

R |

R |

|

|

|

|

|

|

|

~F/14 |

Делитель реализован на D-триггерах типа КР1533ТМ2. Эти триггеры управляются восходящим фронтом «0-1». Над триггерами Т1..Т4 приведен двоичный код числа 12 (младший разряд кода - над первым триггером). Выходы триггеров Т3 и Т4 подключены ко входам элемента Шеффера. Коды выходных логических сигналов для всех триггеров и элемента «И-НЕ» (точка А) приведены в табл.