- •Минобрнауки россии

- •Исследование цифрового сигнального процессора

- •305040, Г. Курск, ул. 50 лет Октября, 94.

- •Цель работы

- •Краткая характеристика исследуемого программного комплекта

- •Краткие теоретические сведения

- •3.1 Встроенный аналого-цифровой преобразователь - (Analog to Digital Converter)

- •3.2 Работа аналого-цифрового преобразователя

- •3.3 Предварительное деление

- •3.4 Регистр управления и состояния adc - adcsr - (adc Control and Status Register)

- •3.5 Регистры данных adc - adcl и adch - (adc Data Register)

- •3.6 Сканирование аналоговых каналов

- •4 Задание к лабораторной работе

- •5 Порядок выполнения лабораторной работы

- •6 Содержание отчета

- •Контрольные вопросы

- •Библиографический список

Краткие теоретические сведения

3.1 Встроенный аналого-цифровой преобразователь - (Analog to Digital Converter)

Основные характеристики:

- Разрешение 10 разрядов.

- Точность ±1/2 LSB.

- Время преобразования 70...280 мс.

- 8 мультиплексируемых каналов входа.

- Режимы циклического и однократного преобразования.

- Прерывание по завершению ADC преобразования.

- Устройство подавления шумов Sleep режима.

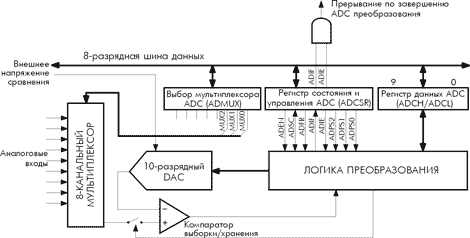

Микроконтроллеры ATmega16 оснащены 10-разрядным ADC последовательного приближения. ADC подсоединен к 8-канальному аналоговому мультиплексору, позволяющему использовать любой вывод порта А в качестве входа ADC. ADC содержит усилитель выборки/хранения, удерживающий напряжение входа ADC во время преобразования на неизменном уровне. Блок-схема ADC представлена на Рис.1. Для питания ADC используются два отдельных вывода: AVCC и AGND. Вывод AGND должен быть подсоединен к GND и напряжение AVCC не должно отличаться от напряжения VCC более чем на (0,4 В).

Рисунок 1 - Блок-схема аналого-цифрового преобразователя

Внешнее напряжение сравнения подается на вывод AREF и должно быть в диапазоне от 2,7 В до AVCC.

3.2 Работа аналого-цифрового преобразователя

Аналого-цифровой преобразователь может работать в двух режимах: режиме однократного преобразования и режиме циклического преобразования. В режиме однократного преобразования каждое преобразование инициируется пользователем. В режиме циклического преобразования ADC осуществляет выборку и обновление содержимого регистра данных ADC непрерывно (см. рис.1). Выбор режима производится битом ADFR регистра ADCSR.

Работа ADC разрешается установкой в состояние 1 бита ADEN в регистре ADCSR. Первому преобразованию, начинающемуся после разрешения ADC, предшествует пустое инициализирующее преобразование. На пользователе это отражается лишь тем, что первое преобразование будет занимать 27 тактовых циклов, вместо обычных 14.

Преобразование начинается с установки в состояние 1 бита начала преобразования ADSC. Этот бит находится в состоянии 1 в течение всего цикла преобразования и сбрасывается, по завершении преобразования, аппаратно. Если в процессе выполнения преобразования выполняется смена канала данных, то ADC вначале закончит текущее преобразование и лишь потом выполнит переход к другому каналу.

Поскольку ADC формирует 10-разрядный результат, то по завершении преобразования результирующие данные размещаются в двух регистрах данных ADCH и ADCL. Для обеспечения соответствия результирующих данных считываемому уровню используется специальная логика защиты. Этот механизм работает следующим образом: при считывании данных первым должен быть считан регистр ADCL. Как только ADCL считан обращение ADC к регистрам данных блокируется. Таким образом, если после считывания состояния ADCL, но до считывания ADCH, будет завершено следующее преобразование, ни один из регистров не будет обновлен и записанный ранее результат не будет искажен. Обращение ADC к регистрам ADCH и ADCL разрешается по завершении считывания содержимого регистра ADCH.

ADC имеет свое собственное прерывание, которое может быть активировано по завершению преобразования. Когда обращение ADC к регистрам запрещено, в процессе считывания регистров ADCL и ADCH, прерывание будет активироваться, даже если результат будет потерян.