- •Министерство образования и науки Российской федерации

- •1. Последовательностные устройства

- •1.1 Триггера.

- •1.2 Регистры.

- •1.3 Счетчики.

- •2. Делители и синтезаторы частоты

- •2.1 Делители частоты с постоянным коэффициентом деления.

- •2.2 Делители частоты с управляемым коэффициентом деления.

- •2.3 Синтезаторы частоты прямого синтеза.

- •2.4 Синтезаторы с фазовой автоподстройкой частоты.

- •3. Полупроводниковые запоминающие

- •3.1 Классификация и структурная организация запоминающих устройств.

- •3.2 Схемотехника запоминающих ячеек накопителей статических запоминающих устройств.

- •3.3 Принципы работы и методы повышения быстродействия динамической памяти.

- •3.4 Постоянные и перепрограммируемые запоминающие устройства.

- •Лехин Сергей Никифорович

- •Часть 3.

3. Полупроводниковые запоминающие

УСТРОЙСТВА

3.1 Классификация и структурная организация запоминающих устройств.

Запоминающее устройство представляет собой узел, позволяющий заносить данные, хранить и обеспечивать их выдачу. Таким образом у него должно быть три основных режима работы – запись, хранение и считывание.

Так как информационные биты, или разряды в общем случае не связаны друг с другом, то есть независимы, то массивы данных можно обрабатывать побитно. При этом для запоминания одной информационной единицы, (бита), который представляет собой нулевое или единичное значение разряда двоичного слова, потребуется использовать отдельную специальную ячейку. Количество ячеек памяти для хранения массива цифровых данных должно быть равно объему этого массива в битах.

Ячейки запоминающего устройства должны удовлетворять следующим основным требованиям. Так как бит принимает два значения – логического нуля и единицы, то ячейка для его хранения должна иметь два различающихся устойчивых состояния. Одному из них можно поставить в соответствие наличие логического нуля, а другому – единицы. Кроме этого, ячейка должна менять эти состояния под действием внешних управляющих сигналов, что соответствует процедуре записи информации и обеспечивать возможность определения или считывания ее текущего состояния. Обычно считывание данных должно происходить без их разрушения, то есть без изменения состояния ячейки.

Совокупность таких запоминающих ячеек называется накопителем, а их количество – емкостью памяти. При записи или считывании конкретного бита, в соответствующем режиме должна функционировать только одна из ячеек накопителя, а остальные не должны реагировать на внешние воздействия. Это можно реализовать путем активизации требуемой ячейки специальным сигналом выборки. При его отсутствии она должна находиться в режиме хранения ранее запомненного бита.

Так как ячейки накопителя одинаковы, а данные требуется заносить в конкретную и считывать из нее, то чтобы ячейки различить, их нумеруют и этот номер называется адресом. При задании адреса по к ячейке определенной линии должен быть подан сигнал для ее активизации.

И сходя

из этого структуру внешних линий связи

с ячейками накопителя можно представить

следующим образом. По шинам записи и

считывания поступают управляющие

сигналы, по шинам данных – входная и

выходная информация, а адресная линия

передает сигнал для активизации (выборки)

ячейки. Вследствие того, что неактивная

(невыбранная) ячейка не реагирует на

внешние воздействия, это позволяет

объединить одноименные линии данных и

управления для всех ячеек накопителя.

Но адресные линии должны быть разделены,

то есть к каждой ячейке требуется

подводить свой сигнал выборки.

сходя

из этого структуру внешних линий связи

с ячейками накопителя можно представить

следующим образом. По шинам записи и

считывания поступают управляющие

сигналы, по шинам данных – входная и

выходная информация, а адресная линия

передает сигнал для активизации (выборки)

ячейки. Вследствие того, что неактивная

(невыбранная) ячейка не реагирует на

внешние воздействия, это позволяет

объединить одноименные линии данных и

управления для всех ячеек накопителя.

Но адресные линии должны быть разделены,

то есть к каждой ячейке требуется

подводить свой сигнал выборки.

Количество таких линий должно быть равно числу ячеек в накопителе. При подаче сигналов выборки извне техническая реализация запоминающего устройства возможна, если число ячеек накопителя не превышает нескольких десятков. Для уменьшения количества внешних линий связи адрес (номер ячейки) задается в двоичном коде, а для формирования сигналов выборки используется специальный узел, который преобразует код номера ячейки в соответствующий сигнал выборки.

В этом случае при Nячейках накопителя число внешних адресных линий будет равноn=log2N, а соответствующее устройство должно выполнять преобразовывать двоичный код в унитарный, то есть выполнять функции дешифратора.

Для записи информации в ячейку накопителя, требуется задать ее адрес (при этом она окажется выбранной или активизированной), подать сигнал входных данных и управляющий сигнал записи, обозначаемый обычно буквой W(от словаwrite). Для считывания необходимо выбрать ячейку и по соответствующей линии подать сигнал считывания -R(read). При этом на ее выходе появится некоторый сигнал, зависящий от состояния в котором ячейка находится. Он преобразуется в стандартные уровни логического нуля или единицы, которые могут быть считаны с выхода запоминающего устройства. Если ячейка не выбрана, то есть адресный сигнал не совпадает с ее номером в накопителе, она находится в режиме хранения, при этом никакие внешние сигналы не изменят ее текущего состояния.

По структурной организации запоминающие устройства делятся на двухадресные (двухпортовые), одноадресные и безадресные. Связь между узлами в первом варианте можно отобразить следующим образом. Здесь имеется накопитель и два дешифратора адреса, один из которых позволяет выбирать требуемую ячейку для записи информации, а другой для считывания. Усилители (устройства) записи и считывания служат для согласования параметров внешних сигналов управления с уровнями соответствующих напряжений накопителя и наоборот. Это связано с тем, что схемотехника запоминающих ячеек обычно отличается от стандартной конфигурации вентилей ТТЛ и КМОП, используются другие напряжения питания и уровни управляющих сигналов.

Д

анная

структура является наиболее универсальной,

так как позволяет одновременно, то есть

параллельно, производить считывание

информации из одной ячейки и запись в

другую. Однако техническая реализация

таких устройств является достаточно

сложной задачей и поэтому их емкость

обычно невелика. Наибольшее распространения

получила одноадресная память, в которой

организован последовательный цикл

записи / чтения.

анная

структура является наиболее универсальной,

так как позволяет одновременно, то есть

параллельно, производить считывание

информации из одной ячейки и запись в

другую. Однако техническая реализация

таких устройств является достаточно

сложной задачей и поэтому их емкость

обычно невелика. Наибольшее распространения

получила одноадресная память, в которой

организован последовательный цикл

записи / чтения.

Ее структура имеет вид. Здесь применен один дешифратор адреса, который используется как в режиме записи, так и при считывании информации. Поэтому, в отличие от предыдущего варианта запоминающего устройства, данные процедуры не могут перекрываться во времени, то есть выполняться одновременно. Таким образом, здесь возможен либо режим записи в заданную ячейку, либо считывания из другой или из той же самой.

Устройство управления используется для формирования соответствующих сигналов при разных режимах работы памяти. В некоторых вариантах одноадресных запоминающих устройств записываемый бит может быть одновременно считан с выхода, а в других выход в режиме записи блокируется.

Кроме записи и считывания часто вводится еще один режим, который называется выборкой кристалла. При этом, сигналом, поступающим на специальный вход, накопитель отключается от всех остальных узлов, а выходной каскад усилителя считывания принудительно закрывается, если он построен по схеме с открытым коллектором, либо переводится в третье (Z) состояние. Наличие такого режима позволяет объединять устройства памяти с целью увеличения объемов обрабатываемой информации.

Как следует из названия третьей разновидности запоминающих устройств – безадресные, в них при обращении к ячейке для записи или считывания не требуется указывать ее номер, то есть адрес. Одним из примеров такого запоминающего устройства является параллельный регистр.

Он представляет собой набор триггерных ячеек, в которых можно запоминать одно многоразрядное двоичное слово. В случае одноразрядного слова регистр вырождается в триггер, то есть в запоминающее устройство с единственной ячейкой накопителя. Второй пример безадресного устройства памяти – регистр сдвига (стек), в котором множество последовательно соединенных ячеек имеют свои номера, или адреса, однако при работе такого регистра перебор адресов осуществляется автоматически (последовательно) и внешние сигналы адреса не требуются.

Запоминающие устройства характеризуются соответствующим набором параметров, основными из которых являются: информационная емкость, быстродействие, энергопотребление.

Информационная емкость– это максимальный объем хранимой информации равный количеству ячеек накопителя. Так как информационная емкость запоминающей ячейки равна одному биту, то в этих же единицах измеряется и емкость накопителя. Часто используются и производные, более крупные единицы - килобиты, которые обозначаются большой буквойК, мегабиты (М) и т. п. По отношению к цифровым данным добавление приставки «Кило» означает умножение не на тысячу, а на 210=1024, множитель «Мега» это не миллион, а 220=1048576. Если емкость запоминающего устройства равна 16К, то его накопитель содержит 16×210или 16384 ячейки. Для некоторых разновидностей запоминающих устройств применяются и десятичные единицы оценки ее емкости. Поэтому накопители емкостью 10 миллионов бит и 10 Мегабит будут содержать разное количество ячеек.

Ч асто

бывает необходимо одновременно запоминать

или считывать многоразрядные слова. В

этом случае одновременно выбирается

требуемое количество ячеек накопителя

и в каждую из них заносится свой бит

данных. Емкость таких запоминающих

устройств, как и в предыдущем случае

определяется общим количеством ячеек

накопителя, но представляется как

произведение числа хранимых слов на их

разрядность, к примеру 2К×8, 256К×4.

асто

бывает необходимо одновременно запоминать

или считывать многоразрядные слова. В

этом случае одновременно выбирается

требуемое количество ячеек накопителя

и в каждую из них заносится свой бит

данных. Емкость таких запоминающих

устройств, как и в предыдущем случае

определяется общим количеством ячеек

накопителя, но представляется как

произведение числа хранимых слов на их

разрядность, к примеру 2К×8, 256К×4.

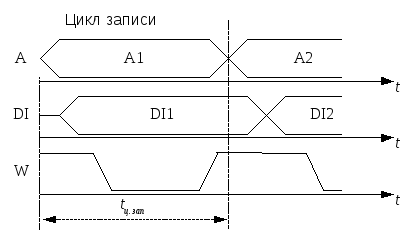

Быстродействие запоминающих устройств оценивается по времени, требуемому для выполнения той или иной операции. Это можно пояснить упрощенными временными диаграммами. Чтобы прочитать данные, необходимо выбрать нужную ячейку, то есть подать на внешние входы запоминающего устройства конкретное значение адреса. Через некоторый интервал времени, определяемый задержками в адресном дешифраторе и линиях связи, ячейка будет активизирована после чего можно подавать сигнал на чтение данных. Считывание происходит либо по положительному фронту этого сигнала, либо по его высокому уровню.

И з-за

конечного быстродействия элементов

памяти выходные данные появятся не

сразу, а с некоторым запаздыванием. Для

чтения бита данных из другой ячейки

необходимо вернуть сигналRв исходное состояние и повторить цикл.

з-за

конечного быстродействия элементов

памяти выходные данные появятся не

сразу, а с некоторым запаздыванием. Для

чтения бита данных из другой ячейки

необходимо вернуть сигналRв исходное состояние и повторить цикл.

В данной ситуации быстродействие оценивается временем доступа и длительностью цикла чтения. Первый параметр определяет минимальный интервал между поступлением сигнала адреса и появлением выходных данных, а второй – время между двумя последовательными обращениями к разным ячейкам. При записи информации сигналы адреса, данных и управления также должны подаваться в строгой последовательности и для надежной фиксации данных иметь определенную длительность, что определяет быстродействие памяти в этом режиме. Запись обычно осуществляется по спаду сигнала управления W.

Энергетические параметры включают в себя величины внешних напряжений питания, токов и мощностей потребления. Иногда в целях сравнения энергетические показатели запоминающих устройств оцениваются по мощности потребляемой на один бит хранимой информации.

По функциональному назначению адресные запоминающие устройства делятся на несколько групп – оперативные, постоянные и перепрограммируемые. Первые называются ОЗУ или RAM(RandomAccessMemory– память с произвольным доступом), вторые ПЗУ илиROM(ReadOnlyMemory– память только для считывания), а третьи –PROM(ProgrammableReadOnlyMemory).

Оперативные запоминающие устройства работают с данными, которые участвуют в информационном обмене при выполнении текущей процедуры обработки информации, они могут записываться, считываться и определенное, относительно небольшое время, храниться. Такие устройства функционируют во всех трех режимах – записи, считывания и хранения.

Одной из отличительных особенностей ОЗУ является потеря занесенной в накопитель информации при отключении питания. В ОЗУ данные записываются либо в триггерные ячейки (память такого типа называется статической), либо хранятся в виде заряда на специальных микроконденсаторах в динамической памяти. В первом случае обесточенные триггера после подачи питания установятся в произвольные состояния, а во втором - отключение питания вызовет полный разряд конденсаторов. При этом записанная информация окажется безвозвратно потерянной.

Статические запоминающие устройства имеют английскую мнемонику SRAM, а динамические –DRAM. Они обладают меньшим быстродействием, но гораздо дешевле и вследствие того, что ячейка накопителяDRAMимеет очень маленькие размеры и энергопотребление, на одном кристалле кремния удается создать накопители очень большой емкости, в сотни и более мегабайт. Память такого типа широко используется в качестве оперативной в современных вычислительных машинах.

Постоянные запоминающие устройства работают только в двух режимах - считывания и хранения, записать туда новые данные невозможно. Они широко используются для хранения фиксированных программ обработки данных, кодовых таблиц и т. п.

Имеется две группы ПЗУ – программируемые маскированием (ROM) и однократно программируемые (PROM). В первые информация заносится на этапе изготовления и изменить ее после этого невозможно. Это память из которой данные можно только считывать.

Однократно программируемые запоминающие устройства это те же ПЗУ, особенность которых состоит в том, что информацию в них может занести пользователь, но только один раз. После этого изменить ее произвольным образом также невозможно. Особенность данных устройств в том, что записанная информация сохраняется там и в отсутствии питании.

Перепрограммируемые или репрограммируемые запоминающие устройства функционально представляют собой некоторую комбинацию ОЗУ и ПЗУ. Информация в них может неоднократно записываться, считываться и сохраняется при отключении питания. Как и ОЗУ, такие устройства работают во всех трех режимах, но их особенность в том, что процедура программирования (записи данных) в современных ППЗУ занимает время в десятки и сотни раз больше, чем считывание и поэтому работать в качестве быстродействующей оперативной памяти они не могут.

Кроме того, ячейки памяти таких устройств перед записью нового массива данных обычно требуется очистить от ранее хранимой информации. Имеется несколько разновидностей ППЗУ, в частности с ультрафиолетовым стиранием, они называются EPROMи с электрическим стиранием –EEPROM.

Сохранение информации в ОЗУ при отключении питания может быть осуществлено путем использования резервных источников энергии, но это реально только при небольшом энергопотреблении, что не позволяет реализовать таким образом блоки памяти большой емкости.

Как уже отмечалось, чтобы записывать и считывать данные, необходимо активизировать (выбрать) соответствующую ячейку накопителя. Для этого на адресной линии, связанной с нею требуется сформировать сигнал определенного уровня. Так как адрес задается в двоичном коде, то в простейшем случае необходимо использовать дешифратор, выходы которого должны быть подключены ко входам выборки ячеек.

Е сли

емкость накопителяM, то

количество выходов дешифратора должно

быть таким же, при разрядности адресной

шиныm=log2M.

Данная структурная организация памяти

называется 2D(D - dimension –

размерность). Здесь одним измерением

считается адресное поле, а другим –

поле данных, так как если требуется

работа с многоразрядными словами, то

одновременно будут выбираться несколько

ячеек.

сли

емкость накопителяM, то

количество выходов дешифратора должно

быть таким же, при разрядности адресной

шиныm=log2M.

Данная структурная организация памяти

называется 2D(D - dimension –

размерность). Здесь одним измерением

считается адресное поле, а другим –

поле данных, так как если требуется

работа с многоразрядными словами, то

одновременно будут выбираться несколько

ячеек.

Недостаток такой организации в сложности дешифратора. Если накопитель содержит тысячу ячеек, то таким же должно быть и количество его выходов.

Б олее

оптимальной для ОЗУ большой емкости

является структура 3D, в которой накопитель

выполняется в виде матрицы и используются

два дешифратора, один для выборки строк,

а другой – столбцов. Схема запоминающей

ячейки в этом случае несколько усложняется,

она делается такой, чтобы ее активизация

происходила при наличии сигнала выборки

строки и столбца, на пересечении которых

расположена ячейка. Условно это можно

представить следующим образом.

олее

оптимальной для ОЗУ большой емкости

является структура 3D, в которой накопитель

выполняется в виде матрицы и используются

два дешифратора, один для выборки строк,

а другой – столбцов. Схема запоминающей

ячейки в этом случае несколько усложняется,

она делается такой, чтобы ее активизация

происходила при наличии сигнала выборки

строки и столбца, на пересечении которых

расположена ячейка. Условно это можно

представить следующим образом.

В

данной структуре для той же емкости

накопителя M

число выходов каждого дешифратора будет

равно ![]() ,

что существенно упрощает его построение.

При емкости накопителя 1024×1, матрица

ячеек накопителя содержит 32 строки и

32 столбца, поэтому потребуются дешифраторы,

у каждого из которых должно быть по 32

выхода.

,

что существенно упрощает его построение.

При емкости накопителя 1024×1, матрица

ячеек накопителя содержит 32 строки и

32 столбца, поэтому потребуются дешифраторы,

у каждого из которых должно быть по 32

выхода.

Дополнительное

упрощение узла адресации реализовано

в памяти со структурой 2DМ. Ее вариант

для накопителя емкостью 1 Кбит имеет

вид. Матрица накопителя разбивается на

несколько блоков, работающих параллельно.

При этом количество строк матрицы

уменьшается, но возрастает длина строки.

В представленном варианте для адресации

строк и групп столбцов понадобятся

дешифраторы 4→16, а для выбора требуемой

ячейки узел, который при считывании

должен выполнять функции мультиплексора

4→1. Т ак

как при записи, данные с внешнего входа

также должны поступать лишь в одну из

ячеек, то в этом режиме узел выборки

должен функционировать как дешифратор

2→4 со стробированием. При больших

объемах накопителя, узел адресации

получается проще, чем в предыдущих

вариантах структур памяти.

ак

как при записи, данные с внешнего входа

также должны поступать лишь в одну из

ячеек, то в этом режиме узел выборки

должен функционировать как дешифратор

2→4 со стробированием. При больших

объемах накопителя, узел адресации

получается проще, чем в предыдущих

вариантах структур памяти.

Полупроводниковые ОЗУ выпускаются в виде интегральных схем, которые реализуются на кристаллах кремния. Они помещаются в пластмассовые или керамические корпуса, имеющие внешние выводы для подачи соответствующих сигналов управления. Успехи современной интегральной технологии позволяют создавать ОЗУ очень большой емкости на кристаллах малых размеров, поэтому габариты микросхемы в основном определяются числом внешних выводов. Для маркировки микросхем ОЗУ используются буквы РУ, располагающиеся после номера серии, например К155РУ7, К565РУ5 и т. п.

Одноразрядное

ОЗУ емкостью 1К×1 изображается на схемах

следующим образом, а его внутренняя

структура имеет вид. Так как в одноадресных

устройствах режимы записи и считывания

во в времени разделены, то для их выбора

используется один сигнал, обозначаемый

![]() .

Черточка

над первым символом условно обозначает

знак инверсии и говорит о том, что режим

записи (write) реализуется при низком

у

.

Черточка

над первым символом условно обозначает

знак инверсии и говорит о том, что режим

записи (write) реализуется при низком

у ровне

такого сигнала, а режим чтения (read) при

высоком. В некоторых схемах ОЗУ запись

и считывание происходят не по уровням

сигнала, а при их изменениях в

соответствующем направлении, то есть

по положительному, либо отрицательному

фронтам сигнала

ровне

такого сигнала, а режим чтения (read) при

высоком. В некоторых схемах ОЗУ запись

и считывание происходят не по уровням

сигнала, а при их изменениях в

соответствующем направлении, то есть

по положительному, либо отрицательному

фронтам сигнала

![]() .

.

В

реальных устройствах оперативной памяти

часто имеется вывод для подачи сигнала

выборки кристалла. Он обозначается

![]() (chip select) и обычно активизирует ОЗУ при

нулевом логическом уровне. Значок в

виде перечеркнутого ромбика у вывода

выходных данных, говорит о том, что при

наличии на входе

(chip select) и обычно активизирует ОЗУ при

нулевом логическом уровне. Значок в

виде перечеркнутого ромбика у вывода

выходных данных, говорит о том, что при

наличии на входе ![]() логической единицы, выход микросхемы

переводится в состояние с высоким

сопротивлением (Z–

состояние). В некоторых вариантах ОЗУ

выходной каскад строится по схеме с

открытым коллектором или стоком. Для

обозначения такой разновидности у

символа выхода ставится значок в виде

ромбика с черточкой снизу

логической единицы, выход микросхемы

переводится в состояние с высоким

сопротивлением (Z–

состояние). В некоторых вариантах ОЗУ

выходной каскад строится по схеме с

открытым коллектором или стоком. Для

обозначения такой разновидности у

символа выхода ставится значок в виде

ромбика с черточкой снизу![]() .

.

Накопитель ОЗУ емкостью 1К×1 содержит 1024 ячейки, организованных в квадратную матрицу 32×32. Схема выборки состоит из двух дешифраторов на пять входов и 32 выхода каждый. Один из них по кодовой комбинации сигналов А0÷А4выбирает строку матрицы, а другой по значению старших разрядов кода адреса А5÷А9– столбец. Активизированной окажется ячейка, находящаяся на пересечении соответствующих строки и столбца.

Входной

информационный сигнал через устройство

управления по шине записи поступает на

выбранную ячейку и при соответствующем

значении

![]() запишется в нее. В режиме считывания

содержимое ячейки по шине ШС проходит

на устройство управления и через выходной

усилитель на выход ОЗУ, если он

активизирован

сигналом

запишется в нее. В режиме считывания

содержимое ячейки по шине ШС проходит

на устройство управления и через выходной

усилитель на выход ОЗУ, если он

активизирован

сигналом ![]() .

При такой организации адрес делится на

две части, которые одновременно поступают

на соответствующие дешифраторы и выбор

ячейки происходит практически сразу

после подачи соответствующих сигналов.

В данной структуре реализуется режим

однотактной адресации.

.

При такой организации адрес делится на

две части, которые одновременно поступают

на соответствующие дешифраторы и выбор

ячейки происходит практически сразу

после подачи соответствующих сигналов.

В данной структуре реализуется режим

однотактной адресации.

Для управления таким устройством потребуется две линии для входных и выходных данных, две для сигналов управления, десять адресных и минимум две для подачи питания (корпус и +Е). В итоге их получается 16, таким же будет и количество выводов микросхемы ОЗУ емкостью 1024×1 (К155РУ7). С ростом емкости накопителя число линий связи будет расти за счет увеличения разрядности адреса. Так для ОЗУ емкостью 16К×1 потребуется корпус с 20 выводами, а модуль памяти 256К×1 может быть помещен в корпус с 24 выводами.

Д ля

уменьшения числа внешних линий связи

используется способ двухтактной

адресации. Один из вариантов памяти

такой структуры емкостью 1К×1 выглядит

следующим образом.

ля

уменьшения числа внешних линий связи

используется способ двухтактной

адресации. Один из вариантов памяти

такой структуры емкостью 1К×1 выглядит

следующим образом.

Здесь

адресное пространство также делится

на две части (младшую - адреса строк и

старшую - адреса столбцов), однако сигналы

адреса поступают не одновременно, а по

очереди, сначала адрес строки, а затем

столбца. Они подаются по одним и тем же

линиям, фиксируются во вспомогательных

регистрах по сигналам записи адреса

строки (raw)

![]() ,

столбца (column)

,

столбца (column)![]() ,

и далее поступают на соответствующие

дешифраторы.

,

и далее поступают на соответствующие

дешифраторы.

Для

того, чтобы в режиме чтения после выбора

строки на выход ОЗУ не поступала

информация из ячейки, находящейся в

столбце, выбранном в предыдущем цикле,

устройство управления блокируется до

прихода сигнала

![]() .

В остальном функционирование данного

ОЗУ не отличается от работы предыдущего.

.

В остальном функционирование данного

ОЗУ не отличается от работы предыдущего.

При такой организации несколько увеличивается время доступа к произвольной ячейке накопителя, но существенно уменьшается число внешних линий связи. Так для ОЗУ емкостью 1К×1 их потребуется 13 (на пять уменьшится количество линий адреса, но добавляется два сигнала управления). В корпус с 16 выводами можно поместить ОЗУ емкостью 64К×1 (К565РУ5).

В некоторых случаях линия

некоторых случаях линия![]() убирается, а состоянием выхода управляют

с помощью сигналов

убирается, а состоянием выхода управляют

с помощью сигналов![]() ,

,

![]() .

или обоими.

По определенному перепаду сигнала

фиксируется адрес столбца, а уровнем

выход переводится в активное, либо

выключенное состояние. Временная

диаграмма работы варианта такого ОЗУ

в режиме чтения имеет вид. В режиме

записи выход переводится в Z

состояние независимо от значения сигнала

.

или обоими.

По определенному перепаду сигнала

фиксируется адрес столбца, а уровнем

выход переводится в активное, либо

выключенное состояние. Временная

диаграмма работы варианта такого ОЗУ

в режиме чтения имеет вид. В режиме

записи выход переводится в Z

состояние независимо от значения сигнала

![]() .

Такой подход дает возможность освободить

еще одну линию под адрес и при том же

числе выводов микросхемы емкость

накопителя может быть в четыре раза

больше, то есть 256К×1 (К565РУ7).

.

Такой подход дает возможность освободить

еще одну линию под адрес и при том же

числе выводов микросхемы емкость

накопителя может быть в четыре раза

больше, то есть 256К×1 (К565РУ7).

Довольно часто при обработке цифровых сигналов требуется запоминать не одноразрядные, а многоразрядные двоичные слова. Для этой цели можно использовать несколько одноразрядных ОЗУ работающих параллельно, но такое устройство может быть выполнено и в виде единой структуры, вариант которой для емкости накопителя 256×4 имеет вид.

Так

как требуемая емкость 1К, то накопитель

такого устройства должен содержать

1024 ячейки памяти и его организуют в виде

матрицы 32×32. Чтобы записывать и считывать

по четыре бита, ячейки объединяются в

группы и при подаче сигнала адреса

обращение происходит сразу ко всей

группе из четырех ячеек.

Так

как требуемая емкость 1К, то накопитель

такого устройства должен содержать

1024 ячейки памяти и его организуют в виде

матрицы 32×32. Чтобы записывать и считывать

по четыре бита, ячейки объединяются в

группы и при подаче сигнала адреса

обращение происходит сразу ко всей

группе из четырех ячеек.

Это реализуется путем объединения у четырех соседних ячеек одной строки линий выборки по столбцам. Структура такого запоминающего устройства и его обозначение на принципиальной схеме имеют вид.

У него количество входных и выходных линий данных в два раза больше разрядности. Число адресных сигналов определяется количеством групп ячеек, так как их 256, то разрядность адресной шины равна 8.

В данной структуре используются два дешифратора, один для адресации строк, а другой групп столбцов, первый имеет 32 выхода, второй 8. Устройство управления оперирует с четырехразрядными сигналами. Для такого ОЗУ понадобится корпус с 20 выводами, если же их количество – 16, то емкость накопителя не может быть больше, чем 16×4 (микросхема К155РУ2).

С

целью дальнейшего уменьшения числа

внешних линий связи ОЗУ может выполняться

с совмещенной шиной данных,

вариант

которого емкостью 256×4 выглядит следующим

образом. Здесь входные данные при записи

и выходные при считывании поступают по

одним и тем же линиямDIO,

но в разные моменты времени. Направление

передачи информации определяется

режимом работы ОЗУ, что никак не влияет

на процедуру функционирования остальных

узлов, так как в одноадресных структурах

процедуры записи и считывания разделены.

вариант

которого емкостью 256×4 выглядит следующим

образом. Здесь входные данные при записи

и выходные при считывании поступают по

одним и тем же линиямDIO,

но в разные моменты времени. Направление

передачи информации определяется

режимом работы ОЗУ, что никак не влияет

на процедуру функционирования остальных

узлов, так как в одноадресных структурах

процедуры записи и считывания разделены.

Для

перенаправления информационных потоков

в состав такого ОЗУ должно входить

специальное коммутирующее устройство,

которое по сигналу

![]() подключает в режиме записи шину данных

ко входам устройства управления, а при

считывании, соединяет ее с выходами. По

сравнению с предыдущим вариантом,

количество линий данных сокращается в

два раза и ОЗУ 256×4 может быть размещено

в корпусе с 16 выводами. Такая разновидность

запоминающих устройств широко используется

в составе вычислительных систем, имеющих

единую шину данных.

подключает в режиме записи шину данных

ко входам устройства управления, а при

считывании, соединяет ее с выходами. По

сравнению с предыдущим вариантом,

количество линий данных сокращается в

два раза и ОЗУ 256×4 может быть размещено

в корпусе с 16 выводами. Такая разновидность

запоминающих устройств широко используется

в составе вычислительных систем, имеющих

единую шину данных.

Емкость запоминающего устройства можно увеличивать соединяя определенным образом функционально законченые блоки ОЗУ, При этом, наращивается либо разрядность, либо адресное пространство.

Пусть имеются

блоки ОЗУ

![]() и на их основе необходимо построить

модуль памяти емкостью

и на их основе необходимо построить

модуль памяти емкостью![]() .

Так как информационные разряды не

связаны друг с другом, то в этой ситуации

можно использовать четыре блока

работающих параллельно. Для этого

потребуется объединить одноименные

линии адреса и сигналов управления, а

входные и выходные данные подавать и

считывать раздельно. Структура такого

модуля будет иметь вид.

.

Так как информационные разряды не

связаны друг с другом, то в этой ситуации

можно использовать четыре блока

работающих параллельно. Для этого

потребуется объединить одноименные

линии адреса и сигналов управления, а

входные и выходные данные подавать и

считывать раздельно. Структура такого

модуля будет иметь вид.

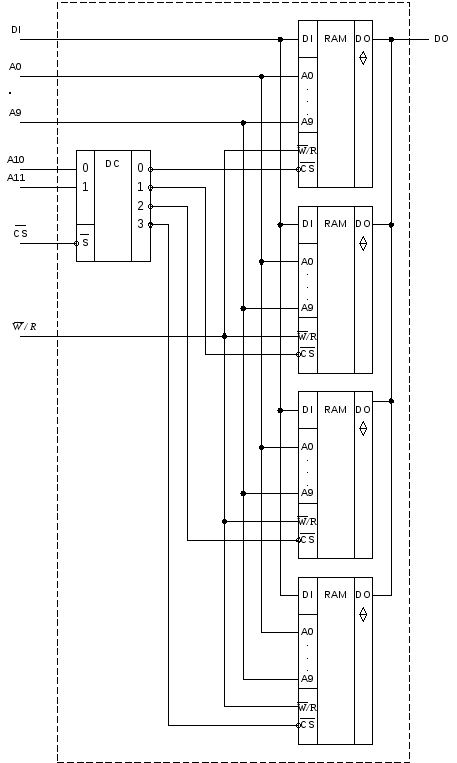

Если из таких же блоков требуется построить модуль емкостью 4К×1, то их также потребуется четыре. Однако структура соединений в этом случае будет существенно отличаться от предыдущей. У модуля должно быть по одному входу и выходу, для чего соответствующие выводы блоков ОЗУ потребуется соединить вместе. Параллельное соединение входов допускается, но с выходами так можно поступать только в случае, когда лишь один из них находится в активном состоянии, а остальные отключены.

К

роме

того, адресное поле блока ОЗУ

десятиразрядное, а у модуля их должно

быть 12. Если накопитель исходного блока

представляет собой квадратную матрицу

размером 32×32 с адресами строк А0÷А4 и

столбцов А5÷А9, то в проектируемом ОЗУ

эта матрица должна иметь размер 64×64 с

адресами А0÷А5и

А6÷А11.

роме

того, адресное поле блока ОЗУ

десятиразрядное, а у модуля их должно

быть 12. Если накопитель исходного блока

представляет собой квадратную матрицу

размером 32×32 с адресами строк А0÷А4 и

столбцов А5÷А9, то в проектируемом ОЗУ

эта матрица должна иметь размер 64×64 с

адресами А0÷А5и

А6÷А11.

Такой накопитель можно представить состоящим из четырех исходных, расположенных следующим образом. Однако при этом возникает проблема с адресацией, так как добавляются дополнительные адреса строк и столбцов.

С другой стороны накопитель можно

представить в виде прямоугольной матрицы

размером 32×128. Здесь количество строк

остается прежним, а общее число столбцов

увеличится в четыре раза. Если адресные

сигналы подавать на одноименные контакты

всех блоков ОЗУ, то одновременно будут

выбираться соответствующие ячейки в

каждом из них. Используя сигналыCS

можно обеспечить поочередную работу

модулей.

другой стороны накопитель можно

представить в виде прямоугольной матрицы

размером 32×128. Здесь количество строк

остается прежним, а общее число столбцов

увеличится в четыре раза. Если адресные

сигналы подавать на одноименные контакты

всех блоков ОЗУ, то одновременно будут

выбираться соответствующие ячейки в

каждом из них. Используя сигналыCS

можно обеспечить поочередную работу

модулей.

Е сли

ОЗУ не выбрано, то никакие внешние

управляющие воздействия не вызовут

изменений состояния его ячеек и они

будут хранить ранее записанную информацию.

Кроме того, в таком режиме выходной

каскад переводится либо в третье

состояние, либо запирается выходной

транзистор в схеме с открытым коллектором.

Это дает возможность подавать на выход

любые внешние сигналы и позволяет

соединять их вместе., Данная структура

накопителя будет более оптимальна при

решении задачи наращивания адресного

пространства запоминающих устройств.

сли

ОЗУ не выбрано, то никакие внешние

управляющие воздействия не вызовут

изменений состояния его ячеек и они

будут хранить ранее записанную информацию.

Кроме того, в таком режиме выходной

каскад переводится либо в третье

состояние, либо запирается выходной

транзистор в схеме с открытым коллектором.

Это дает возможность подавать на выход

любые внешние сигналы и позволяет

соединять их вместе., Данная структура

накопителя будет более оптимальна при

решении задачи наращивания адресного

пространства запоминающих устройств.

Д ля

организации поочередной работы блоков

памяти потребуется формировать четыре

сигнала выборки кристалла, что можно

сделать используя для этого два

дополнительных разряда адреса. Если

выборка осуществляется логическим

нулем, то таблица соответствия между

данными сигналами будет выглядеть

следующим образом. Она описывает работу

дешифратора 2→4, формирующего унитарный

код логических нулей.

ля

организации поочередной работы блоков

памяти потребуется формировать четыре

сигнала выборки кристалла, что можно

сделать используя для этого два

дополнительных разряда адреса. Если

выборка осуществляется логическим

нулем, то таблица соответствия между

данными сигналами будет выглядеть

следующим образом. Она описывает работу

дешифратора 2→4, формирующего унитарный

код логических нулей.

При

соединении

одноименных разрядов адресов всех

блоков памяти будут выбираться четыре

ячейки (по одной в каждом блоке), но

доступной для работы окажется лишь

находящаяся в активизированном ОЗУ.

Для сигналов адреса

![]() доступными станут ячейки первого блока,

при

доступными станут ячейки первого блока,

при

![]() - второго и .т.д. Структурная схема такого

устройства выглядит следующим образом.

- второго и .т.д. Структурная схема такого

устройства выглядит следующим образом.

Д ля

того чтобы у данного модуля памяти был

вход выборки кристалла, необходимо

использовать дешифратор со стробированием.

ля

того чтобы у данного модуля памяти был

вход выборки кристалла, необходимо

использовать дешифратор со стробированием.

Так как при одном и том же значении адреса информация записывается и считывается из одной ячейки накопителя, это в ряде случаев дает возможность упростить разводку плат, содержащих ОЗУ. В случае использовании естественного порядка преобразования двоичного кода адреса в номер ячейки, адресные шины индексируются в соответствие со значениями их весов: А0имеет вес 20, А1– 21и т. д. Чтобы к примеру, записать информацию в ячейку с номером 4, требуется задать код адреса в виде комбинации 00…..00100. Для считывания данные из этой ячейки код адреса должен быть точно таким же.

Е сли

изменить внешнюю разводку адресных шин

(поменять местами, линии А1и А2),

то при подаче в режиме записи на внешние

линии кода четверки, обращение произойдет

ко второй ячейке накопителя. Но, так как

в режиме считывания разводка не меняется,

то при поступлении кода адреса, равного

четырем обращение опять произойдет ко

второй ячейке, к той, куда записывались

данные. Поэтому с точки зрения пользователя

запоминающее устройство будет

функционировать естественным образом.

сли

изменить внешнюю разводку адресных шин

(поменять местами, линии А1и А2),

то при подаче в режиме записи на внешние

линии кода четверки, обращение произойдет

ко второй ячейке накопителя. Но, так как

в режиме считывания разводка не меняется,

то при поступлении кода адреса, равного

четырем обращение опять произойдет ко

второй ячейке, к той, куда записывались

данные. Поэтому с точки зрения пользователя

запоминающее устройство будет

функционировать естественным образом.

Это свойство ОЗУ широко используется при разводке печатных плат, позволяя подключать проводники адресных линий произвольным образом. В связи с этим в разных справочниках нумерация выводов одинаковых адресных линий микросхем оперативной памяти может указываться по-разному.

В цифровых системах, использующих корреляционные принципы обработки сигналов, требуется проводить определенные действия над поступающим сигналом и его сдвинутой во времени копией. Сдвиг может быть реализован с помощью последовательного регистра, однако при его построении на основе триггеров, количество разрядов регистра не может быть сделано достаточно большим. Как уже отмечалось, такие регистры используются и в качестве стековых запоминающих устройств.

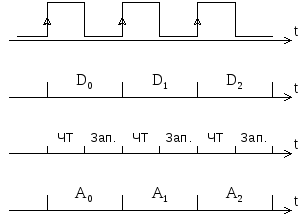

А налог

стека может быть построен на основе

ОЗУ, счетчика адресов и фиксирующего

триггера, как показано на рисунке.

Эквивалентная разрядность такого стека

будет равна емкости накопителя

запоминающего устройства. Временные

диаграммы и таблица функционирования

такого устройства на примере

четырехразрядного ОЗУ выглядят следующим

образом.

налог

стека может быть построен на основе

ОЗУ, счетчика адресов и фиксирующего

триггера, как показано на рисунке.

Эквивалентная разрядность такого стека

будет равна емкости накопителя

запоминающего устройства. Временные

диаграммы и таблица функционирования

такого устройства на примере

четырехразрядного ОЗУ выглядят следующим

образом.

П

еред

началом работыв ячейках ОЗУ может

находиться произвольная информация,

что помечено звездочками. С приходом

положительного фронта тактирующего

сигнала, на выходах счетчика появляется

код адреса

еред

началом работыв ячейках ОЗУ может

находиться произвольная информация,

что помечено звездочками. С приходом

положительного фронта тактирующего

сигнала, на выходах счетчика появляется

код адреса![]() ,

выбирается соответствующая ячейка и

производится чтение ее содержимого. По

отрицательному фронту в ячейку с этим

адресом записывается бит данных

,

выбирается соответствующая ячейка и

производится чтение ее содержимого. По

отрицательному фронту в ячейку с этим

адресом записывается бит данных

![]() ,

а считанное ранее значение фиксируется

в триггере. В следующем такте выбирается

ячейка по адресу

,

а считанное ранее значение фиксируется

в триггере. В следующем такте выбирается

ячейка по адресу![]() ,

считывается ее содержимое и туда же

записывается бит

,

считывается ее содержимое и туда же

записывается бит

![]() .

.

Через

четыре такта, перед записью

![]() из ячейки с адресом

из ячейки с адресом![]() будет считан ранее записанный бит

будет считан ранее записанный бит

![]() и т.д. Таким образом произвольная

последовательность входных данных

окажется задержанной на четыре периода

сигнала тактирования. При использовании

ОЗУ с емкостью накопителя

и т.д. Таким образом произвольная

последовательность входных данных

окажется задержанной на четыре периода

сигнала тактирования. При использовании

ОЗУ с емкостью накопителя![]() и

счетчика с разрядностью

и

счетчика с разрядностью![]() ,

эквивалентная разрядность такого

устройства, имитирующего работу

последовательного регистра сдвига

будет равна М.

,

эквивалентная разрядность такого

устройства, имитирующего работу

последовательного регистра сдвига

будет равна М.