- •Министерство образования и науки Российской федерации

- •1. Последовательностные устройства

- •1.1 Триггера.

- •1.2 Регистры.

- •1.3 Счетчики.

- •2. Делители и синтезаторы частоты

- •2.1 Делители частоты с постоянным коэффициентом деления.

- •2.2 Делители частоты с управляемым коэффициентом деления.

- •2.3 Синтезаторы частоты прямого синтеза.

- •2.4 Синтезаторы с фазовой автоподстройкой частоты.

- •3. Полупроводниковые запоминающие

- •3.1 Классификация и структурная организация запоминающих устройств.

- •3.2 Схемотехника запоминающих ячеек накопителей статических запоминающих устройств.

- •3.3 Принципы работы и методы повышения быстродействия динамической памяти.

- •3.4 Постоянные и перепрограммируемые запоминающие устройства.

- •Лехин Сергей Никифорович

- •Часть 3.

2.2 Делители частоты с управляемым коэффициентом деления.

В таких устройствах коэффициент деления

задается внешним кодом. Для их реализации

используются соответствующие счетчики

с управляемым модулем. Один из вариантов

такого устройства имеет вид. Здесь

используется вычитающий синхронный

счетчик, в который при появлении единичных

сигналов на всех его выходах производится

занесение кода числа К.

таких устройствах коэффициент деления

задается внешним кодом. Для их реализации

используются соответствующие счетчики

с управляемым модулем. Один из вариантов

такого устройства имеет вид. Здесь

используется вычитающий синхронный

счетчик, в который при появлении единичных

сигналов на всех его выходах производится

занесение кода числа К.

Выходной сигнал,

снимаемый с элементов НЕ, представляет

собой последовательность импульсов

длительностью равной удвоенному времени

задержки логического элемента, с периодом

повторения

![]() ,

где

,

где![]() - период входного сигнала. Коэффициент

деления частоты также будет равен К.

- период входного сигнала. Коэффициент

деления частоты также будет равен К.

2.3 Синтезаторы частоты прямого синтеза.

Цифровые синтезаторы

частоты формируют сигналы, частота

следования которых прямо пропорционально

входному коду, то есть

![]() ,

где

,

где![]() - шаг изменения частоты. Из соотношения

следует, что они умножают частоту

- шаг изменения частоты. Из соотношения

следует, что они умножают частоту![]() на соответствующий коэффициент. Однако

реализация умножителей частоты в

произвольное число раз достаточно

сложна, поэтому синтезаторы обычно

строятся таким образом, что реализуется

соотношение

на соответствующий коэффициент. Однако

реализация умножителей частоты в

произвольное число раз достаточно

сложна, поэтому синтезаторы обычно

строятся таким образом, что реализуется

соотношение![]() ,

гдеNи М целые числа,

причем

,

гдеNи М целые числа,

причем![]() .

В таких устройствах интервал времени

длительностью

.

В таких устройствах интервал времени

длительностью![]() заполняется импульсами с частотой

заполняется импульсами с частотой![]() ,

причем их количество определяется

значением кода К.

,

причем их количество определяется

значением кода К. Схема

одного из вариантов такого устройства

с М=8 иN, принимающим

значения от 0 до 7 и временные диаграммы

его работы имеют вид. Его основу составляет

трехразрядный двоичный счетчик с

дополнительными элементами, формирующими

соответствующие импульсные

последовательности.

Схема

одного из вариантов такого устройства

с М=8 иN, принимающим

значения от 0 до 7 и временные диаграммы

его работы имеют вид. Его основу составляет

трехразрядный двоичный счетчик с

дополнительными элементами, формирующими

соответствующие импульсные

последовательности.

Сигналы в точке

![]() появляются с приходом каждого второго

входного импульса, в точке

появляются с приходом каждого второго

входного импульса, в точке![]() каждого четвертого, а в точке

каждого четвертого, а в точке![]() - каждого восьмого, причем они не совпадают

во времени. Данные сигналы появляются

лишь при наличии логических единиц в

соответствующих разрядах

- каждого восьмого, причем они не совпадают

во времени. Данные сигналы появляются

лишь при наличии логических единиц в

соответствующих разрядах![]() управляющего код, а логический элемент

ИЛИ производит их сложение во времени.

При этом количество импульсов на

интервале равном восьми периодам частоты

входного сигнала будет определяться

соотношением

управляющего код, а логический элемент

ИЛИ производит их сложение во времени.

При этом количество импульсов на

интервале равном восьми периодам частоты

входного сигнала будет определяться

соотношением![]() ,

а средняя частота следования выходных

импульсов -

,

а средняя частота следования выходных

импульсов -![]() .

Пример выходного сигнала такого

устройства для К=5 имеет вид.

.

Пример выходного сигнала такого

устройства для К=5 имеет вид.

П ри

увеличении разрядности счетчика и

усложнении соответствующих устройств

выделения импульсов диапазон перестройки

частоты возрастает. Промышленностью

выпускается микросхема К155ИЕ8,

представляющая собой шестиразрядное

устройство, работающее по вышеописанному

принципу и допускающее возможность

наращивания разрядности.

ри

увеличении разрядности счетчика и

усложнении соответствующих устройств

выделения импульсов диапазон перестройки

частоты возрастает. Промышленностью

выпускается микросхема К155ИЕ8,

представляющая собой шестиразрядное

устройство, работающее по вышеописанному

принципу и допускающее возможность

наращивания разрядности.

Недостатком синтезаторов данной конфигурации является значительная неравномерность следования выходных импульсов, что может быть интерпретировано как меняющийся во времени фазовый сдвиг выходных сигналов.

Для формирования

сигналов с большей симметрией к выходу

такого устройства подключают делители

частоты. При этом относительная

неравномерность длительностей импульсов

и пауз уменьшается пропорционально

коэффициенту деления. Выходная частота

в этом случае будет определяться

соотношением

![]() .

Временные диаграммы формируемых сигналов

приN=5, К равном два и

четыре имеют вид.

.

Временные диаграммы формируемых сигналов

приN=5, К равном два и

четыре имеют вид.

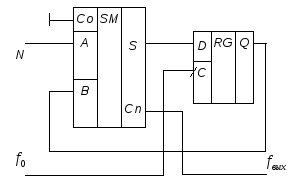

Н

есколько

меньшей нерегулярностью импульсных

последовательностей обладают синтезаторы

частоты прямого синтеза построенные

на основе накапливающих сумматоров.

Структура такого устройства имеет вид.

Оно состоит из сумматора двоичных кодов

чисел и регистра, накапливающего

результат сложения. В каждом такте

происходит прибавление числаN,

присутствующего на входе с ранее

полученной суммой.

есколько

меньшей нерегулярностью импульсных

последовательностей обладают синтезаторы

частоты прямого синтеза построенные

на основе накапливающих сумматоров.

Структура такого устройства имеет вид.

Оно состоит из сумматора двоичных кодов

чисел и регистра, накапливающего

результат сложения. В каждом такте

происходит прибавление числаN,

присутствующего на входе с ранее

полученной суммой.

Так как сумматор

имеет конечную разрядность, то через

определенное количество операций

сложения, выполняемых по моменту прихода

очередного импульса записи, частота

следования которых

![]() ,

произойдет его переполнение и появление

единичного сигнала на выходе переноса.

Этот сигнал будет появляться тем чаще,

чем больше значение кода числа,

поступающего на сумматор.

,

произойдет его переполнение и появление

единичного сигнала на выходе переноса.

Этот сигнал будет появляться тем чаще,

чем больше значение кода числа,

поступающего на сумматор.

Э то

можно пояснить временными диаграммами,

описывающими работу четырехразрядного

накапливающего сумматора при значениях

входного кода, равных 1 и 3. В первом

случае в каждом такте происходит

прибавление по единице и переполнение

возникнет, когда сумма станет равной

16. При этом в регистр запишется нулевое

значение и процесс сложения единиц

повторится. Во втором случае переполнение

реализуется через 6, 5 и 5 тактов то есть

три раза за шестнадцать входных импульсов.

то

можно пояснить временными диаграммами,

описывающими работу четырехразрядного

накапливающего сумматора при значениях

входного кода, равных 1 и 3. В первом

случае в каждом такте происходит

прибавление по единице и переполнение

возникнет, когда сумма станет равной

16. При этом в регистр запишется нулевое

значение и процесс сложения единиц

повторится. Во втором случае переполнение

реализуется через 6, 5 и 5 тактов то есть

три раза за шестнадцать входных импульсов.

Для произвольного

Nчастота выходного сигнала

такого устройства определяется

соотношением![]() .

Неравномерность пауз между импульсами

здесь никогда не превысит одного такта.

При увеличении разрядности сумматора

и регистра до

.

Неравномерность пауз между импульсами

здесь никогда не превысит одного такта.

При увеличении разрядности сумматора

и регистра до![]() работа

устройства работа устройства будет

описываться соотношением

работа

устройства работа устройства будет

описываться соотношением![]() .

Для повышения степени симметрии выходных

сигналов здесь также применяются

дополнительные делители частоты.

.

Для повышения степени симметрии выходных

сигналов здесь также применяются

дополнительные делители частоты.