- •Аналоговая и цифровая электроника

- •Часть 2. Цифровые устройства

- •Введение Логические элементы

- •1. Цифровые микросхемы

- •Контрольные вопросы и задания

- •2. Арифметические сумматоры

- •Контрольные вопросы и задания.

- •3. Логический элемент с тремя состояниями

- •4. Мультиплексоры и демультиплексоры

- •Контрольные вопросы и задания

- •5. Шифраторы и дешифраторы

- •Контрольные вопросы и задания

- •6. Цифровые компараторы

- •7. Устройство контроля четности

- •8. Триггеры

- •Контрольные вопросы и задания

- •9. Счетчики

- •Контрольные вопросы и задания

- •10. Регистры

- •Контрольные вопросы и задания

- •11. Оперативные запоминающие устройства

- •Контрольные вопросы и задания

- •12. Постоянные запоминающие устройства

- •Контрольные вопросы и задания

- •Замечание.

- •13. Арифметико-логическое устройство

- •Контрольные задания

Контрольные вопросы и задания

1. Когда были созданы первая МКС и первый микропроцессор?

2. Что из себя представляют ТТЛ- и КМОП-серии цифровых ИМС?

3. Что позволило радикально повысить быстродействие ТТЛ-серии?

4. В чем заключается различие в обозначениях цифровых ИМС зарубежного и отечественного производства?

5. В чем основное преимущество цифровых КМОП-микросхем по сравнению с ТТЛ и на каких частотах оно проявляется?

6. Какие функции выполняет многоэмиттерный транзистор в ТТЛ ?

7. Из описания процесса формирования на выходе S сигнала логического нуля в схеме вентиля на рис.9 не совсем ясно, в каком состоянии при этом находится транзистор VT3 — в открытом или закрытом. Для проверки необходимо при логической единице на входах А, В, измерить с помощью мультиметра напряжение на коллекторе VT3, предварительно убедившись, что на выходе S сигнал логического нуля. Если это напряжение равно Ucc=+5 В, то это означает, что через резистор R4 ток не течет и, следовательно, транзистор VT3 закрыт. Если это так, попытайтесь объяснить, почему?

8. Проверьте правильность функционирования схемы на рис.12.

2. Арифметические сумматоры

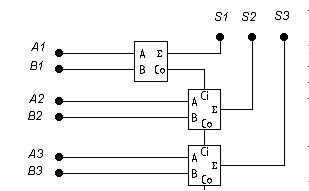

Арифметические сумматоры являются составной частью арифметико-логических устройств (АЛУ) микропроцессоров (МП). Они используются также для формирования физического адреса ячеек памяти в МП с сегментной организацией памяти. В программе EWB арифметические сумматоры представлены двумя базовыми устройствами, показанными на рис.13: полусумматором и полным сумматором. Они имеют следующие назначения выводов: А, В — входы слагаемых, E — результат суммирования. Со — выход переноса, Ci — вход переноса. Многоразрядный сумматор создается на базе одного полусумматора и n полных сумматоров. В качестве примера на рисунке 13 приведена структура трехразрядного сумматора. На входы Al, A2, A3 и Bl, B2, ВЗ подаются первое и второе слагаемые соответственно, а с выходов SI, S2, S3 снимается результат суммирования. Очевидно, что сумматор отличается от полусумматора отсутствием выхода переноса.

Рис.13

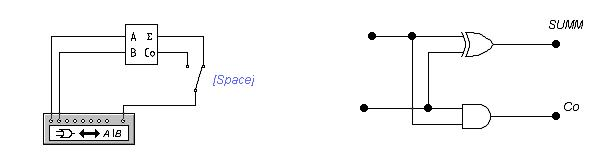

Для исследования внутренней структуры и логики функционирования сумматоров как нельзя лучше подходит логический преобразователь. После подключения полусумматора к логическому преобразователю согласно рисунку 14 а, а последовательно нажимаем соответствующие кнопки логического преобразователя. В результате получаем таблицу истинности и булево выражение. Сравнивая полученные данные с результатами исследования базовых логических элементов, приходим к выводу, что при подключении вывода Е полусумматора к зажиму OUT преобразователя (как показано на рисунке 14 а), он выполняет функции элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Подключив клемму OUT преобразователя к выходу Со полусумматора и проделав аналогичные действия, приходим к выводу, что в таком включении полусумматор выполняет функции элемента И. Следовательно, эквивалентная схема полусумматора имеет вид, показанный на рис.14 б.

Рис.14 а Рис.14 б

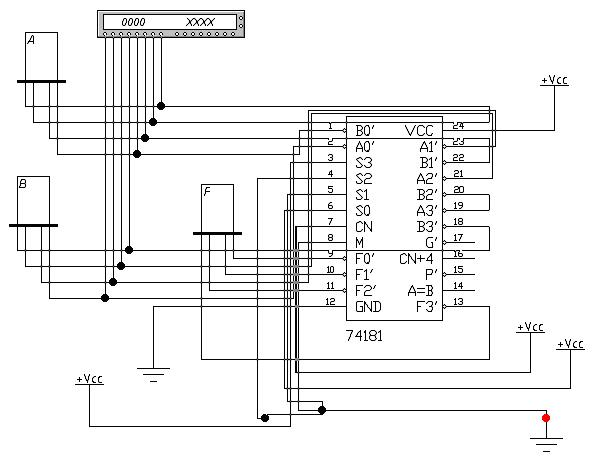

В каталоге программы EWB имеется схема включения четырехразрядного АЛУ на базе серийной микросхемы 74181 (отечественный аналог К155ИПЗ). В несколько переработанном виде она показана на рис.15. ИМС 74181 обеспечивает 32 режима работы АЛУ в зависимости от состояния управляющих сигналов на входах М, S0...S3, а также допускает наращивание разрядности (вход CN и выход CN+4 для переносов). Показанная на рис.6 схема включения ИМС соответствует режиму сумматора без переноса. Значения четырехразрядных операндов А и В на входе задаются с помощью генератора слова и в шестнадцатеричном коде отображаются одноименными алфавитно-цифровыми индикаторами. На выходах F0...F3 результат суммирования отображается индикатором F.

Рис.15