Complex Programmable Logic Device (CPLD) based on EPROM or EEPROM technology PAL device

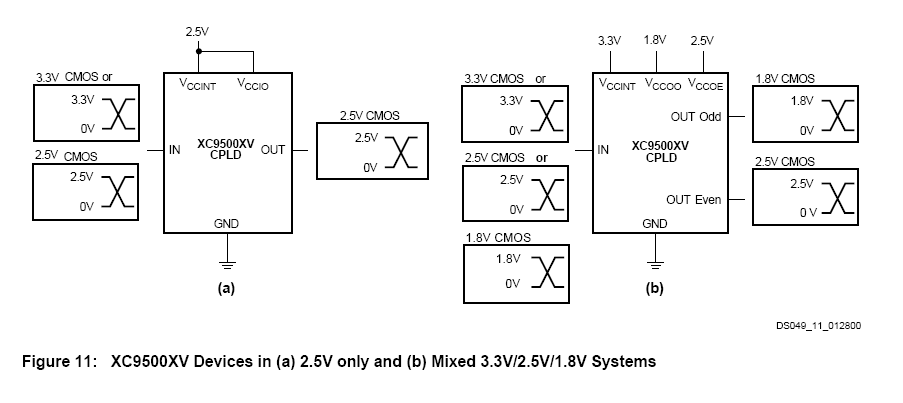

Each user pin is compatible with 3.3V, 2.5V, 1.8V, and 1.5V inputs and the outputs may be configured for 3.3V, 2.5V, or 1.8V operation.

Design Security

In-System Programming

Output Banking designers can have one set of outputs driving to 2.5V and another set to 1.8V

Mixed Voltage In mixed 3.3V/2.5V/1.8V systems, the user pins, the core power supply (VCCINT), and the output power supply (VCCIO) may have power applied in any order.

IEEE 1149.1 Boundary-Scans (JTAG)

Reliability and Endurance

-

10,000 in-system program/erase cycles and a minimum;

-

Data retention of 20 years

Low Power Mode All XC9500XV devices offer a low-power mode for individual macrocells or across all macrocells.