Топологическое проектирование буфера.

Топология буфера, спроектированного по американским размерам, имеет вид (рис.11.).

Для определения площади учтем то, что размеры ячейки кратны размерам квадрата трассировочной сетки, последний имеет размер 0.66*0.66мкм2. Таким образом, площадь элемента равна 12*5= 60 квадратов трассировочной сетки. Анализ его поводим с такими же изменяемыми параметрами, как и для простой схемы. Результаты отражены в таблице 3.

График зависимости задержки переключения нарисован на рисунке 12.

У чет

топологии не внес существенных изменений

в работу схемы, увеличилась только

задержка на 18.8%. Разброс задержек

переключения из «0» в «1» и из «1» в «0»

по-прежнему остается высоким (то есть

порядка 40-50% при больших фронтах).

чет

топологии не внес существенных изменений

в работу схемы, увеличилась только

задержка на 18.8%. Разброс задержек

переключения из «0» в «1» и из «1» в «0»

по-прежнему остается высоким (то есть

порядка 40-50% при больших фронтах).

Топология буфера, спроектированного по американским размерам, имеет вид (рис.13.). Площадь буфера, спроектированного по нашим размерам, оказалась равна 12*6=72кв, что на 20% больше площади американского. Получилось это в связи с тем, что размеры нашего p-канального транзистора гораздо больше размера наибольшего транзистора в американском элементе, а размер карманаNwellпринимается постоянным для всех библиотечных элементов. В результате этого ограниченияp-канальный транзистор с шириной канала 3мкм не помещается в карман так, как представлено в американской модели (из-за того, что контакт к карману выполнен вертикально с транзистором, он накладывает дополнительные ограничения на размер последнего). Поэтому контакт к карману пришлось вынести к стоковой области транзистора, что привело к увеличению площади. Примечание: если ширину транзистора подогнать с учетом ограничений точно под ширину кармана, то естьWp=2.94мкм, то размеры буфера совпадают с американскими, однако контакт ко входу буфера не помещается в узел трассировочной сетки. Поэтому решено было оставить первоначальный вариант. Для него же и проводилось моделирование, результаты которого занесены в таблицу 4.

З

десь

сохраняется равенство задержек

переключения в пределах 10% (смотри

рис.14) и равенство фронта и среза. По

сравнению с идеальным случаем средняя

задержка увеличилась примерно на 18.7%,

то есть примерно на столько же, насколько

и в американском варианте. Как это видно

на рисунке 14, она все равно меньше, чем

задержка реального библиотечного

элемента.

десь

сохраняется равенство задержек

переключения в пределах 10% (смотри

рис.14) и равенство фронта и среза. По

сравнению с идеальным случаем средняя

задержка увеличилась примерно на 18.7%,

то есть примерно на столько же, насколько

и в американском варианте. Как это видно

на рисунке 14, она все равно меньше, чем

задержка реального библиотечного

элемента.

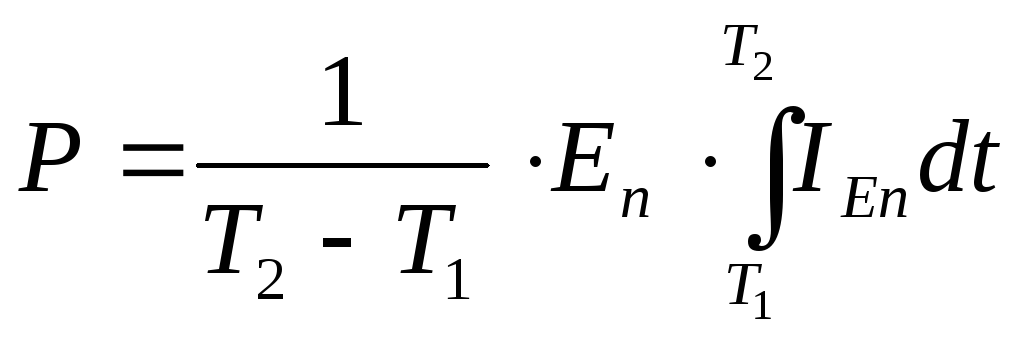

Проведем теперь оценку средней

потребляемой мощности за период. Ее

можно рассчитать по формуле

, где

, где![]() –

потребляемый ток,

–

потребляемый ток,![]() -

напряжение питания, а

-

напряжение питания, а![]() - период. Общие результаты по нашему и

американскому буферу занесены в таблицу

5, а сравнительные графики представлены

на рисунке 15. Здесь дана чисто сравнительная

оценка мощности за период (в нашем случае

он равен 50нс). Поэтому судить о каких-то

конкретных цифрах не совсем корректно.

Можно только дать оценку мощности для

нашего буфера по сравнению с американским.

В данном случае наша мощность получилась

больше американской. Это можно объяснить

только тем, что наши подобранные

транзисторы больше американских,

соответственно через них протекают

большие токи, тем самым увеличивая

мощность. В результате мощность

увеличилась по сравнению с американским

вариантом на 10-15%, а наша почти не

изменилась

- период. Общие результаты по нашему и

американскому буферу занесены в таблицу

5, а сравнительные графики представлены

на рисунке 15. Здесь дана чисто сравнительная

оценка мощности за период (в нашем случае

он равен 50нс). Поэтому судить о каких-то

конкретных цифрах не совсем корректно.

Можно только дать оценку мощности для

нашего буфера по сравнению с американским.

В данном случае наша мощность получилась

больше американской. Это можно объяснить

только тем, что наши подобранные

транзисторы больше американских,

соответственно через них протекают

большие токи, тем самым увеличивая

мощность. В результате мощность

увеличилась по сравнению с американским

вариантом на 10-15%, а наша почти не

изменилась

Т о,

что мы сформировали топологию по

американским размерам, еще не говорит

о том, что данная топология имеет

абсолютно такой же вид. Для сравнения

полученных нами данных для американской

модели с реально существующими

воспользуемся цифрами, взятыми изTLFфайла (TimingLibraryFormat).

о,

что мы сформировали топологию по

американским размерам, еще не говорит

о том, что данная топология имеет

абсолютно такой же вид. Для сравнения

полученных нами данных для американской

модели с реально существующими

воспользуемся цифрами, взятыми изTLFфайла (TimingLibraryFormat).

В случае сильного расхождения в значениях

поведем перерасчет сравнительных

характеристик для нашего и американского

случаев. Итак, реально замеренные данные

занесены в таблицу 6, а на рисунке 16

изображено изменение реальных задержек

относительно задержек для созданного

нами буфера по американским размерам.

Как видно из графиков, разница при этом

очень небольшая и находится в районе

2-3%. Поэтому можно считать топологию,

построенную нами по заданным размерам

(американским), корректной для сравнения

с топологией, построенной по собственным

критериям.

случае сильного расхождения в значениях

поведем перерасчет сравнительных

характеристик для нашего и американского

случаев. Итак, реально замеренные данные

занесены в таблицу 6, а на рисунке 16

изображено изменение реальных задержек

относительно задержек для созданного

нами буфера по американским размерам.

Как видно из графиков, разница при этом

очень небольшая и находится в районе

2-3%. Поэтому можно считать топологию,

построенную нами по заданным размерам

(американским), корректной для сравнения

с топологией, построенной по собственным

критериям.