Задание:

Спроектировать библиотечный элемент типа CLKKBUFX1. Технология 0.18мкм, нагрузочная емкость единичная (от 10 до 40 фФ), напряжение питания 3В.

Буферные ячейки КМОП БИС предназначены для организации электрического и временного взаимодействия ядра БИС с внешней средой. При соблюдении соответствующих правил соединения внутренних и буферных ячеек обеспечивают соответствующие уровни выходных логических сигналов, нагрузочные способности, времена задержек выходных сигналов и длительности их фронтов и так далее. Часто буферные элементы организуются как двунаправленные с целью формирования двунаправленных входов/выходов БИС. За счёт специальных средств управления входами N и P схемы представляется возможным независимо от ядра логической схемы устанавливать на внешних выводах произвольные логические состояния 0, 1 и H.

Проектирование библиотечного элемента разобьем на несколько этапов.

Verilog описание.

Разработку нашего библиотечного элемента начнем с описания его языком высокого уровня, в данном случае Verilog’ ом без указания внутренней структуры. Тогда само описание выглядит так, как представлено ниже.

`timescale 1ns/10ps

module CLKBUFX1 (Y, A, GRND, POWR);

output Y;

input A;

input GRND;

input POWR;

reg Y;

always @(A)

Y=A;

endmodule

module test;

reg A;

wire Y, GRND, POWR;

CLKBUFX1 BUF(.A(A), .Y(Y), .GRND(GRND), .POWR(POWR));

initial

begin

A=0;

forever #10 A=~A;

end

initial # 100 $finish;

endmodule

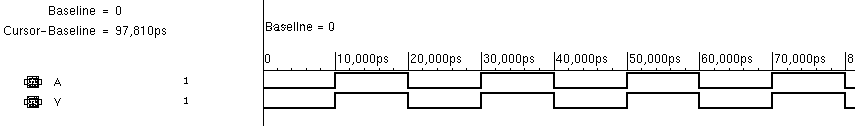

Результаты моделирования:

Выбор схемы.

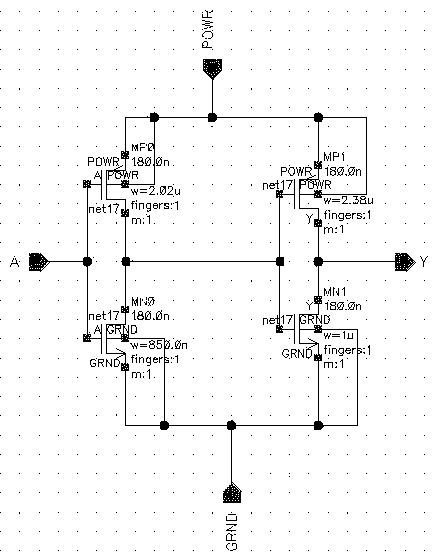

Схему буфера проектируем на основе двух последовательно соединенных инверторов. В конечном варианте схема представлена на рис.1.

Р

Рис.1.

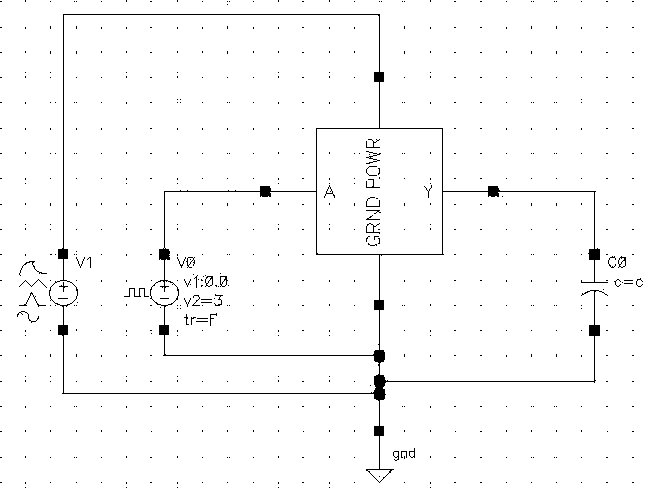

При выборе параметров ширины каналов n- иp-канальных транзисторов принимаются одинаковыми для обоих инверторов и меняются одновременно. Тестовая схема для оптимизации представлена на рисунке 2.

Н

Рис.2.

При проведении анализа по постоянному току порог получился равным 1.53В, то есть больше на 2% от оптимального (см. рис.3).

Аналогичный буфер, спроектированный в библиотеке GPDK, состоит из двух инверторов, имеющих разные ширины канала транзисторов:

Wn1=0.85мкм,Wp1=2.02мкм(базовый инвертор библиотеки);

W n2=1мкм,Wp2=2.38мкм.

Здесь сохранен коэффициент масштабирования

относительно базового инвертора. В

основе принципа, по которому строился

данный буфер, лежит вероятно принцип

построения супербуфера. Наше предположение

в выборе критериев – минимальная

суммарная задержка.

n2=1мкм,Wp2=2.38мкм.

Здесь сохранен коэффициент масштабирования

относительно базового инвертора. В

основе принципа, по которому строился

данный буфер, лежит вероятно принцип

построения супербуфера. Наше предположение

в выборе критериев – минимальная

суммарная задержка.

На рисунке 4 изображен сравнительный DCанализ по постоянному току для обоих полученных буферов. Как видно, для американского элемента пороговое напряжение упало до 1.41В, что составляет 6% от номинала.

Далее был проведен временной анализ исследуемой схемы. Его общий вид изображен на рисунке 5. На рисунках 6 и 7 представлено поведение выходного сигнала в области переключения. Входной фронт = 10пс. Данные рисунки отражают только характер поведения сигнала. Основной анализ будет приведен далее в таблицах.

Моделирование схемы проводилось при различном входном фронте и нагрузке. Фронт имел дискретные значения: 0.05нс, 0.15нс, 0.6нс, 1.5нс, 2.3нс, 3.3нс, 4.5нс. Нагрузку возьмем минимальную и максимальную, поскольку с целом характер изменения задержек при изменении емкости остается примерно одинаковым. В результате моделирования данные занесены в таблицу 1 для нашего случая и в таблицу 2 для аналогичного американского.

В данной таблице задержки удовлетворяют основному критерию с точностью ±10%

П

олученная

из этих таблиц зависимость задержек

переключения от входного фронта

представлена на рисунках 8 и 9 для нашего

буфера и американского варианта

соответственно.

олученная

из этих таблиц зависимость задержек

переключения от входного фронта

представлена на рисунках 8 и 9 для нашего

буфера и американского варианта

соответственно.

Как видно по графикам, в американской модели гораздо больший разброс задержек, нежели в нашей (при большом входном фронте погрешность относительно средней задержки составляет порядка 40-50%). Это можно объяснить только двумя вариантами: либо они изначально подбирали размеры транзисторов на маленьком фронте (в наше же случае на некотором среднем значении диапазона), либо руководствовались другим критерием, поскольку наиболее удачно у них получилось равенство фронта/среза выходного сигнала (погрешность в пределах 5%). Хотя в нашем случае этот параметр тоже оказался примерно одинаковым, попадая в десятипроцентный разброс. Критерий по минимизации средней задержки отражен на рисунке 10. По нему видно, что американский вариант буфера работает медленнее, чем спроектированный нами, хоть и ненамного. Также можно судить о характере изменения задержек при увеличении нагрузочной емкости, поскольку графики идут примерно параллельно, то есть при увеличении емкости идет сдвиг зависимости вверх.

Однако эти графики не дают конструктивной сравнительной оценки обоих буферов. Для более детального анализа необходимо сравнивать характеристики с учетом паразитных элементов, то есть с учетом топологии.