- •Нижегородский государственный университет им. Н.И. Лобачевского

- •Содержание

- •Архитектура GPU NVIDIA

- •Архитектура CPU и GPU

- •Архитектура CPU и GPU

- •Архитектура GPU: общие сведения

- •Архитектура Tesla 8/10

- •Мультипроцессор Tesla 8

- •Мультипроцессор Tesla 10

- •Иерархия памяти Tesla 10

- •Мультипроцессор Fermi

- •Архитектура Fermi

- •Вычислительные возможности

- •Вычислительные возможности

- •Исполнение потоков

- •Основные понятия

- •Взаимодействие потоков

- •Выполнение блоков

- •«Автоматическая масштабируемость»

- •SIMT

- •Пример выполнения варпов

- •Выполнение ветвлений

- •Оптимизация загрузки устройства

- •Иерархия памяти CUDA

- •Типы памяти и скорость доступа

- •Использование локальной памяти

- •Использование константной памяти

- •Использование константной памяти

- •Использование текстурной памяти

- •Использование глобальной памяти

- •Использование глобальной памяти

- •Пример: выделение памяти и копирование вектора

- •Эффективная работа с глобальной памятью

- •Эффективная работа с глобальной памятью

- •Эффективная работа с глобальной памятью

- •Пример доступа к глобальной памяти

- •Пример доступа к глобальной памяти

- •Пример доступа к глобальной памяти

- •Рекомендации по эффективной работе с глобальной памятью

- •Пример

- •Работа с разделяемой памятью

- •Работа с разделяемой памятью

- •Пример

- •Динамически выделяемая разделяемая память

- •Пример

- •Эффективная работа с разделяемой памятью

- •Эффективная работа с разделяемой памятью

- •Доступ к разделяемой памяти без конфликтов банков

- •Доступ к разделяемой памяти с конфликтами банков

- •Пример: параллельная редукция

- •Постановка задачи

- •Иерархическое суммирование

- •Вариант 1

- •Вариант 1

- •Вариант 2

- •Вариант 2

- •Вариант 3

- •Вариант 3

- •Вариант 4

- •Вариант 4

- •Вариант 5

- •Результаты

- •Материалы

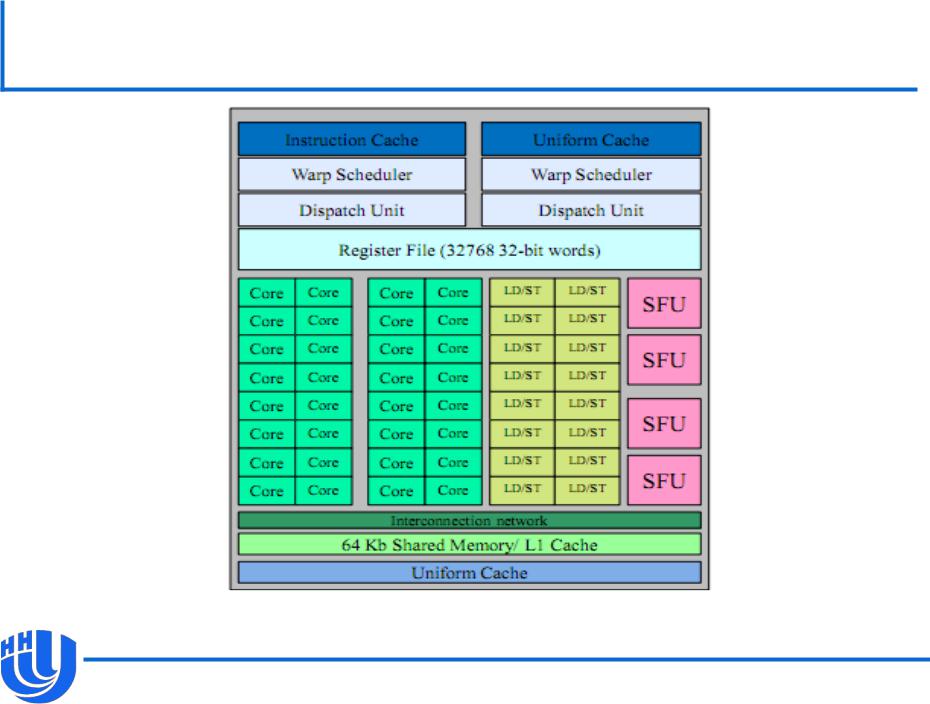

Мультипроцессор Fermi

[А.В. Боресков, А.А. Харламов «Архитектура и программирование массивно- параллельных вычислительных систем»

Н. Новгород, 2012 г. |

Исполнение потоков. Иерархия памяти |

11 |

Архитектура Fermi

Новейшая на текущий момент архитектура NVIDIA.

Добавлен общий L2-кэш для глобальной памяти.

На каждом мультипроцессоре добавлен L1-кэш для глобальной памяти. Физически расположен вместе с разделяемой памятью, возможность настройки размеров L1-кэша и разделяемой памяти 48kB/16kB.

В каждом ядре отдельные блоки для вычислений с плавающей точкой и целочисленных вычислений.

Значительно улучшена производительность арифметики с плавающей точкой двойной точности и SFU.

Техническая возможность для полной поддержки C++.

Н. Новгород, 2012 г. |

Исполнение потоков. Иерархия памяти |

12 |

Вычислительные возможности

Вычислительные возможности (compute capability) служат для классификации устройств по качественным архитектурным особенностям.

Определяются при помощи числового индекса, состоящего из номеров главной (major) и второстепенной (minor) ревизий, записывается в виде major.minor.

–Например, 1.3.

Таблица вычислительных возможностей (а также числа мультипроцессоров и CUDA-ядер) всех устройств в Appendix A в NVIDIA CUDA C Programming Guide.

Архитектура Fermi имеет номер главной ревизии 2 (индекс имеет вид 2.x), все более ранние архитектуры имеют номер главной ревизии 1 (индекс имеет вид 1.x).

Н. Новгород, 2012 г. |

Исполнение потоков. Иерархия памяти |

13 |

Вычислительные возможности

Отличия устройств с различными вычислительными возможностями в Appendix G в NVIDIA CUDA C Programming Guide.

Минимальный индекс 1.0.

Поддержка вычислений с плавающей точкой в двойной точности, начиная с индекса 1.3.

Поддержка классов (C++), начиная с индекса 2.0.

Полная поддержка С++ на устройствах индекса 2.0 и выше, начиная с версии CUDA 4.0.

От вычислительных возможностей существенно зависят требования для эффективного доступа к глобальной памяти и возможность выполнения специфических

операций.

Н. Новгород, 2012 г. |

Исполнение потоков. Иерархия памяти |

14 |

Исполнение потоков

Н. Новгород, 2012 г. |

Исполнение потоков. Иерархия памяти |

15 |

Основные понятия

Большое количество потоков (thread) параллельно выполняют одну и ту же функцию – ядро (kernel).

–На Fermi одновременно может исполняться до 4 разных ядер. На более старых архитектурах одновременно может исполняться только 1 ядро.

Потоки группируются в блоки (thread blocks).

Каждый блок исполняется на одном мультипроцессоре, его потоки – на CUDA-ядрах данного мультипроцессора.

Блоки объединяются в решетку/сетку блоков (grid).

Ядро выполняется на решетке из блоков.

Размер блока и размер решетки блоков задается при вызове ядра.

Н. Новгород, 2012 г. |

Исполнение потоков. Иерархия памяти |

16 |

Взаимодействие потоков

Потоки внутри одного блока выполняются на одном мультипроцессоре, они способны взаимодействовать между собой посредством:

–разделяемой памяти ;

–точек синхронизации – барьерная синхронизация при вызове __syncthreads() в ядре.

Два потока из различных блоков могут взаимодействовать лишь через глобальную память.

Атомарные функции для разделяемой и глобальной памяти.

Н. Новгород, 2012 г. |

Исполнение потоков. Иерархия памяти |

17 |

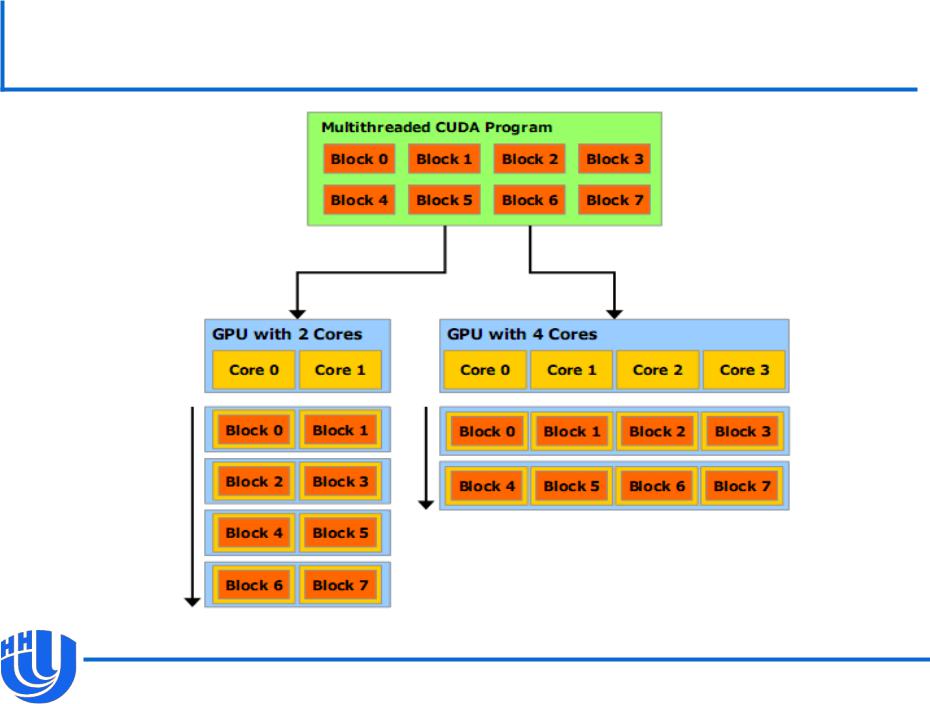

Выполнение блоков

Автоматическое распределение блоков на мультипроцессоры.

Каждый блок целиком выполняется одним мультипроцессором.

При наличии достаточного количества ресурсов, несколько блоков могут «одновременно» исполняться на одном мультипроцессоре.

Наличие большого количества блоков открывает возможности для автоматической масштабируемости с ростом числа мультипроцессоров.

Н. Новгород, 2012 г. |

Исполнение потоков. Иерархия памяти |

18 |

«Автоматическая масштабируемость»

[NVIDIA CUDA C Programming Guide v. 4.0]

Н. Новгород, 2012 г. |

Исполнение потоков. Иерархия памяти |

19 |

SIMT

Все потоки, выполняющиеся на одном мультипроцессоре, группируются в варпы (warp), в варп попадают потоки с последовательными идентификаторами.

–Размер варпа на текущих архитектурах равен 32.

Выполнение производится варпами, аппаратный планировшик на мультипроцессоре

–На Fermi 2 планировщика на мультипроцессор.

CUDA-ядра данного мультипроцессора параллельно выполняют одну и ту же инструкцию для всех потоков варпа (SIMT, Single Instruction Multiple Thread).

–Потоки одного варпа всегда синхронизованы.

Программирование в скалярных терминах (скалярный код для каждого потока, возможность ветвлений).

Н. Новгород, 2012 г. |

Исполнение потоков. Иерархия памяти |

20 |