- •Потоковые процессоры

- •Общие сведения

- •Альтернативные функции

- •Устройство портов

- •3.3.1.Регистр режима работы таймера/счетчика tmod

- •3.3.2.Регистр управления/статуса таймера tcon.

- •3.3.3.Режимы работы таймеров-счетчиков.

- •3.5.1.Функциональное назначение бит регистра управления/статуса приемопередатчика scon.

- •3.5.2.Скорость приема/передачи информации через последовательный порт.

- •3.5.3.Регистр управления мощностью pcon.

- •Вопрос #11 Контроллер прерываний msc-51. Особенности работы, программирование

- •3.6.1.Регистр масок прерывания (ie).

- •3.6.2.Регистр приоритетов прерываний (ip).

- •3.6.3.Выполнение подпрограммы прерывания.

- •Режим захвата.

- •Режим 16-разрядного программируемого таймера.

- •Режим скоростного вывода.

- •Режим сторожевого таймера (watchdog timer).

- •Режим генерации импульсов заданной скважности.

- •2.1.1 Центральный процессор (cpu)

- •2.1.2. Периферийные устройства 8xc196kc и 8xc196kd

- •1. Повышение тактовой частоты.

- •2. Увеличение объема и пропускной способности подсистемы памяти.

- •3. Увеличение количества параллельно работающих исполнительных устройств.

- •4. Системы на одном кристалле (SoC) и новые технологии.

- •Программные симуляторы.

- •Режим генерации импульсов заданной скважности. (Модуль pca как генератор шим)

- •Режим захвата.

- •Режим 16-разрядного программируемого таймера.

- •Режим скоростного вывода.

Вопрос #1 - “Назначение, состав, основные характеристики микроконтроллеров”

См. вопрос #6

Вопрос #2 - “Классификация микроконтроллеров”

Все МК можно условно разделить на три основных класса:

8-разрядные МК для встраиваемых приложений;

16- и 32-разрядные МК;

цифровые сигнальные процессоры (DSP).

8-разрядные МК обеспечивают реализацию алгоритмов управления в реальном масштабе времени, отличительные признаки: модульная организация (на базе одного процессорного ядра, различающийся объем и тип памяти программ, объем памяти данных, набор периферийных модулей, частота синхронизации); закрытая архитектура (отсутствие выводов шин адреса и данных на корпусе).

Цифровой сигнальный процессор (DSP) - специализированный процессор, предназначенный для цифровой обработки сигналов. Особенности: гарвардская архитектура, встроенная оперативная память (одновременная выборка нескольких машинных слов), аппаратная реализация сложных инструкций цифровой обработки сигналов (например, операция умножение с накоплением за 1 такт), вложенные циклы, довольно большая длина конвейера.

По архитектурам:

Архитектура фон Неймана - совместное хранение программ и данных в памяти компьютера (дешевле, но медленнее). В общем случае:

Гарвардская архитектура - программа и данные хранятся в различных устройствах памяти (в архитектуре фон Неймана для выборки команды и двух операндов требуется три такта, здесь два; в реальности, это время может быть сокращено до одного такта).

Вопрос #3 - “Тенденции развития архитектуры”

См. вопрос #24

Вопрос #5 - “Обзор микропроцессоров управления потоками событий”

С точки зрения организации обмена командами между процессором и памятью все компьютеры можно разделить на четыре класса:

SISD (Single Instruction Single Data) — «один поток команд, один поток данных»»;

SIMD (Single Instruction Multiply Data) — один поток команд, много потоков данных;

MISD (Multiple Instruction Single Data) — много потоков команд, один поток данных;

MIMD (Multiple Instruction Multiple Data) — много потоков команд, много потоков данных.

Из этой классификации видно, что фон-неймановская машина является частным случаем, попадающим в категорию SISD. Возможные усовершенствования в рамках архитектуры SISD ограничиваются включением в нее конвейеров и других дополнительных функциональных узлов, а также использованием разных методов кэширования. Две другие категории архитектур (SIMD, в которую входят векторные процессоры, и конвейерные архитектуры MISD) были реализованы в нескольких проектах, но не стали массовыми. Если оставаться в рамках этой классификации, то единственной возможностью преодоления ограничений «бутылочного горла» остается развитие архитектур класса MIMD. В их рамках обнаруживается множество подходов: это могут быть и различные параллельные и кластерные архитектуры, и многопотоковые процессоры.

В самом общем виде многопотоковый процессор состоит из двух типов примитивов. Первый тип — это ресурс, поддерживающий исполнение потока, который называют mutex (от Mutual Exclusion — «взаимное исключение»), а второй — события. То, как физически реализован тот или иной mutex, зависит от выбранной схемы — SMT или CMP. В любом случае выполнение процесса сводится к тому, что очередной поток захватываает mutex на время своего исполнения, а затем освобождает его. Если mutex занят одним потоком, то второй поток не может его заполучить. Конкретная процедура передачи полномочий на обладание mutex от одного потока другому может иметь случайный характер; она зависит от реализации управления, например, в определенной операционной системе. В любом случае управление должно быть построено так, чтобы ресурсы, состоящие из mutex, распределялись корректно и подавлялся эффект неопределенности.

События — это объекты (event), сигнализирующие о об изменении во внешней среде. Они могут переводить себя в режим ожидания до наступления иного события или сообщать о своем состоянии другому событию. Таким способом события могут взаимодействовать между собой, и при этом должна обеспечиваться преемственность данных между событиями. Ожидающий исполнения агент необходимо информировать о готовности данных для него. И как в распределении mutex должен подавляться эффект неопределенности, так при работе с событиями должен подавляться эффект неизвестности. Впервые схема SMT была реализована в процессорах Compaq Alpha 21464, а также в Intel Xeon MP и Itanium

Нет достаточных оснований для однозначного утверждения о преимуществах CMP по сравнению с SMT. Опыт создания процессоров, реализующих SMT, является гораздо большим: начиная с середины 80-х годов созданы несколько десятков экспериментальных изделий и несколько серийных процессоров. История развития CPM пока короткая: если не учитывать семейство специализированных сигнальных процессоров Texas Instruments TMS 320C8x, то первым успешным проектом стал Hydra, выполненный в Стэндфордском университете. Среди университетских исследовательских проектов, нацеленных на построение CMP-процессоров, известны еще три — Wisconsin Multiscalar, Carnegie-Mellon Stampede и MIT M-machine.

Кристалл Hydra состоит из четырех процессорных ядер на основе известной RISC-архитектуры MIPS . Каждое ядро имеет кэш-память команд и кэш-память данных, а все ядра объединены в общую кэш-память второго уровня. Процессоры выполняют обычный набор команд MIPS плюс команды условного хранения (Store Conditional или SC), предназначенные для реализации синхронизационных примитивов. Процессоры и кэш-память второго уровня объединяются шинами чтения/записи, а кроме того, есть вспомогательные адресные и управляющие шины. Все эти шины являются виртуальными, то есть логически представляются проводными шинами, а физически разделены на множество сегментов, использующих повторители, и буферов, что позволяет повысить скорость работы ядер.

Niagara — «сплав» MAJC и Hydra

У процессора UltraSPARC T1, более известного как Niagara, два основных предшественника — Hydra и MAJC.

В середине 90-х годов, на волне увлечения специализированными Java-процессорами, в Sun Microsystems была предпринята попытка создания процессора «с очень длинным словом» — Very Long Instruction Word (VLIW). Эта инициатива получила название MAJC (Microprocessor Architecture for Java Computing). Как и в других проектах, стартовавших в то время (Intel IA-64 Itanium), в данном случае ставилась задача переноса некоторых из самых сложных операций в ведение компилятора. Освободившуюся транзисторную логику можно использовать для создания более производительных функциональных узлов (functional units), с тем чтобы обеспечить продуктивный обмен командами и данными между CPU, кэш-памятью и основной памятью. Таким образом, преодолевалось фон-неймановское «бутылочное горло».

MAJC отличался от большинства процессоров отсутствием специализированных сопроцессоров (subprocessors), которые обычно называют функциональными устройствами, предназначенными для выполнения операций с целыми числами, числами с плавающей точкой и мультимедийными данными. В нем все функциональные устройства были одинаковыми, способными к выполнению любых операций, что, с одной стороны, снижало эффективность выполнения отдельных операций, но с другой повышало коэффициент использования всего процессора.

Niagara воплощает в себе лучшее из двух альтернативных подходов к реализации многопотоковости — SMT и CMP. На первый взгляд, он очень похож на Hydra, но скорее Hydra можно назвать «макетом» Niagara. Помимо того что в последнем — вдвое больше ядер, каждое из них может обрабатывать четыре потока.

Собственный подход к созданию многоядерных процессоров предложила корпорация IBM, чей проект Cell назван «гетерогенным мультипроцессорным чипом» (heterogeneous chip multiprocessor). Архитектуру Cell именуют еще и Cell Broadband Engine Architecture (CBEA). Мультипроцессор Cell состоит из ядра IBM 64-bit Power Architecture и восьми специализированных сопроцессоров, реализующих схему «одна команда много данных». В компании IBM эту архитектуру называют Synergistic Processor Unit (SPU).

Потоковые процессоры

Потоковыми называют процессора, в основе работы кото-рых лежит принцип обработки многих данных с помощью одной команды. Согласно классификации Флинна они принадлежат к SIMD архитектуре. Технология SIMD позволяет выполнять одно и то же действие, например вычитание и сложение, над несколькими наборами чисел одновременно. SIMD-операции для чисел двойной точности с плавающей запятой ускоряют работу ресурсоемких приложений для создания контента, трехмерного рендеринга, фи-нансовых расчетов и научных задач. Кроме того, усовершенство-ваны возможности 64-разрядной технологии MMX (целочислен-ных SIMD-команд); эта технология распространена на 128-разрядные числа, что позволяет ускорить обработку видео, речи, шифрование, обработку изображений и фотографий. Потоковый процессор повышает общую производительность, что особенно важно при работе с 3D-графическими объектами.

Может быть отдельный потоковый процессор (Single-streaming processor — SSP) и многопотоковый процессор (Multi-Streaming Processor - MSP).

Ярким представителем потоковых процессоров является семейство процессоров Intel, начиная с Pentium III, в основе рабо-ты которых лежит технология Streaming SIMD Extensions (SSE, потоковая обработка по принципу "одна команда - много дан-ных"). Эта технология позволяет выполнять такие сложные и не-обходимые в век Internet задачи, как обработка речи, кодирование и декодирование видео- и аудиоданных, разработка трехмерной графики и обработка изображений.

Бесспорными представителями класса SIMD считаются матрицы процессоров: ILLIAC IV, ICL DAP, Goodyear Aerospace MPP, Connection Machine 1 и т.п. В таких системах единое управ-ляющее устройство контролирует множество процессорных эле-ментов. Каждый процессорный элемент получает от устройства управления в каждый фиксированный момент времени одинако-вую команду и выполняет ее над своими локальными данными.

Другими представителями SIMD-класса являются вектор-ные процессоры, в основе которых лежит векторная обработкаданных. Векторная обработка увеличивает производительность процессора за счет того, что обработка целого набора данных (век-тора) производится одной командой. Векторные компьютеры ма-нипулируют массивами сходных данных подобно тому, как ска-лярные машины обрабатывают отдельные элементы таких масси-вов. В этом случае каждый элемент вектора надо рассматривать как отдельный элемент потока данных. При работе в векторном режиме векторные процессоры обрабатывают данные практически параллельно, что делает их в несколько раз более быстрыми, чем при работе в скалярном режиме. Максимальная скорость передача данных в векторном формате может составлять 64 Гб/с, что на 2 порядка быстрее, чем в скалярных машинах. Примерами систем подобного типа является, например, процессоры фирм NEC и Hitachi

Вопрос #6 – “Архитектура однокристальных микро-ЭВМ семейства МСS-51”

МК i8051АН: CPU MCS-51, память программ 4096 байт, память данных 128 байт, 4 параллельных 8-x порта I/O, 2 16-x таймера, последовательный порт, внутренняя 8-x магистраль, гарвардская архитектура (см. вопрос 2), макс. размер адресного пространства каждого типа памяти – 64К, открытая архитектура.

Процессор.

Устройство управления (УУ) вырабатывает управляющие сигналы, поступающие по шинам инструкций во все блоки машины.

Арифметико-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций преобразования информации. АЛУ обычно состоит из двух регистров, сумматора и схем управления. Сумматор - выполняет сложение поступающих на вход двоичных кодов. Регистры - быстродействующие ячейки памяти различной длины. Схемы управления принимают по шине инструкций управляющие сигналы от УУ и преобразуют их в сигналы для управления работой регистров и сумматора. АЛУ выполняет арифметические операции (+, -, *,:) только над целыми двоичными числами.

Интерфейсная часть микропроцессора.

Узел формирования адреса - устройство, вычисляющее полный адрес ячейки памяти.

Шины данных, адреса и инструкций. УУ формирует управляющие сигналы для:

выбора из регистра-счетчика адреса команды ячейки ОЗУ очередной команды программы;

выбора из ячеек ОЗУ очередной команды и приема в регистр команд;

расшифровки кода операции;

считывания из ячеек ПЗУ микропрограмм управляющих сигналов, определяющих процедуры выполнения заданной операции, и пересылки управляющих сигналов в эти блоки;

считывания из регистров адресов операндов, выборки операндов и выполнения операции обработки;

записи результатов в память.

Порты ввода/вывода. Через них МП обменивается информацией с другими устройствами. Каждый порт имеет номер, соответствующий адресу ячейки памяти, являющейся частью устройства ввода-вывода, использующего этот порт. Порт содержит аппаратуру сопряжения и два регистра памяти - для обмена данными и управляющей информацией.

Схема управления шиной и портами выполняет следующие функции:

формирование адреса порта и управляющей информации;

прием от порта информации: управляющей, о готовности порта, о состоянии;

организацию канала для передачи данных между портом и МП.

Вопрос #7 – “Организация внутренней и внешней памяти МС8-51”

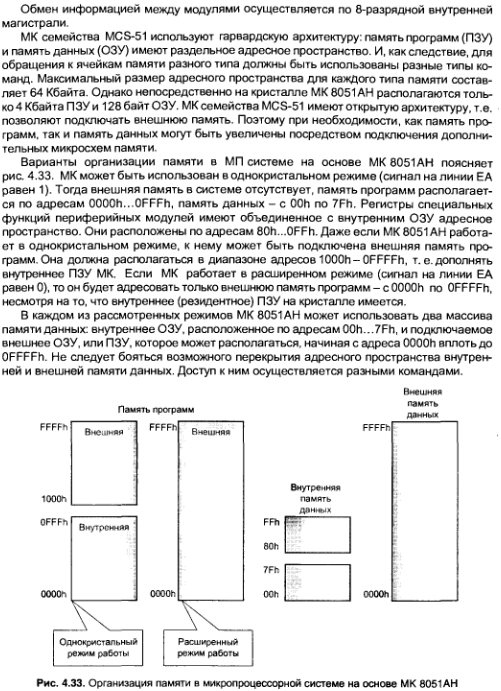

В архитектуре семейства 8051 память программ и память данных разделены (гарвардская архитектура). Каждая из них имеет размер 64 Кбайта, вы* бор одной из двух матриц памяти осуществляется сигналами PSEN, RD#, WR#. Организация памяти в микроконтроллерах семейства 8051 иллюстрируется рис. 2.3. Память программ может быть целиком внешней (сигнал ЕА = 0), либо при обращении по младшим 4К адресов код извлекается из ячеек внутренней памяти микроконтроллера, а содержимое старших 60К берется из внешней памяти системы (сигнал ЕА =1). Микроконтроллеры 8751Ы имеют бит секретности, предназначенный для защиты внутренней памяти программ от доступа извне. Значение этого бита программируется один раз, очищен он может быть только при полном стирании всей внутренней памяти программ. При установленном бите секретности запрещается не только чтение внутренней памяти извне, но и ее допрограммирование, а также ступают на внешние адресные выводы. В режиме 64К содержимое (ЕРС) принимает фиксированное значение 0FFH, поэтому все команды выбираются со страницы 0FH. Внутреннее ПЗУ программ в модели 83C196NP, размещенное на странице 0FH (адреса 0F2080H..0F2FFFH), выбирается при значении внешнего сигнала ЕА = 1. Это же ПЗУ может выбираться со страницы ООН (адреса 2080H..2FFFH), если в регистре реконфигурации CCR1 установлено значение бита REMAP = 1.

О бращение

к внешней памяти программ. Механизм

программирования и верификации внутренней

памяти программ здесь рассматриваться

не будет, поскольку в продаже имеются

программаторы различных типов и

стоимости. Это позволяет разработчику

сосредоточиться на решении основной

задачи. Универсальный профессиональный

программатор KROM описан в гл. 4.

бращение

к внешней памяти программ. Механизм

программирования и верификации внутренней

памяти программ здесь рассматриваться

не будет, поскольку в продаже имеются

программаторы различных типов и

стоимости. Это позволяет разработчику

сосредоточиться на решении основной

задачи. Универсальный профессиональный

программатор KROM описан в гл. 4.

Память данных делится на внешнюю и внутреннюю, каждая из них имеет свое пространство адресов. В архитектуре MCS-51 пространство адресов внутренней -памяти данных объединяет все внутренние программно доступные i ресурсы. Это пространство размером 256 байт в свою очередь делится на пространство адресов внутреннего ОЗУ (размером 128 байт) и пространство адресов регистров специальных функций. Область внутреннего ОЗУ изображена на рис. 2.4, ячейки области занимают младшие адреса внутренней памяти данных с ООН по 7FH. В этой области памяти выделяются два фрагмента:

♦ младшие 32 адреса занимают четыре регистровых банка, каждый из кото-рых содержит по восемь регистров общего назначения R0..R7. Текущий банк определяется значением битов RSO, RS1 регистра PSW. Таким образом, младшие 32 ячейки ОЗУ, кроме адресов, имеют имена;

♦ ячейки с адресами в диапазоне 32..48 имеют прямо адресуемые биты, адреса битов этой части ОЗУ находятся в диапазоне 00H..7FH.

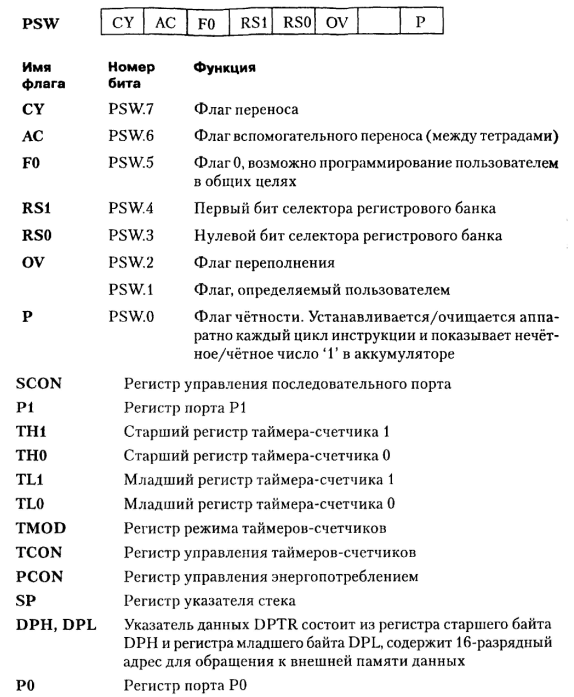

На рис, 2.5 изображена область регистров специальных функций. В нее включены все программно доступные регистры (управления и данных) внутреннихблоков ввода-вывода.

Эта область формально занимает старшие 128 байт внутренней памяти данных, но обращение должно осуществляться по определенным адресам ячеек или отдельных битов. Обращение по промежуточным адресам приведет к ошибочному результату. Все регистры имеют как символические имена, так и адреса в качестве ячеек внутренней памяти. Часть регистров содержит прямо адресуемые биты. Адреса битов находятся в диапазоне 80H..F7H. Назначение регистров специальных функций следующее:

Формат всех регистров специальных функций будет рассмотрен в разделах, посвященных описанию системы прерываний и функций отдельных блоков ввода-вывода. Здесь приведен формат регистра PSW, хранящего слово состояния процессора. Этот регистр вместе с аккумулятором содержит результат выполнения команд.

Формат всех регистров специальных функций будет рассмотрен в разделах, посвященных описанию системы прерываний и функций отдельных блоков ввода-вывода. Здесь приведен формат регистра PSW, хранящего слово состояния процессора. Этот регистр вместе с аккумулятором содержит результат выполнения команд.

Вопрос #8 – “Порты ввода-вывода МС8-51. Особенности работы, программирование.”