- •§3. Операционные элементы

- •1.Комбинационные ОЭ (без памяти)

- •Пример: десятично-двоичный coder

- •Простейшая схема на элементах ИЛИ

- •• дешифратор

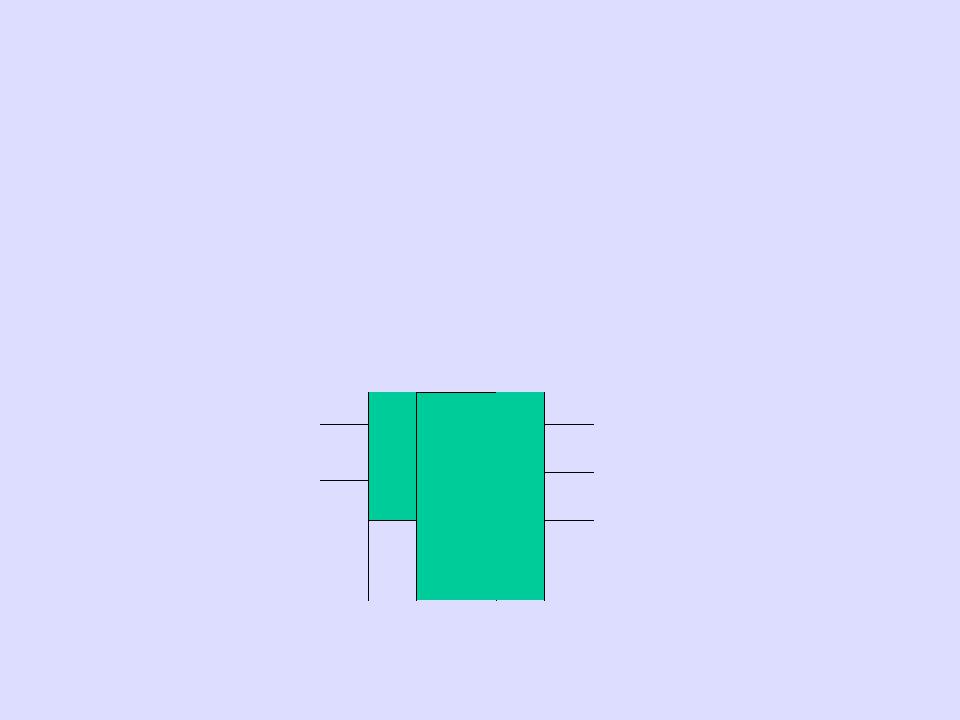

- •Пример: 2-х разрядный decoder

- •б) Коммутаторы

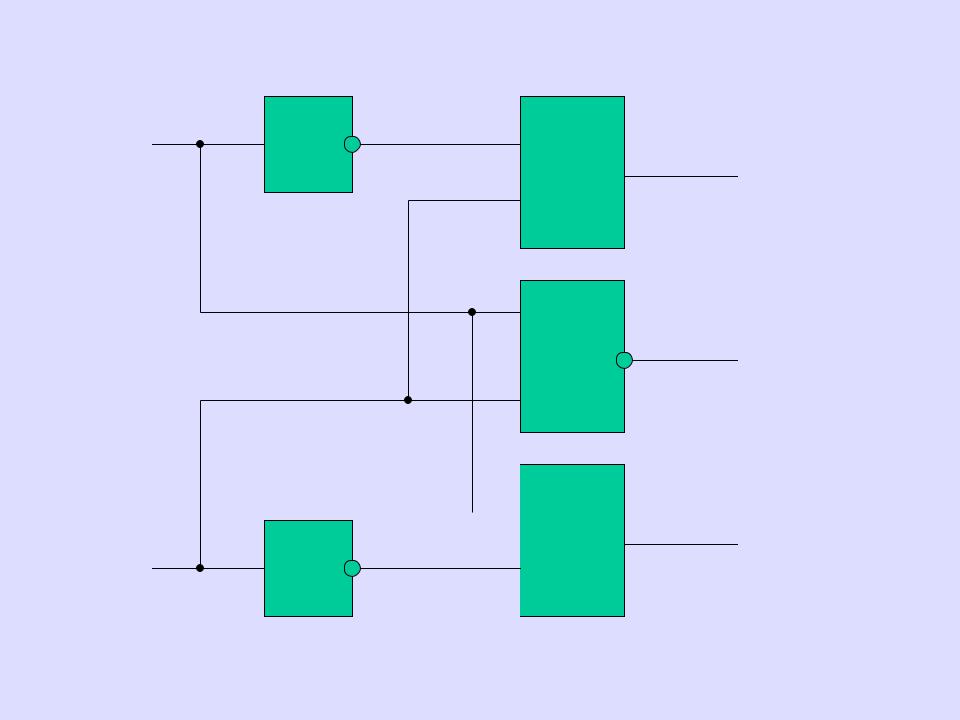

- •• демультиплексор

- •в) Арифметические устройства

- •• сумматор

- •Одноразрядный сумматор с переносом

- •2. Триггеры

- •Устойчивость вызвана наличием обратных связей – выход одного замыкается на

- •R – reset

- •в) Триггер переключается только при определённых комбинациях входных сигналов.

- •* – оба выходных сигнала

- •У RS-триггера есть четыре режима работы:

- •RS-триггер является базовым элементом ЛУ

- •г) Триггеры без запрещённых комбинаций

- •д) Синхронизация

- •Синхронизация

- •3. Последовательностные ОЭ

- •• параллельный RG – триггеры не зависят друг от друга

- •Используются в кэшах

- •• последовательный RG – выход каждого триггера идёт на вход следующего

- •Фронт делают узким настолько, чтобы сигнал

- •Каждый синхроимпульс сдвигает код числа на один разряд

- •Для записи N-разрядного числа нужно N тактов.

- •А для чтения достаточно одного такта!

- •• универсальный RG – может записывать и выдавать

- •Вывод:

- •б) Счётчик – запоминает кол-во Nf пришедших

- •§4. Микросхемы памяти

- •Сравнение:

- •Для ППЗУ также указывают

- •2) Физика элементов памяти (ЭП)

- •Электрические элементы

- •Магниторезистивные элементы и чипы

- •Фазопеременные элементы и чипы

- •Оптические элементы:

- •64 слова по

- •Память ЭВМ приблизилась по

- •3) Организация МП

- •Страница – область памяти фиксированного размера (н-р, 4 Кбайт, 2, 4 Мбайт)

- •б) Физическая

- •• Адрес ЭП вычисляется контроллером памяти и

- •• адреса строк и столбцов подаются на дешифраторы

- •• режимы работы ЭП

- •Банк – чип (группа чипов), использующий всю ширину шины данных

§3. Операционные элементы

(ОЭ)

ОЭ – ЛУ, выполняющие не элементарные операции.

Н-р, сумматоры, счётчики, …

1.Комбинационные ОЭ (без памяти)

а) Преобразователи кодов

• шифратор

преобразует сигнал на одном из n входов в m- разрядный выходной код

Пример: десятично-двоичный coder

x0

x9

|

0 |

CD |

|

|

y0 |

|

|

||||

|

1 |

|

1 |

|

|

|

|

|

|||

|

2 |

|

|

||

|

|

|

|||

|

|||||

|

3 |

|

2 |

|

|

|

|

|

|

||

|

4 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

5 |

|

4 |

|

|

|

|

|

|

||

|

6 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

7 |

|

8 |

|

y3 |

|

|

|

|||

|

9 |

|

|

||

|

8 |

|

|

веса |

|

|

|

|

|

||

|

|

|

|

||

Простейшая схема на элементах ИЛИ

1 20

1 21

1 22

|

|

|

23 |

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 2 3 4 5 6 7 8 9

• дешифратор

преобразует n-разрядный входной код в сигнал только на одном из m выходов

m 2n

Пример: 2-х разрядный decoder

|

|

|

|

y0 |

x0 |

|

DC |

||

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x1 |

|

|

|

y3 |

|

|

|

||

|

|

|

||

|

|

|

|

|

|

|

|

б) Коммутаторы

• мультиплексор

пропускает сигнал только с одного из указанных входов

n входов адреса

MX

MX

2n информ. входов

• демультиплексор

посылает входной сигнал на указанный выход

A0 DMX y0

A1

x

y3

y3

в) Арифметические устройства

• компаратор |

A |

|

|

|

A<B |

||

== |

|||||||

|

|||||||

|

|

|

|

|

|

A=B |

|

|

|

|

|

|

|

||

|

B |

|

|

|

A>B |

||

|

|

|

|

||||

Сравнивает два числа. Результат

отображается лог. 1 на одном из трёх выходов.

A

B

&

YA<B

M2

YA=B

&

&

YA>B