_23Л_Сумматоры и АЛУ

.doc1. Арифметические операции над двоичными числами

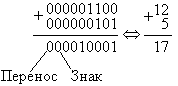

1.1. Сложение положительных двоичных чисел выполняется в обычном двоичном коде, называемым прямым кодом. Один или два старших разряда используются для знака числа. Рассмотрим на примере восьми битного числа с двумя знаковыми разрядами. Использование для представления знака числа двух бит предоставляет интересную возможность контролировать переполнение при выполнении арифметических операций. Рассмотрим несколько примеров.

Просуммируем числа A=12 и B=5. Для выполнения этой операции в АЛУ надо со входов мультиплексоров передать числа A и B без изменения в сумматор, на выходе S, которого получим результат.

В результате суммирования получается правильный результат. Это можно проконтролировать по старшему разряду знака (флагу переноса C), который совпадает со вторым знаковым разрядом (знаком результата).

Просуммируем числа 100 и 31

В этом примере видно, что в результате суммирования произошло переполнение восьмибитовой переменной, т.к. в результате операции над положительными числами получился отрицательный результат. Однако если рассмотреть флаг переноса, то он не совпадает со знаком результата. Эта ситуации является признаком переполнения результата и легко обнаруживается при помощи операции "исключающее ИЛИ" над старшим битом результата и флагом переноса C. Большинство процессоров осуществляют эту операцию аппаратно и помещают результат во флаг переполнения OV.

1.2. Сложение отрицательных двоичных чисел выполняется в дополнительном коде. В нем операции с отрицательными числами выполняются аналогично операциям с положительными числами.

Просуммируем два отрицательных числа -12 и -5. Чтобы представить отрицательное число в дополнительном коде, надо представить его в прямом коде с нулевыми знаковыми разрядами как в предыдущем примере. После этого надо инвертировать все разряды кода и прибавить единицу младшего разряда. Получим значения A и B, приведенные ниже и просуммируем их.

В примере флаг переноса C тоже совпадает со знаком результата, то есть переполнения не произошло и в этом случае.

1.3. Сложение положительного и отрицательного двоичных чисел ничем не отличается от предыдущих операций. Просуммируем положительное и отрицательное число -12 и +5.

В этом примере при суммировании положительного и отрицательного числа автоматически получается правильный знак результата. В данном случае знак результата отрицательный. Флаг переноса совпадает со знаком результата, поэтому переполнения не было.

2. Сумматоры

Сумматоры выполняют арифметическую операцию сложения двух чисел. Они имеют как самостоятельное значение, так и являются составной частью арифметическо-логического устройства (АЛУ) микропроцессора. При организации различных вычислительных процессов суммированию отводится главная роль, оно является основной операцией. Например, вычитание - это суммирование с использованием дополнительного либо обратного кода, умножение сводится к сдвигу и сложению (суммированию) двоичных чисел. Следует отметить, что сумматоры являются логическими устройствами, функционируют по законам алгебры логики, но выполняют операцию арифметического, а не логического сложения.

Рис. 1. Обозначение сумматора на функциональных схемах

По выполняемым функциям различают: полусумматоры, одноразрядные сумматоры, многоразрядные сумматоры.

На основе сумматоров строятся арифметико-логические устройства (АЛУ).

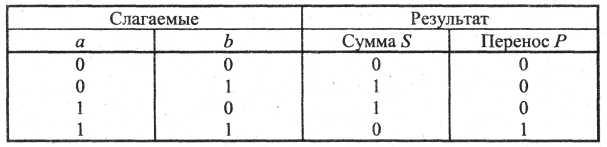

2.1. Одноразрядный полусумматор

В сумматорах операция суммирования чисел, представленных в двоичном коде, осуществляется поразрядно.

Таблица истинности полусумматора

На основании этой таблицы выражение для S является функцией двух переменных СЛОЖЕНИЕ ПО МОДУЛЮ 2 (ИСКЛЮЧАЮЩЕЕ-ИЛИ), а для переноса Р – просто функцией совпадения И:

![]()

![]()

Используя представление в базисе И-НЕ, из таблицы истинности получим

![]() .

.

Техническая реализация полусумматора представлена на рис.2.

Рис. 2

Полусумматор (рис. 2) не имеет входа переноса с предыдущего разряда, поэтому его можно использовать только в младших разрядах устройства обработки многоразрядных двоичных слов.

Полный одноразрядный сумматор можно построить из двух полусумматоров (рис. 3).

Рис. 3

Полные одноразрядные сумматоры являются основой, из которых получают различные схемы многоразрядных сумматоров.

2.2. Многоразрядные сумматоры

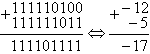

Сумматор параллельного действия содержит одноразрядные сумматоры, число которых равно разрядности суммируемых двоичных слов (рис. 4).

Разряды двоичных слов поступают на соответствующие одноразрядные сумматоры. Каждый одноразрядный сумматор формирует выходы суммы S1-S4 и выходы переноса Р. Перенос передается на вход следующего одноразрядного сумматора более старшего разряда. По цепям переноса сумматоры соединены последовательно. Импульс переноса в каждом сумматоре формируется после того, как будет сформирован и поступит на сумматор перенос из предыдущего разряда. Поэтому быстродействие такого параллельного сумматора с последовательным переносом невысокое. В наихудшем случае перенос может последовательно пройти все сумматоры. Общая задержка сигнала

![]()

где τ1 — задержка распространения в одном сумматоре.

Рис. 4

Повышение быстродействия достигается применением специальных схем сквозного или параллельного формирования переноса.

В результате задержки сигналов в логических элементах и неодновременного прихода сигналов на входы a, b, p сумматоров (задержка переноса) выходной код суммы может принимать в течение коротких интервалов времени ложные значения, не соответствующие входным суммируемым кодам.

Для того, чтобы избежать неопределенных состояний, применяют синхронизирование или стробирование выходных сигналов.

3. Арифметико-логические устройства

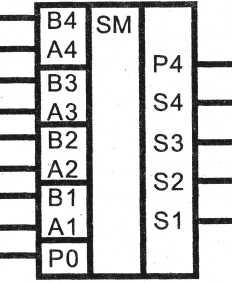

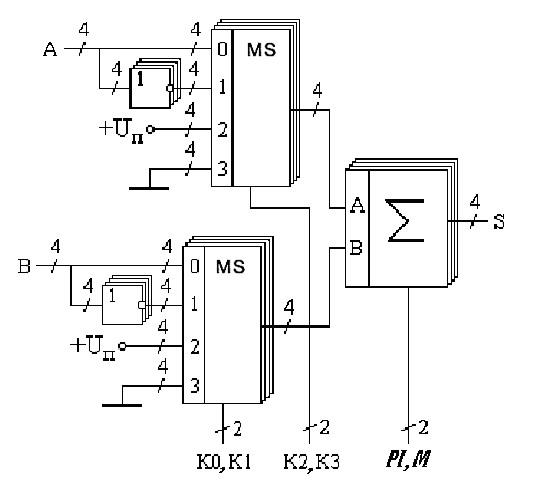

Для организации функционирования вычислительного устройства кроме операций сложения необходимо реализовать целый ряд арифметических и логических операций: вычитание, инверсия знака, инкремент, декремент, сдвиг и т.д. Устройство реализующее весь набор арифметических и логических операций в процессоре называется арифметико-логическим устройством (АЛУ). Оно может быть реализовано на основе управляемого сумматора, двух многоразрядных инверторов и двух мультиплексоров. Типовая структура АЛУ приведена на рис.5.

Рис.5. Структурная схема арифметического устройства.

В этой схеме арифметические операнды передаются через две группы четырёхвходовых коммутаторов (мультиплексоров). На входы мультиплексоров поступают прямые и инверсные значения разрядов чисел-операндов, а так же логический ноль и логическая единица. Этот набор необходим для выполнения различных операций над числами. Прямой и инверсный операнды используются для реализации арифметического сложения или вычитания. С помощью логических нулей и единиц, можно выполнять операции инкремента, декремента, формирования нуля, единицы и минус единицы на выходе АЛУ.

Управление АЛУ осуществляется с помощью адресных входов MS: К0, К1 - первой группы мультиплексоров и К2, К3 – второй группы. Подавая разные коды на эти входы можно задавать различные операции, выполняемые АЛУ. Для расширения числа возможных операций можно воспользоваться входом переноса PI, имеющимся в сумматоре.

Кроме арифметических операций АЛУ может выполнять поразрядные логические операции, если в сумматор ввести дополнительные элементы способные запрещать и изменять межразрядные переносы внутри сумматора. Управление межразрядными переносами производится по специальному входу M.