- •2. Сравнительная оценка базовых логических элементов

- •4. Типы корпусов микросхем

- •5. Условное графическое обозначение микросхем

- •6. Основы булевой алгебры

- •7. Аксиомы и законы булевой алгебры

- •8. Формы представления логических функций

- •12. Карты Карно для двух, трех, четырех и пяти переменных. Порядок минимизации функций с помощью карт Карно. Примеры минимизации

- •17. Комбинационные устройства: определение, методика проектирования

- •18. Шифраторы

- •19. Дешифратор

- •22, Преобразователи кодов

- •24, Мультиплексоры

- •25. Мультиплексорное дерево

- •27. Демультиплексоры

- •28. Сумматоры и полусумматоры

- •31. Многоразрядные двоичные сумматоры

- •33. Двоичные компараторы

- •35. Мажоритарный элемент

- •36. Программируемые логические матрицы

- •40. Реализация шифраторов, дешифраторов, мультиплексоров и демультиплексоров на плм

- •43. Последовательностные устройства: определение, основные типы устройств, методика проектирования

- •44. Триггеры

- •45. Классификация триггеров по функциональному назначению

- •46. Регистры

- •47. Регистры хранения

- •48. Регистры сдвига

- •49. Счетчики

- •50. Последовательные счетчики

- •51. Параллельные счетчики

- •52. Вычитающий и реверсивный счетчик

- •53. Декадный счетчик

- •64) Постоянные запоминающие устройства

- •65) Увеличение объема памяти запоминающих устройств

- •66) Назначение цап и ацп

- •67) Основные характеристики цап и ацп

- •68) Цап с матрицей взвешенных резисторов

- •69) Цап с матрицей r-2r

- •71) Области применения цап

- •72) Ацп времяимпульсного типа

- •73) Ацп с двойным интегрированием

- •74) Ацп параллельного преобразования (прямого преобразования)

- •75) Ацп последовательного счета (развертывающего типа)

- •76) Ацп следящего типа

- •77) Ацп последовательного приближения (поразрядного уравновешивания)

- •78) Области применения ацп

- •79) Схема выборки и хранения

- •85) Общая структура и принципы функционирования микропроцессорных систем

- •91. Способы адресации операндов. Особенности способов адресации.

- •92. Формат типовой команды микропроцессора. Одноадресные, двухадресные, и трехадресные команды. Классификация групп операций микропроцессора.

- •93. Команды пересылки. Команды арифметических и логических операций.

- •94. Команды сдвига. Команды сравнения и тестирования. Команды управления процессором.

- •95. Команды битовых операций. Операции управления программой.

- •96. Структурная схема, физический интерфейс и условное графическое обозначение однокристального микроконтроллера (мк) к1816ве48.

- •97) Структурная организация центрального процессора мк к1816ве48.

- •98) Организация памяти программ и данных мк к1816ве48.

- •99) Организация системы ввода-вывода мк к1816ве48.

- •100) Организация систем подсчета времени, прерываний и синхронизации мк к1816ве48.

- •101) Средства расширения памяти программ мк к1816ве48: интерфейс, схе-мы подключения, временные диаграммы.

- •102) Средства расширения памяти данных мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

- •103) Средства расширения ввода-вывода мк к1816ве48: интерфейс, схемы подключения, временные диаграммы.

45. Классификация триггеров по функциональному назначению

RS-триггер

имеет два управляющих входа

и

и ,

с помощью которых выполняются функции

установки триггера в состояние

,

с помощью которых выполняются функции

установки триггера в состояние (при

(при ,

, )

и сброса в состояние

)

и сброса в состояние (при

(при ,

, ).

При

).

При триггер работает в режиме хранения,

т.е. сохраняет ранее установленное

состояние:

триггер работает в режиме хранения,

т.е. сохраняет ранее установленное

состояние: либо

либо .

Комбинация входных переменных

.

Комбинация входных переменных (установка и сброс одновременно) являетсязапрещенной,

так как может привести к неопределенному

(непредсказуемому) состоянию выхода

(установка и сброс одновременно) являетсязапрещенной,

так как может привести к неопределенному

(непредсказуемому) состоянию выхода

.

Во избежание возникновения сбоев в

цифровых системах комбинацию

.

Во избежание возникновения сбоев в

цифровых системах комбинацию исключают, поэтому она являетсянереализуемой.

Полная таблица состояний 3.1 представляет

собой табличное описание функционирования

RS-триггера.

Нереализуемая комбинация входных

переменных

исключают, поэтому она являетсянереализуемой.

Полная таблица состояний 3.1 представляет

собой табличное описание функционирования

RS-триггера.

Нереализуемая комбинация входных

переменных

дает два безразличных набора переменных

дает два безразличных набора переменных ,

, ,

, ,

для которых значение функции

,

для которых значение функции не определено. Минимизировав функцию

не определено. Минимизировав функцию ,

получим характеристическое уравнениеRS-триггера:

,

получим характеристическое уравнениеRS-триггера:

. (3.1)

Как видно из таблицы 3.1, при

. (3.1)

Как видно из таблицы 3.1, при (режим хранения) состояние выхода

триггера не изменяется:

(режим хранения) состояние выхода

триггера не изменяется: .

Поэтому полную таблицу состояний путем

объединения строк и исключения столбца

.

Поэтому полную таблицу состояний путем

объединения строк и исключения столбца можно преобразовать в более компактную

форму (таблица 3.2).RS-триггеры

могут быть асинхронными или синхронными,

синхронизируемые уровнем либо фронтом

синхросигнала.

можно преобразовать в более компактную

форму (таблица 3.2).RS-триггеры

могут быть асинхронными или синхронными,

синхронизируемые уровнем либо фронтом

синхросигнала.

Таблица 3.1 Таблица 3.2

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

| |

|

0 |

0 |

1 |

1 |

0 |

1 |

1 | |

|

0 |

1 |

0 |

1 |

1 |

0 |

0 | |

|

0 |

1 |

1 |

1 |

1 |

1 |

| |

|

1 |

0 |

0 |

0 | ||||

|

1 |

0 |

1 |

0 | ||||

|

1 |

1 |

0 |

| ||||

|

1 |

1 |

1 |

| ||||

JK-триггер

характеризуется таблицей состояний

3.3. Он отличается от RS-триггера

тем, что при поступлении на входы

комбинации

меняет состояние выхода на противоположное:

меняет состояние выхода на противоположное: .

Таким образом,JK-триггер

не имеет запрещенных комбинаций входных

сигналов, которые следовало бы исключать

при работе цифровых систем. Его

характеристическое уравнение имеет

вид

.

Таким образом,JK-триггер

не имеет запрещенных комбинаций входных

сигналов, которые следовало бы исключать

при работе цифровых систем. Его

характеристическое уравнение имеет

вид

. (3.2)

. (3.2)

|

|

|

|

|

0 |

0 |

|

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

|

Так

же как RS-триггер,

JK-триггер

может быть асинхронным, синхронизируемым

уровнем или фронтом. На практике обычно

используются JK-триггеры,

синхронизируемые фронтом. T-триггер,

называемый часто счетным

триггером,

характеризуется таблицей состояний

3.4. Состояние его выхода меняется на

противоположное при поступлении на

вход счетного сигнала

и сохраняется неизменным при

и сохраняется неизменным при .

В соответствии с таблицей 3.4

характеристическое уравнениеT-триггера

имеет вид

.

В соответствии с таблицей 3.4

характеристическое уравнениеT-триггера

имеет вид

. (3.3)

. (3.3)

Из

таблицы 3.3 видно, что при

состояниеJK-триггера,

синхронизируемого фронтом, будет

изменяться на противоположное

состояниеJK-триггера,

синхронизируемого фронтом, будет

изменяться на противоположное

при поступлении каждого синхроимпульса.

Таким образом,JK-триггер

в этом случае функционирует как T-триггер

при подаче счетного сигнала

при поступлении каждого синхроимпульса.

Таким образом,JK-триггер

в этом случае функционирует как T-триггер

при подаче счетного сигнала

на вход синхронизации

на вход синхронизации .D-триггер

имеет таблицу состояний 3.5, в которой

отсутствует состояние, соответствующее

режиму хранения. D-триггеры

бывают только синхронными, и в соответствии

с таблицей 3.5 они после поступления

синхросигнала устанавливаются в

состояние

.D-триггер

имеет таблицу состояний 3.5, в которой

отсутствует состояние, соответствующее

режиму хранения. D-триггеры

бывают только синхронными, и в соответствии

с таблицей 3.5 они после поступления

синхросигнала устанавливаются в

состояние

. (3.4)

. (3.4)

Выражение

(3.4) является характеристическим

уравнением D-триггера.

D-триггер

выполняет функцию задержки информации,

поступающей на управляющий вход

,

на один период синхросигналов (такт

машинного времени). В микроэлектронной

аппаратуре широко используютсяD-триггеры,

синхронизируемые фронтом и синхронизируемые

уровнем.

,

на один период синхросигналов (такт

машинного времени). В микроэлектронной

аппаратуре широко используютсяD-триггеры,

синхронизируемые фронтом и синхронизируемые

уровнем.

Таблица 3.4 Таблица 3.5

|

|

|

|

|

|

|

0 |

|

0 |

0 | |

|

1 |

|

1 |

1 |

Согласно

таблицам состояний 3.3 и 3.5 синхронный

JK-триггер

будет выполнять функции D-триггера,

если исключить комбинации, при которых

.

Это достигается соединением входов

.

Это достигается соединением входов и

и через инвертор. В свою очередь,D-триггер,

синхронизируемый фронтом, выполняет

функции T-триггера,

если соединить вход

через инвертор. В свою очередь,D-триггер,

синхронизируемый фронтом, выполняет

функции T-триггера,

если соединить вход

с инверсным выходом

с инверсным выходом .

.

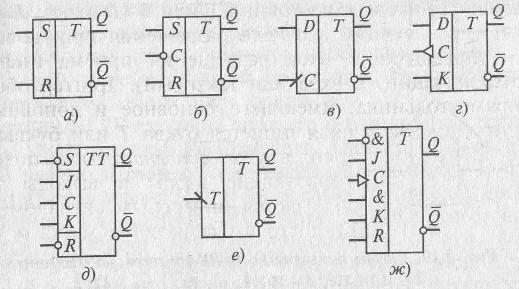

Условные графические обозначения рассмотренных триггеров приведены на рис. 3.4.

Рис. 3.4. Условные графические обозначения триггеров

а – асинхронный RS-триггер; б – синхронизируемый логическим нулем RS-триггер; в – D-триггер, срабатывающий по фронту 01; г – JK-триггер, срабатывающий по срезу 10; д – двухступенчатый JK-триггер с входами раздельной установки в нулевое (R) и единичное (S) состояния; T-триггер, срабатывающий по срезу 10; ж – синхронизируемый фронтом 10

JK-триггер с логическими элементами И на входах J и K

В комбинированных триггерах совмещаются несколько режимов. Например, триггер типа RST – счетный триггер, имеющий также входы установки и сброса.

Примером триггера со сложной входной логикой служит JK-триггер с группами

входов

и

и ,

соединенных операцией конъюнкции:

,

соединенных операцией конъюнкции:

,

,

. (3.5)

. (3.5)

Помимо

таблиц состояния и характеристических

уравнений, триггеры определяются также

таблицами переходов (словарями

триггеров), которые представляют собой

зависимость входных переменных от вида

переключений

.

Таблицы переходов для рассмотренных

выше триггеров приведены в таблице

3.6.

.

Таблицы переходов для рассмотренных

выше триггеров приведены в таблице

3.6.

Таблица 3.6