ЭБНЭ_full

.pdf

Постоянная память

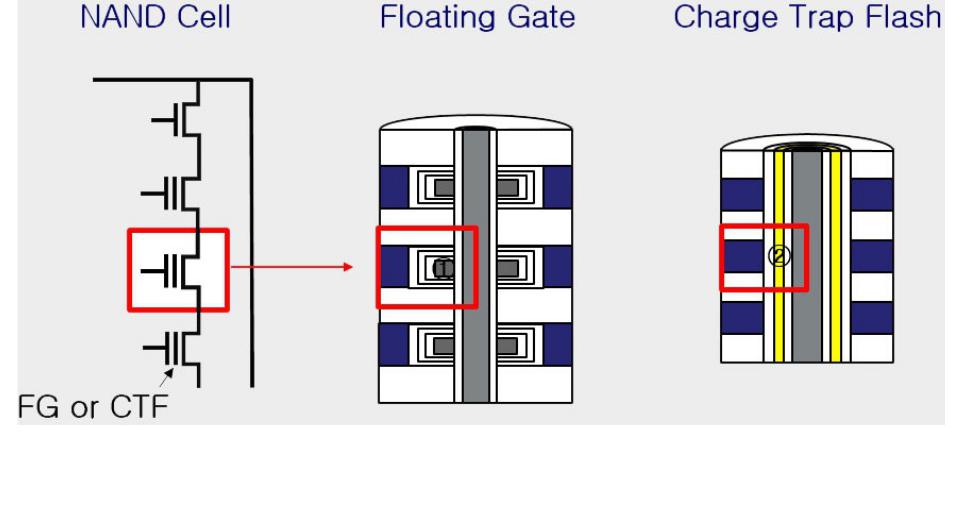

3D Flash

Micron

Постоянная память

3D Flash

Массовое производство началось в августе 2013 г, архитектура выпущенной памяти содержит 24 стэка ячеек и имеет емкость 128 Гбайт MLC (2бита/ячейка).

Это считается первым поколением 3D-памяти.

Второе поколение, созданное в 2014 г., содержит 32 стэка ячеек общим объемом 128 Гбайт и ячейки типа TLC (3бита/ячейка) с вертикальным каналом (V-NAND).

В 2016г. появляется третье поколение 3D-памяти с 48 стеками ячеек общим объемом 256

Гбайт и ячейками типа TLC V-NAND, и 768 Гбайт ячейки типа TLC FG NAND.

В последующие годы интенсивно возрастает количество стеков ячеек и уменьшается эффективный размер ячейки.

На сегодняшний момент технология столкнулась с серьезными трудностями, связанными с невозможностью дальнейшего увеличения числа стэков.

Постоянная память

3D Flash

Первая трудность - аспектное отношение превысило величину 30.

Поэтому память содержащая больше количество стэков реализовалась как группа по 32 стэка, то есть при заявленных 128 это означало 4x32 стэка.

При создании колодцев наблюдается отклонение формы колодца от идеального круга, чаще сечение представляет собой некое подобие эллипса и это приводит к появлению

нежелательныхэффектов.

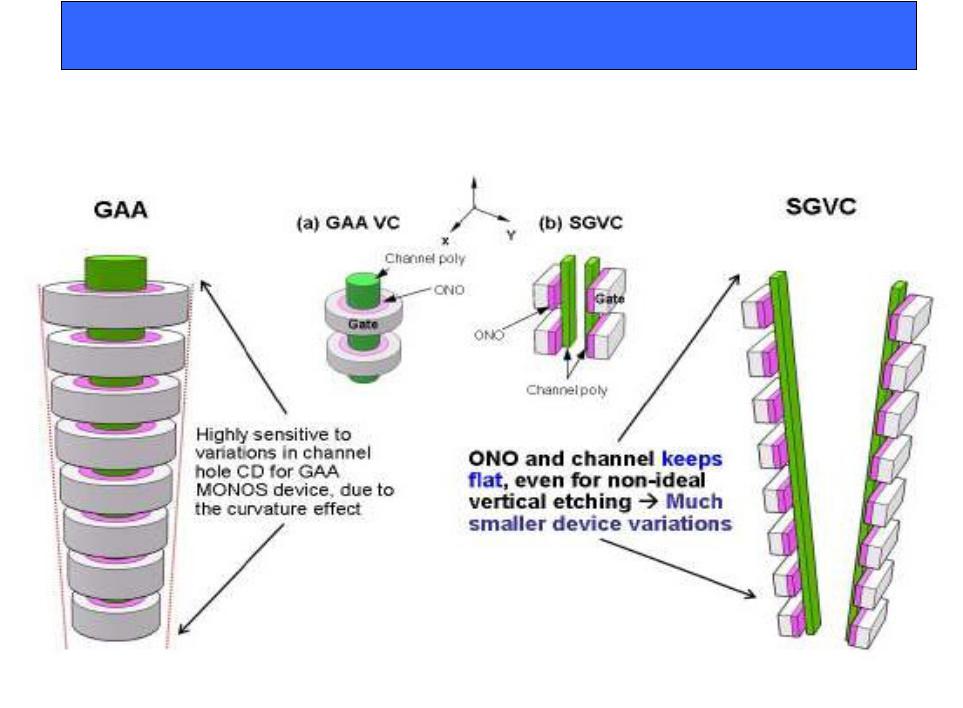

Вторая сложность-это низкие значения токов в поликремниевом канале. А также зависимость тока в канале от расположения ячейки в стэки.

Постоянная память

3D Flash

Следующимшагом в технологическом совершенствовании V-NAND памяти стало появление транзистора SGVC(Single-Gate Vertical Channel)

Постоянная память

3D Flash

Технологические дефекты при создании кольцевого затвора

Одноуровневая ячейка |

Многоуровневая ячейка |

«10» |

«01» |

«00» |

||

«1» |

«0» |

«11» |

||||

Состо |

Состо |

Состо |

Состо |

|||

Состо |

Состо |

|||||

яние D яние C |

яние В |

яние А |

||||

яние В |

яние А |

|||||

|

|

|

|

|||

Пороговое напряжение |

|

Пороговое напряжение |

||||

транзистора |

|

транзистора |

|

|||

У фирмы «Intel» это называется технология StrataFlash, у AMD и «Fujitsu» - MirrorBir, у израильской фирмы «Saifun» - NROM, у «Toshiba» и «M-Systems» – просто х2 или х4 (смотря по тому, сколько бит хранится в ячейке).

Тип ячейки

SLC

(Single Level Cell)

MLC

(Multi Level

Cell)

TLC (Triple

Level Cell)

Бит/на ячейку |

Кол-во состояний |

1 2

Надежная, высокая цена

2 4

Тот же размер ячейки, удвоенная емкость, ниже надежность

3 8

Тот же размер ячейки, высокая емкость, низкая надежность

Распределение напряжения в ячейке

Постоянная память

3D Flash

Многослойная 2D структура

3D структура

Элементная база наноэлектроники

Лекция 1

Основные термины

Элементная база – это система узлов, схем, устройств, блоков, а также способов и методов их соединения и взаимодействия, необходимых для построения соответствующих машин, устройств и других изделий.

Наноэлектроника – это раздел электроники, занимающийся разработкой физических и конструктивно-технологических основ

создания интегральных электронных схем со структурными

элементами нанометровых размеров – примерно от 1 до 100 нм.

наноэлектронная элементная база – это система наноразмерных структурных элементов, способов и методов их соединения и взаимодействия, необходимых для построения технических средств. Это также научно-техническая дисциплина, изучающая и описывающая принципы построения наноэлектронной элементной базы.