Frisk_1_tom

.pdf

150 |

Глава первая. Описание лабораторных работ по ОТЦ |

|

|

Ðèñ. 27

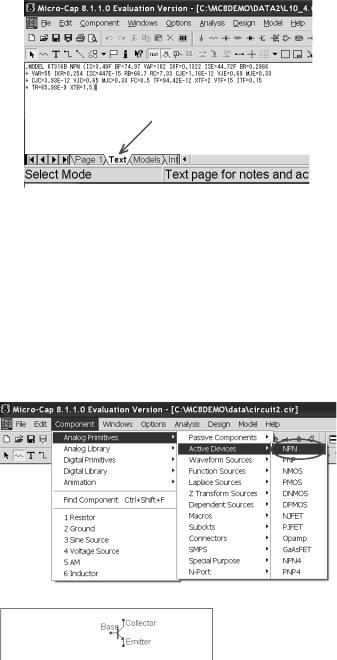

.MODEL KT316B NPN (IS = 3.49F BF = 74.97 VAF = 102 IKF = 0.1322 ISE = 44.72F BR = 0.2866

+VAR = 55 IKR = 0.254 ISC = 447E-15 RB = 66.7 RC = 7.33 CJE = 1.16E-12 VJE = 0.69 MJE = 0.33

+CJC = 3.93E-12 VJC = 0.65 MJC = 0.33 FC = 0.5 TF = 94.42E-12 XTF = 2 VTF = 15 ITF = 0.15

+TR = 65.98E-9 XTB = 1.5)

Щелкните закладку Page 1.

Откроите меню Component\Analog Primitives\Active Devices и выберите команду конденсатор NPN (ðèñ. 28).

Ðèñ. 28

Курсор примет форму транзистора. Поместите его на рабочее окно, возле конденсатора С3 и щелкните левой кнопкой мыши. Появиться окно NPN Transistor (ðèñ. 29). Â îêíå Value введите KT316B (латинскими буквами), установите галочку у Show и нажмите кнопку OK.

Лабораторная работа ¹ 10 |

151 |

|

|

Ðèñ. 29

Установите остальные элементы.

4.3.3 Построение осциллограммы и спектра генерируемого напряжения

Убедитесь, что введены все элементы правильно.

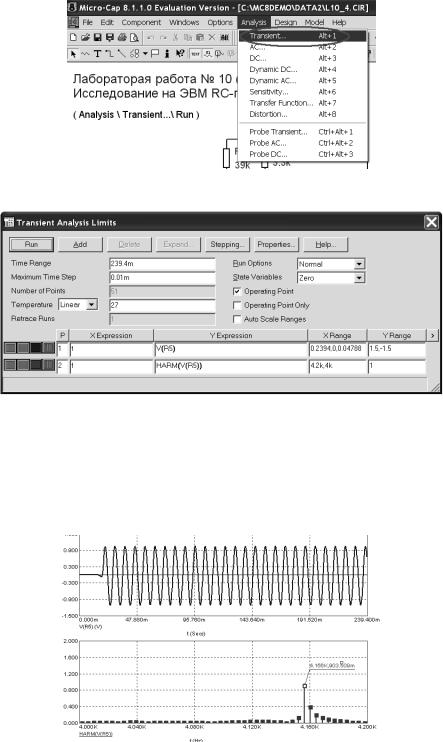

Получите зависимость генерируемого напряжения RС-генератора от времени (осциллограмму). Для этого в меню Analysis выберите команду

Transient... (ðèñ. 30).

На экране появиться окно Transient Analysis Limits, в котором следует задать параметры построения требуемых графиков так, как показано на рис. 31.

Time Range «239.4u» — интервал времени (0...239,4 мкс).

Maximum Time Step «0.01u» максимальный шаг интегрирования (0,01 мкс).

P номер окна «1», в котором будет построен график напряжения.

P номер окна «2», в котором будет построен график амплитудного спек-

òðà.

X Expression «t», «f» — аргументы функции напряжения и амплитудного спектра.

Y Expression «V(R5)» è «HARM(V(R5))» — имена функции напряжения и амплитудного спектра.

152 |

Глава первая. Описание лабораторных работ по ОТЦ |

|

|

Ðèñ. 30

Ðèñ. 31

X Range — интервал отображения аргумента по оси Х. Y Range — интервал отображения функции по оси Y. Запустите построение, нажав кнопку Run.

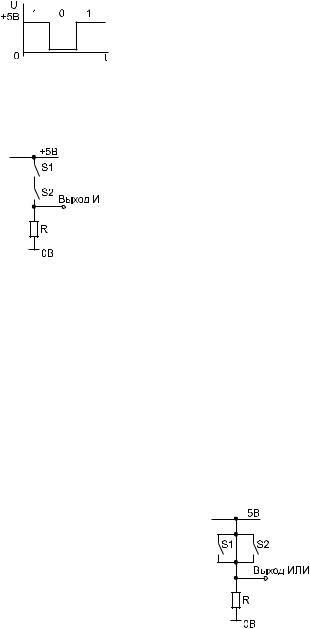

На экране появиться графики зависимости напряжения генерации V(R5) и амплитудный спектр (рис. 32).

Ðèñ. 32

Лабораторная работа ¹ 10 |

153 |

|

|

Полученные графики (осциллограмму и амплитудный спектр) занесите в соответствующий раздел отчета. По диаграмме амплитудного спектра определите частоту генерации и занесите ее значение в таблицу 1.

В случае возникновении проблем загрузите с сайта поддержки учебного процесса (http://frisk.newmail.ru/) файл L10_4.CIR (File\Open...).

5 Обработка результатов машинного эксперимента

Сравнить полученные графики и данные с графиками и данными, полу- ченными в предварительном расчете. Сделать выводы.

6 Вопросы для самопроверки

1.Выведите формулу ФЧХ для однозвенной фазосдвигающей цепочки.

2.Выведите формулу для частоты, при которой ФЧХ однозвенной цепоч- ки равна 60°.

3.Выведите формулу ФЧХ для двухзвенной фазосдвигающей цепочки.

4.Объясните физические процессы, проходящие в RC-генераторе?

5.Какое условие называется балансом фаз?

7 Содержание отчета

Отчет оформляется в формате MS Word. Шрифт Times New Roman 14, полуторный интервал.

Для защиты лабораторной работы отчет должен содержать следующий материал: титульный лист; цель работы; результаты машинного эксперимента; графики исследуемых зависимостей; выводы. К отчету должны быть приложены в напечатанном виде вопросы для самопроверки и ответы на них.

8Литература

1.Фриск В. В. Основы теории цепей. М.: РадиоСофт, 2002. 288 с.

2.Гоноровский И. С. Радиотехнические цепи и сигналы. М.: Радио и связь, 1986. 512 с.

3.Тули М. Карманный справочник по электронике. М.: Энергоатомиздат, 1993. 176 с.

Лабораторная работа ¹ 11

Исследование на ЭВМ цифровых логических элементов

1 Цель работы

С помощью программы Micro-Cap исследовать цифровые элементы электрических цепей. Изучить таблицы истинности и реализацию логических элементов ÍÅ, È, ÈËÈ, È-ÍÅ è ÈËÈ-ÍÅ.

2 Задание для самостоятельной подготовки

Изучить основные положения теории цепей о цифровых схемах стр. 267—271 [1], стр. 5—50 [2] и стр. 4—92 [3]. Выполнить предварительный рас- чет, письменно ответить на вопросы для самопроверки.

3 Предварительный расчет

3.1. Составить таблицу истинности для одновходового логического элемента ÍÅ (ðèñ. 1).

Ðèñ. 1

Обозначения на рис. 1: 1 — вход; 2 — выход.

Полученные данные занести в таблицу 1.

3.2. Составить таблицу истинности для двухвходового логического элемента È (ðèñ. 2).

Обозначения на рис. 2: 1 — первый вход; 2 — второй вход; 3 — выход.

Лабораторная работа ¹ 11 |

155 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ðèñ. 2

Полученные данные занести в таблицу 2.

3.3. Составить таблицу истинности для двухвходового логического элемента ÈËÈ (ðèñ. 3).

Ðèñ. 3

Обозначения на рис. 3: 1 — первый вход; 2 — второй вход; 3 — выход.

Полученные данные занести в таблицу 2.

3.4. Составить таблицу истинности для двухвходового логического элемента È-ÍÅ (ðèñ. 4).

Ðèñ. 4

Обозначения на рис. 4: 1 — первый вход; 2 — второй вход; 3 — выход.

Полученные данные занести в таблицу 2.

3.5. Составить таблицу истинности для двухвходового логического элемента ÈËÈ-ÍÅ (ðèñ. 5).

Ðèñ. 5

Обозначения на рис. 5: 1 — первый вход; 2 — второй вход; 3 — выход.

Полученные данные занести в таблицу 2.

156 |

|

Глава первая. Описание лабораторных работ по ОТЦ |

||

|

|

|

|

|

Таблица 1 |

|

|

|

|

|

|

|

|

|

|

|

По предварительному расчету |

|

Получено экспериментально |

|

|

|

|

|

S |

|

ÍÅ |

ÍÅ (NPN) |

ÍÅ (DPMOS, DNMOS) |

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 2

|

|

По предварительному расчету |

|

|

|

Получено экспериментально |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S1 |

S2 |

È |

ÈËÈ |

È-ÍÅ |

ÈËÈ-ÍÅ |

S1 |

S2 |

|

È |

ÈËÈ |

|

È-ÍÅ |

ÈËÈ-ÍÅ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 Порядок выполнения работы

В цифровых микросхемах логические операции осуществляются с помощью логических элементов. Устройства, предназначенные для формирования алгебры логики, называются цифровыми устройствами. Функции алгебры логики и их аргументы могут принимать значения логических 0 и 1.

Рассмотрим некоторые элементарные логические функции.

Логическая функция ÍÅ (логическое отрицание, инверсия) одного аргумента преобразует сигнал логической 1 на своем входе в логический 0 на выходе. Логический 0 на входе преобразуется в логическую 1 на выходе.

Логическая функция È (конъюнкция) двух аргумента осуществляет операцию логического умножения сигналов. Конъюнкция входных сигналов равна логической 1 в том случае, когда оба входных сигналов равны логиче- ской 1. Если хотя бы на одном входе присутствует логический 0, то на выходе будет 0.

Логическая функция ÈËÈ (дизъюнкция) двух аргумента осуществляет операцию логического сложения сигналов. Дизъюнкция входных сигналов равна логической 1, если или первый сигнал или второй сигнал равен логиче- ской 1. Сигнал 0 на выходе появляется тогда, когда на двух входах одновременно присутствует логический 0.

Логическая функция È-ÍÅ (штрих Шеффера) двух аргумента осуществляет операцию логического отрицания конъюнкции. Если на всех входах штриха Шеффера присутствует логическая 1, то на выходе будет 0. Иначе на выходе будет 1.

Логическая функция ÈËÈ-ÍÅ (стрела Пирса, функция Вебба) двух аргумента осуществляет операцию отрицания дизъюнкции. Если на всех входах

Лабораторная работа ¹ 11 |

157 |

|

|

стрелы Пирса имеется логический 0, то на выходе будет логическая 1. Любая другая комбинация входных сигналов приведет к логическому 0 на выходе.

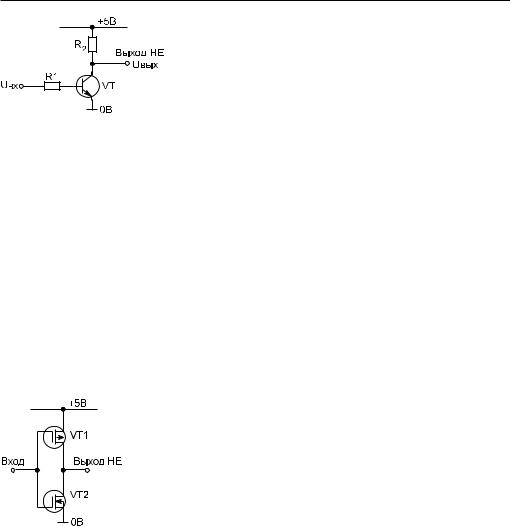

Будем использовать положительную логику, т. е. считать, что логическая 1 физически соответствует высокому уровню напряжения (близкому к +5 В). Логический 0 соответствует низкому уровню напряжения (близкому к нулю вольт) (рис. 6).

Ðèñ. 6

Если последовательно соединить два ключа (рис. 7), то они будут работать по логике È. Ток в цепи появиться, если замкнуты оба ключа и S1 и S2.

Ðèñ. 7

Назовем замыкание ключа событием логической 1, а размыкание ключа событием логического 0. Будем считать, что на выходе элемента логическая 1 соответствует напряжению высокого уровня, а логический 0 напряжению низкого уровня.

Последовательно перебирая состояния этих ключей, можно составить таблицу входных и выходных данных для такого элемента. Покажем с помощью программы Micro-Cap, что эта таблица будет таблицей истинности элемента È.

Если параллельно соединить два ключа (рис. 8), то они будут работать по логике ÈËÈ. Ток в цепи появиться, если замкнут ключ S1 или ключ S2. Назовем замыкание ключа событием логической 1, а размыкание ключа событием логического 0. Будем считать, что на выходе элемента логическая 1 соответствует напряжению высокого уровня, а логический 0 напряжению низкого

уровня. Последовательно перебирая состояния этих клю- |

|

чей, можно составить таблицу входных и выходных данных |

|

для такого элемента. Покажем с помощью программы |

|

Micro-Cap, что эта таблица будет таблицей истинности эле- |

|

мента ÈËÈ. |

|

На рис. 9 показана одна из возможных реализаций од- |

|

новходового элемента ÍÅ. Наибольшее распространение |

|

получил транзисторный элемент, собранный по схеме с об- |

|

щим эмиттером (рис. 9). Резистор R1 ограничивающий ток |

Ðèñ. 8 |

158 |

Глава первая. Описание лабораторных работ по ОТЦ |

|

||||||

|

|

базы последовательно соединен с n-p-n транзи- |

||||||

|

|

стором VT. Резистор R2 — коллекторная нагрузка. |

||||||

|

|

|

Когда на базе транзистора нет напряжения, то |

|||||

|

|

транзистор закрыт, выходное напряжение имеет |

||||||

|

|

высокий уровень (почти +5 В). Если через рези- |

||||||

|

|

ñòîð R1 на базу транзистора подать напряжение |

||||||

Ðèñ. 9 |

высокого уровня, то потечет ток, который откроет |

|||||||

транзистор, т. е. переведет транзистор в состояние |

||||||||

|

|

|||||||

насыщения. В этом случаи выходное напряжение станет низким. Можно счи- |

||||||||

тать, что все выводы транзистора база, эмиттер и коллектор замкнуты между |

||||||||

собой, т. е. транзистор превращается в точку. |

|

|

|

|||||

Будем считать, что переключение транзистора происходит мгновенно. |

||||||||

Следовательно, выходное напряжение может принимать только два дискрет- |

||||||||

ных значения высокое (логическая 1) или низкое (логический 0). Транзистор |

||||||||

работает в ключевом режиме. Он только открыт или только закрыт и удержи- |

||||||||

вается в одном из этих состояний, пока на входе сохраняется соответствую- |

||||||||

щий уровень сигнала. |

|

|

|

|

|

|

||

Последовательно подавая на вход низкий (логический 0) или высокий |

||||||||

(логическая 1) уровень напряжения, можно составить таблицу входных и вы- |

||||||||

ходных данных для такого элемента. Покажем с помощью программы |

||||||||

Micro-Cap, что эта таблица будет таблицей истинности элемента ÍÅ. |

|

|||||||

Вместо биполярного транзистора можно использовать комплиментарную |

||||||||

пару полевых транзисторов (КМОП — комплиментарная-метал-окисел-полу- |

||||||||

|

|

проводник) с противоположными типами электропро- |

||||||

|

|

водимости. Затворы этих транзисторов электрически со- |

||||||

|

|

единены |

è |

образуют |

âõîä |

логического |

элемента |

|

|

|

(ðèñ. 10). |

|

|

|

|

|

|

|

|

Транзистор VT1 имеет р-канал, а транзистор VT2 — |

||||||

|

|

n-канал. |

|

|

|

|

|

|

|

|

Если на входе устанавливается низкий уровень на- |

||||||

|

|

пряжения (логический 0), то транзистор VT1 открыт, а |

||||||

|

|

транзистор VT2 закрыт. В этом случае уровень выходно- |

||||||

Ðèñ. 10 |

|

го напряжения будет близок к напряжения шины пита- |

||||||

|

|

ния +5 В (логическая 1). |

|

|

|

|||

Когда на входе устанавливается высокий уровень напряжения (логиче- |

||||||||

ская 1), то транзистор VT1 закрыт, а транзистор VT2 открыт. В этом случае |

||||||||

уровень выходного напряжения будет близок к нулевому потенциалу обей |

||||||||

шины (логический 0). |

|

|

|

|

|

|||

Заметим, что поскольку один из транзисторов обязательно закрыт при |

||||||||

любом сигнале на входе, то ток через эти транзисторы не проходит. Поэтому |

||||||||

потребление энергии от источника питания происходит только в моменты пе- |

||||||||

реключения транзисторов. |

|

|

|

|

|

|||

Последовательно подавая на вход комплиментарной пары низкий (логи- |

||||||||

ческий 0) или высокий (логическая 1) уровень напряжения, можно составить |

||||||||

таблицу входных и выходных данных для такого элемента. Покажем с помо- |

||||||||

щью программы Micro-Cap, что эта таблица будет таблицей истинности эле- |

||||||||

мента ÍÅ. |

|

|

|

|

|

|

|

|

Лабораторная работа ¹ 11 |

159 |

|

|

В качестве элемента È-ÍÅ используем цифровую микросхему. Элементы таких микросхем имеют два, три или четыре входа и выполняют над входными данными операцию È с последующим изменением результата на противоположный.

На рис. 11 показан пример микросхемы изготовленная на основе КМОП-структур (K561ЛА7). В одном корпусе размещаются четырех логиче- ских элемента È-ÍÅ. Элементы работают независимо друг от друга, хотя имеют общие шины, к которым подключают источник питания. Каждый логиче- ский элемент имеет два входа и один выход.

Ðèñ. 11

Назначение выводов данной микросхемы.

1 и 2, 4 и 5, 8 и 9, 12 и 13 — соответственно входы логических элементов; 3, 6, 10 и 11 — выходы логических элементов.

К выводу 14 подключают питание микросхемы. Вывод 7 является общим. Последовательно подавая на входы одного логического элемента этой микросхемы низкий (логический 0) или высокий (логическая 1) уровень напряжения, можно составить таблицу входных и выходных данных для такого элемента. Покажем с помощью программы Micro-Cap, что эта таблица будет

таблицей истинности элемента È-ÍÅ.

В качестве элемента ÈËÈ-ÍÅ используем цифровую микросхему К561ЛЕ5 (рис. 12). Элементы этой микросхем имеют два входа и один выход. Над входными данными выполняется операция ÈËÈ с последующим изменением результата на противоположный.

Ðèñ. 12