Slides_OEVM_final

.pdf

Лекция 8. Внутренняя память: |

|

|

|||

структурная организация п/п ЗУ |

|

|

|||

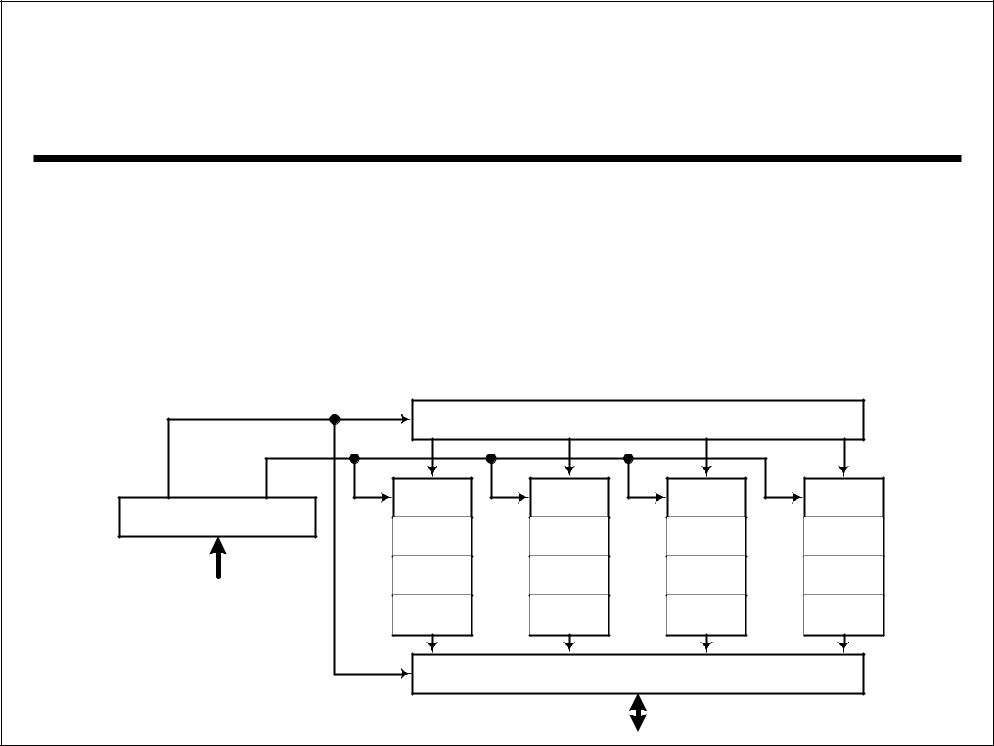

Блочная схема |

|

|

|

|

|

Адресное пространство памяти разбито на группы |

|

|

|||

последовательных адресов. Каждую группу обеспечивает |

|

||||

отдельный банк памяти. |

|

|

|

|

|

A8...A9 |

Дешифратор номера банка памяти |

|

|||

A0...A7 |

|

||||

|

|

|

|

|

|

Регистр адреса |

Банк0 |

Банк1 |

Банк2 |

Банк3 |

|

0 |

256 |

512 |

768 |

|

|

A0...A9 |

|

||||

... |

... |

... |

... |

|

|

Шина адреса |

255 |

511 |

767 |

1023 |

|

|

|

Мультиплексор |

|

242 |

|

© С. Г. Мосин, 2007 |

|

|

Шина данных |

||

|

|

|

|||

|

|

|

|

||

Лекция 8. |

Внутренняя память: |

|

|

|||

структурная организация п/п ЗУ |

|

|

||||

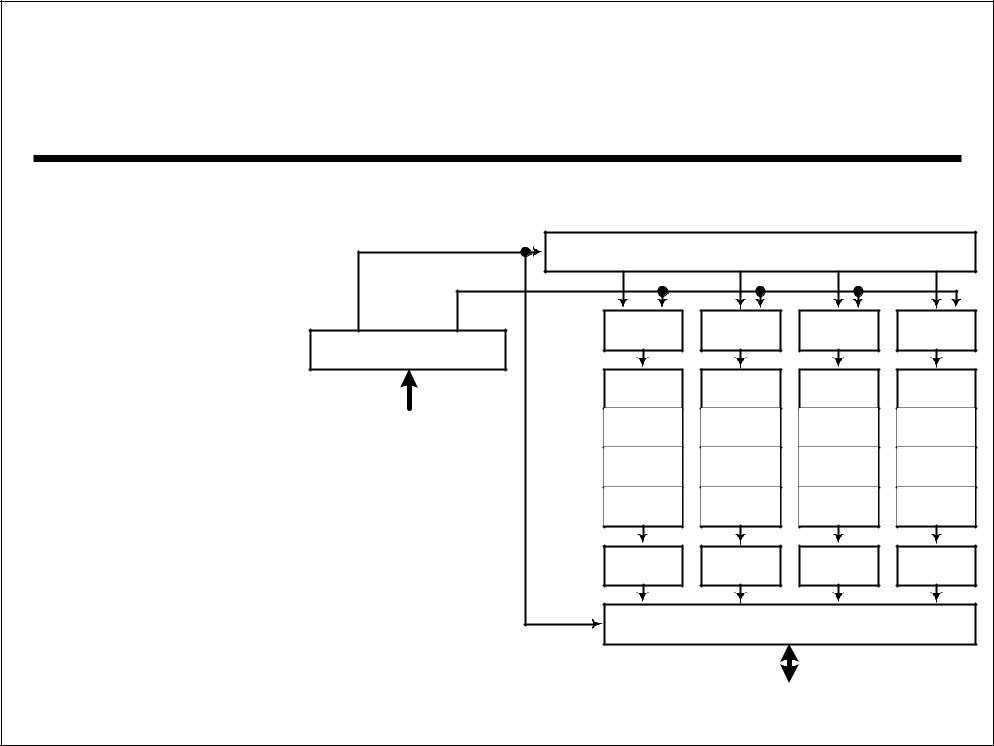

Схема расслоения памяти (циклическая) |

|

|

|

|||

Используется |

A0...A1 |

Дешифратор номера банка памяти |

||||

A2...A9 |

||||||

чередование |

|

|

|

|

||

|

РгА0 |

РгА1 |

РгА2 |

РгА3 |

||

адресов между |

Регистр адреса |

|||||

|

|

|

|

|||

банками |

A0...A9 |

Банк0 |

Банк1 |

Банк2 |

Банк3 |

|

памяти. |

||||||

Шина адреса |

0 |

1 |

2 |

3 |

||

Чередование |

... ... ... ... |

|||||

|

||||||

обеспечивают за счет |

1020 |

1021 |

1022 |

1023 |

||

циклического разбиения |

РгД |

РгД |

РгД |

РгД |

||

адреса. |

|

|

Мультиплексор |

|

||

n = A mod N, a = A div N |

|

|

||||

|

|

Шина данных |

||||

© С. Г. Мосин, 2007 |

|

|

|

|

243 |

|

|

|

|

|

|

||

Лекция 8. Внутренняя память: |

|

|||

структурная организация п/п ЗУ |

|

|||

Способы повышения быстродействия ИС памяти |

|

|||

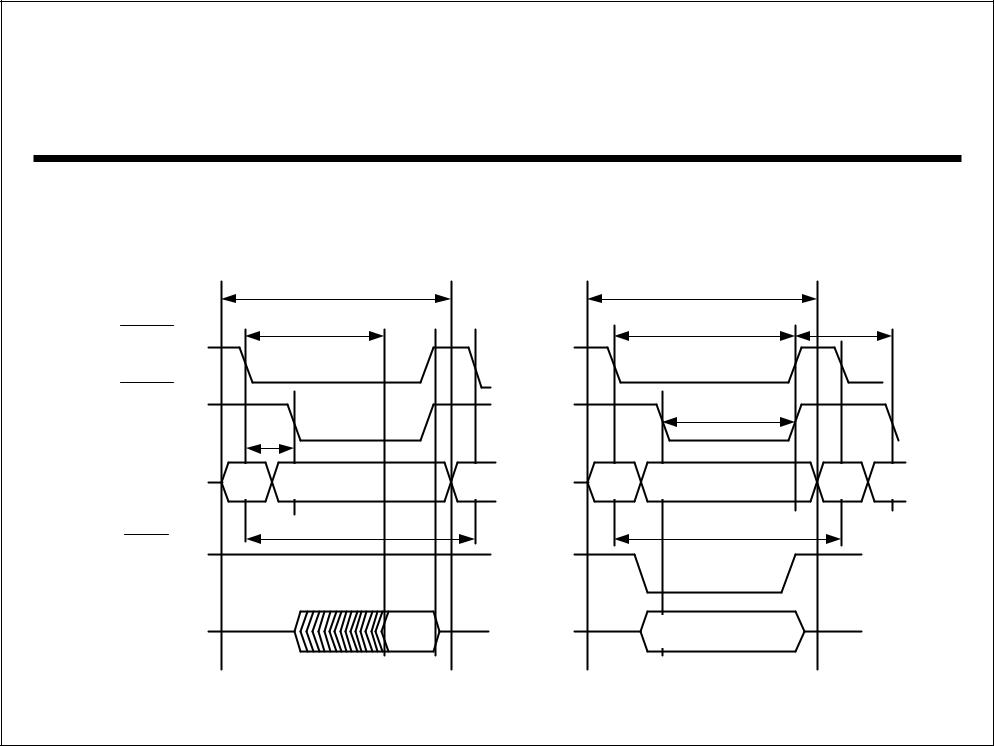

Пакетный режим (Burst Mode) – на запрос по конкретному |

||||

адресу память возвращает пакет данных, которые хранятся по |

||||

данному адресу и по нескольким последующим адресам. |

||||

TRAS |

|

TPC |

|

|

RAS |

|

|

|

|

CAS |

|

|

|

|

ADDR R1 C1 |

C2 |

C3 |

C4 |

|

DATA |

D1 |

D2 |

D3 |

D4 |

© С. Г. Мосин, 2007 |

|

|

|

248 |

|

|

|

|

|

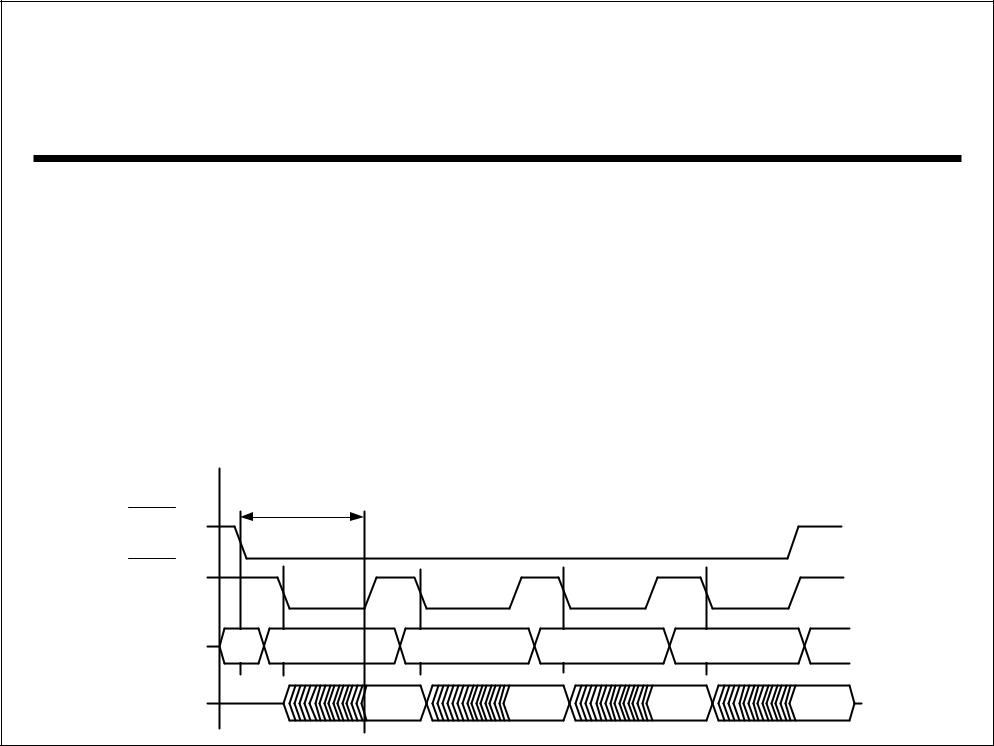

Лекция 8. Внутренняя память: структурная организация п/п ЗУ

Способы повышения быстродействия ИС памяти

EDO (Extended Data Output – растянутый выход данных). В микросхеме EDO-памяти на выходе установлен буфер-защелка,

фиксирующий данные после их извлечения из матрицы памяти при подъеме сигнала CAS и удерживающий их на выходе до следующего его спада. Это позволило сократить длительность сигнала CAS и соответственно цикл памяти.

RAS |

|

TRAS |

|

|

|

|

|

|

|

|

|

|

|

CAS |

|

|

|

|

|

|

ADDR |

R1 |

C1 |

C2 |

C3 |

C4 |

|

© С. ГDATA. Мосин, 2007 |

|

|

D1 |

D2 |

D3 |

249 |

|

|

D4 |

Лекция 8. Внутренняя память: структурная организация п/п ЗУ

Способы повышения быстродействия ИС памяти

Синхронная DRAM. У SDRAM- памяти присутствует синхросигнал CLK, по переднему фронту которого происходят все переключения в микросхеме. Сигнал CKE (Clock Enable) разрешает работу микросхемы при высоком уровне, а при низком – переводит ее в один из режимов энергосбережения. Сигналы выбора банка BS0 и BS1, адресуют конкретные обращения в один из четырех имеющихся в микросхемах SDRAM банков памяти. Сигналы DQM маски линий данных позволяют

блокировать запись данных в цикле записи или переключать шину |

||

данных в состояние высокого выходного сопротивления при |

|

|

чтении. В момент подачи сигнала CAS сигнал A10 на линии адреса |

||

задает способ подзаряда строки банка. |

250 |

|

© С. Г. Мосин, 2007 |

||

|

||