- •Глава 1. Основные понятия 9

- •Глава 8. Организация виртуальной памяти 227

- •Глава 9. Организация кэш-памяти 246

- •Глава1. Основные понятия

- •1.1. Система программно-аппаратных средств обработки информации

- •1.2.Традиционная классификация эвм

- •1.3. Структуры эвм

- •1.4. Многомашинные комплексы и многопроцессорные системы

- •1.5. Эволюция режимов работы эвм

- •1.5. Особенности построения и эксплуатации современных многопроцессорные и многомашинных комплексов.

- •Глава 2. Программная модель процессора

- •2.1. Общие понятия

- •2.2. Виды используемых структур памяти по принципам размещения и поиска информации

- •2.3. Организация оперативной памяти

- •2.3.1. Оперативная память и адресные пространства процессора

- •2.3.2. Адресация многобайтовых объектов в оперативной памяти

- •2.3.3. Структура и типы команд

- •2.4. Режимы адресации

- •2.5. Типы машинных арифметик

- •2.6. Управление потоком команд.

- •2.7. Контекст программы

- •2.8. Команды cisc- и risc-архитектуры

- •Глава 3. Программная модель мп Intel

- •3.1. Режимы работы

- •3.2. Программная модель 16-ти битового микропроцессора мп ia-16

- •3.2.1. Модель памяти

- •3.2.2. Порты ввода/вывода

- •2.2.3. Регистровый файл

- •3.2.4. Структура команд

- •3.3. Программная модель 32-битового микропроцессора

- •3.3.1. Основные особенности организации

- •3.3.2. Модель памяти

- •3.3.3. Регистровый файл

- •3.3.4. Структура команд и режимы адресации

- •3.3.5. Структура данных

- •Глава 4. Программные модели мп корпорации dec

- •4.1. Программная модель процессоров семейства pdp-11

- •4.2. Программная модель процессоров эвм vax-11 (см 1700)

- •Глава 5. Система прерывания

- •5.1.Функции системы прерывания и общие решения по реализации

- •5.2. Система прерывания в мп intel

- •5.2.1. Система прерывания в мп ia-16

- •5.2.2. Особенности системы прерывания в мп ia-32

- •5.2.3. Организация системы прерывания в pdp 11

- •Глава 6. Организация ввода-вывода

- •6.1. Система ввод/вывода

- •6.2.Теоретические основы операций ввода/вывода

- •6.3. Синхронизация передачи данных при вводе/выводе

- •6.3.1. Ввод/вывод с проверкой готовности

- •6.3.2. Ввод/вывод с использованием системы прерывания

- •6.3.3. Ввод/вывод с использованием устройств прямого доступа к памяти

- •Глава 7. Шинные интерфейсы

- •7.1. Общие положения

- •7.2. Асинхронный системный интерфейс "Общая шина"

- •7.3. Системные интерфейсы мп ia

- •7.4. Локальный интерфейс микропроцессора i80386

- •7.4.1. Особенности локального интерфейса i80386

- •7.4.2. Диаграммы работы локального интерфейса мп i80386

- •7.4.3. Модель функционирования локального интерфейса мп i80386. (интерфейс с конвейерной передачей данных)

- •7.4.4. Специальные циклы

- •7.5. Локальный интерфейс микропроцессора i486 (интерфейс с пакетной передачей данных)

- •7.5.1. Особенности локального интерфейса i486

- •7.5.2. Диаграммы работы локального интерфейса мп i486

- •7.5.3. Модель функционирования локального интерфейса мп i486

- •7.6. Локальный интерфейс мп Pentium (интерфейс с пакетной передачей данных и конвейеризацией передачи адреса)

- •7.7. Интерфейсы с расщепленными транзакциями

- •Глава 8. Организация виртуальной памяти

- •8.2. Основные задачи виртуальной памяти

- •8.3. Страничная организации виртуальной памяти

- •8.3.1. Страничная организация памяти

- •8.3.2. Виртуальная память на основе таблицы математических страниц

- •8.3.3. Упрощенная схема виртуальной памяти на основе таблицы физических страниц

- •8.3.4. Схема виртуальной памяти на основе таблицы физических страниц.

- •Глава 9. Организация кэш-памяти

- •9.1. Назначение и общая схема подключения кэш-памяти

- •9.2. Системы адресации кэш-памяти

- •9.3. Режимы работы кэш-памяти

- •9.4. Иерархическая структура кэш-памяти и средства управления кэш-памятью

- •9.5. Организация когерентности системы кэш-памяти в многопроцессорных системах с общей оперативной памятью.

- •Основные переходы. При запросах на чтение (r):

- •Чтение (sr2):e в s. При запросах на запись (w):

- •Глава 10. Организация системы памяти на жестких дисках

- •10.1.Дисковые массивы и уровни raid

- •125Стр. Из 292

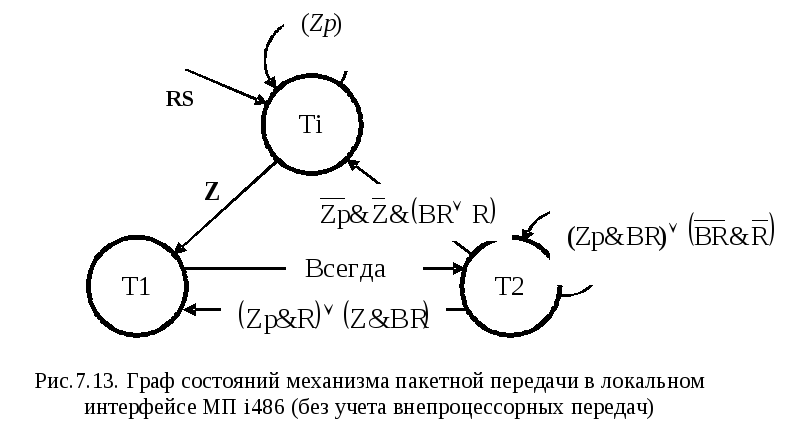

7.5.3. Модель функционирования локального интерфейса мп i486

Последовательности тактов, представленные на рисунках 7.10, 7.11, и 7.12 не исчерпывают все множество возможных комбинаций тактов в последовательностях локального интерфейса МП i486. На рисунке 7.13 представлена упрощенная модель функционирования локального интерфейса МП i486 в виде графа состояний и переходов. Упрощение заключается в том, что в модели не рассматриваются такты Tb и Т1b. То есть моделируется только взаимодействие задатчика с исполнителем без арбитража и смены задатчика.

В модели на рис. 7.13 вершины графа соответствуют отдельным тактам возможных циклов, дуги – переходам. Вершины графа снабжены символами названия соответствующих тактов, переходы – условиями переходов.

Внутренний запрос процессора на передачу данных может потребовать один простой цикл, один пакетный цикл или одну последовательность циклов, отдельные циклы которой могут быть пакетными. В пакетном цикле и в одной последовательности циклов могут передаваться только данные одной строчки кэш-памяти.

В связи с этим в модели внутренний запрос процессора на передачу данных может быть запросом передачи данных новой строчки кэш-памяти Z или запросом на продолжение передачи данных той же строчки кэш-памяти Zp.

Описание тактов и условий переходов

Ti – шины интерфейса находятся в пассивном состоянии. Сигналы на линиях адреса и сигналы статуса имеют неопределенные значения, тристабильные выходы могут находиться в высокоимпедансном состоянии.

При включении или рестарте процессора на шинах интерфейса устанавливается такт Тi. Процессор находится в пассивном состоянии при отсутствии внутреннего запроса процессора на передачу данных. При появлении внутреннего запроса на передачу данных производится переход на такт Т1.

Состояние подтверждения прерывания для процессора также является пассивным состоянием. Это тоже такт Тi, но в состоянии захвата процессор активизирует идентифицирующий выходной сигнал HLDA.

T1 – Первый такт цикла магистрали. На линиях адреса и идентификации цикла устанавливаются достоверные значения, сигнал ADS# активен. После такта Т1 всегда следует такт Т2.

T2 - Второй и последующие такты цикла магистрали. Данные формируются в цикле записи или принимаются в цикле чтения. Проверяется активность сигналов RDY# и BRDY# и наличие внутренних запросов процессора Z и Zp.

При одновременной пассивности сигналов RDY# и BRDY# или активности BRDY# и Zp – такт Т2 повторяется.

При активных сигналах Zp и RDY# или сигналах Z и BRDY# – такт Т2 сменяется тактом Т1.

При одновременной пассивности сигналов Zp и Z, но активности одного из сигналов готовности RDY# или BRDY# – такт Т2 сменяется тактом Тi.

Вопросы для самопроверки:

1. Новые сигналы в интерфейсе.

2. Особенности автоконфигурации шины данных.

3. Особенности кодировки циклов.

4. Роль встроенной в процессор кэш-памяти.

5. Организация пакетных циклов.

6. Предназначение сигнала BLAST.

7. Назначение сигналов RDY и BRDY.

8. Использование сигналаBLAST.

7.6. Локальный интерфейс мп Pentium (интерфейс с пакетной передачей данных и конвейеризацией передачи адреса)

Процессор Pentium содержит кэш-память, ориентированную на пакетную передачу строки данных в 32 байта, т.е. в два раза большую по сравнению со строкой данных МП i486. Для сокращения времени передачи шина данных локального интерфейса процессора содержит 64 линии данных. Но это только внешняя шина передачи данных. Ширина обработки данных остается 4 байта (два двойных слова).

Другой особенностью протокола интерфейса процессора Pentium является возможное совмещение пакетной передачи с конвейеризацией адресов. Конвейеризация адресов, как и в интерфейсе МП 386, производится по инициативе периферийного устройства по сигналу запроса следующего адреса NA.

Пример передачи данных в пакетном режиме и с конвейеризацией передачи адреса представлен на рис.7.14.

|

|

|

Конвейерная передача пакета "а" |

| |||||||||

|

|

|

Конвейерная передача пакета "б" | ||||||||||

|

ТАКТЫ |

Тi |

Т1 |

Т2 |

Т2 |

Т2 |

Т12 |

Т1р |

Т2 |

Т2 |

Т12 |

Т1р | |

|

CLK |

|

|

|

|

|

|

|

|

|

|

| |

|

ADS# |

|

|

|

|

|

|

|

|

|

|

| |

|

ADRESS |

|

|

a |

|

|

b |

|

|

|

|

с | |

|

CACHE# |

|

|

|

|

|

|

|

|

|

|

| |

|

W/R# |

|

|

|

|

|

|

|

|

|

|

| |

|

KEN# |

|

|

|

|

|

|

|

|

|

|

| |

|

NA# |

|

|

|

|

|

|

|

|

|

|

| |

|

BRDY# |

|

|

|

a |

a |

a |

a |

b |

b |

b |

b | |

|

DATA |

|

|

|

|

|

|

|

|

|

|

| |

|

Рис.7.14 Конвейеризированные пакетные циклы чтения на шине локального интерфейса МП Pentium | ||||||||||||

Пакетная передача данных производится только при возможности их занесения в кэш-память процессора по сигналу KEN# (разрешение кэширования данных запрошенной области от контроллера памяти) и запросу NA# (сигнал от контроллера памяти) следующего адреса.

Вопросы для самопроверки:

1.Особенность разрядности шин данных.

2. Решение проблемы согласования разрядности процессора и УВВ.

3. Конвейеризированные пакетные циклы.