- •Глава 1. Основные понятия 9

- •Глава 8. Организация виртуальной памяти 227

- •Глава 9. Организация кэш-памяти 246

- •Глава1. Основные понятия

- •1.1. Система программно-аппаратных средств обработки информации

- •1.2.Традиционная классификация эвм

- •1.3. Структуры эвм

- •1.4. Многомашинные комплексы и многопроцессорные системы

- •1.5. Эволюция режимов работы эвм

- •1.5. Особенности построения и эксплуатации современных многопроцессорные и многомашинных комплексов.

- •Глава 2. Программная модель процессора

- •2.1. Общие понятия

- •2.2. Виды используемых структур памяти по принципам размещения и поиска информации

- •2.3. Организация оперативной памяти

- •2.3.1. Оперативная память и адресные пространства процессора

- •2.3.2. Адресация многобайтовых объектов в оперативной памяти

- •2.3.3. Структура и типы команд

- •2.4. Режимы адресации

- •2.5. Типы машинных арифметик

- •2.6. Управление потоком команд.

- •2.7. Контекст программы

- •2.8. Команды cisc- и risc-архитектуры

- •Глава 3. Программная модель мп Intel

- •3.1. Режимы работы

- •3.2. Программная модель 16-ти битового микропроцессора мп ia-16

- •3.2.1. Модель памяти

- •3.2.2. Порты ввода/вывода

- •2.2.3. Регистровый файл

- •3.2.4. Структура команд

- •3.3. Программная модель 32-битового микропроцессора

- •3.3.1. Основные особенности организации

- •3.3.2. Модель памяти

- •3.3.3. Регистровый файл

- •3.3.4. Структура команд и режимы адресации

- •3.3.5. Структура данных

- •Глава 4. Программные модели мп корпорации dec

- •4.1. Программная модель процессоров семейства pdp-11

- •4.2. Программная модель процессоров эвм vax-11 (см 1700)

- •Глава 5. Система прерывания

- •5.1.Функции системы прерывания и общие решения по реализации

- •5.2. Система прерывания в мп intel

- •5.2.1. Система прерывания в мп ia-16

- •5.2.2. Особенности системы прерывания в мп ia-32

- •5.2.3. Организация системы прерывания в pdp 11

- •Глава 6. Организация ввода-вывода

- •6.1. Система ввод/вывода

- •6.2.Теоретические основы операций ввода/вывода

- •6.3. Синхронизация передачи данных при вводе/выводе

- •6.3.1. Ввод/вывод с проверкой готовности

- •6.3.2. Ввод/вывод с использованием системы прерывания

- •6.3.3. Ввод/вывод с использованием устройств прямого доступа к памяти

- •Глава 7. Шинные интерфейсы

- •7.1. Общие положения

- •7.2. Асинхронный системный интерфейс "Общая шина"

- •7.3. Системные интерфейсы мп ia

- •7.4. Локальный интерфейс микропроцессора i80386

- •7.4.1. Особенности локального интерфейса i80386

- •7.4.2. Диаграммы работы локального интерфейса мп i80386

- •7.4.3. Модель функционирования локального интерфейса мп i80386. (интерфейс с конвейерной передачей данных)

- •7.4.4. Специальные циклы

- •7.5. Локальный интерфейс микропроцессора i486 (интерфейс с пакетной передачей данных)

- •7.5.1. Особенности локального интерфейса i486

- •7.5.2. Диаграммы работы локального интерфейса мп i486

- •7.5.3. Модель функционирования локального интерфейса мп i486

- •7.6. Локальный интерфейс мп Pentium (интерфейс с пакетной передачей данных и конвейеризацией передачи адреса)

- •7.7. Интерфейсы с расщепленными транзакциями

- •Глава 8. Организация виртуальной памяти

- •8.2. Основные задачи виртуальной памяти

- •8.3. Страничная организации виртуальной памяти

- •8.3.1. Страничная организация памяти

- •8.3.2. Виртуальная память на основе таблицы математических страниц

- •8.3.3. Упрощенная схема виртуальной памяти на основе таблицы физических страниц

- •8.3.4. Схема виртуальной памяти на основе таблицы физических страниц.

- •Глава 9. Организация кэш-памяти

- •9.1. Назначение и общая схема подключения кэш-памяти

- •9.2. Системы адресации кэш-памяти

- •9.3. Режимы работы кэш-памяти

- •9.4. Иерархическая структура кэш-памяти и средства управления кэш-памятью

- •9.5. Организация когерентности системы кэш-памяти в многопроцессорных системах с общей оперативной памятью.

- •Основные переходы. При запросах на чтение (r):

- •Чтение (sr2):e в s. При запросах на запись (w):

- •Глава 10. Организация системы памяти на жестких дисках

- •10.1.Дисковые массивы и уровни raid

- •125Стр. Из 292

2.4. Режимы адресации

С появлением РОНов появилось два типа команд:

команды структуры регистр/регистр (r/r): Коп R1, R2,

команды структуры регистр/память (r/m): Коп R1, М2,

где:

R1, R2 – номера (адреса) РОНов.

M2 – полноразрядный адрес оперативной памяти.

Первый тип команд по отношению к данным является двухадресным (задаются адреса двух РОНов), но по отношению к памяти – безадресным.

Второй тип команд по отношению к данным тоже двухадресный, но по отношению к памяти – одноадресный (первый адрес является адресом РОНа).

Адреса памяти в современных процессорах задаются в большинстве случаев отдельными компонентами с указанием (явно или "по умолчанию") способа вычисления адреса. Способы вычисления адреса определяются режимами адресации. Задание операнда в команде его непосредственным значением (непосредственный операнд), прямым значением адреса (непосредственный адрес) или номером РОНа – это частные случаи режимов адресации.

Адреса операндов в командах задаются через компоненты по двум причинам:

1. для уменьшения разрядности поля адреса в команде,

2. для упрощения процедур обработки массивов.

Уменьшение разрядности поля адреса

Для 32-разрядных машин, например моделей семейства IBM 360, команда имеет следующие размеры полей:

Команды структуры r/r: код операции – 8 бит, R1 и R2 – по четыре бита. Итого 16 бит при ширине выборки данных из памяти 32 бита. За одно обращение к памяти выбирается по две команды этого типа. Тут нет проблем.

Команды структуры регистр/память (r/m): код операции – 8 бит, R1 – 4 бита, m – 32 бита. Итого 44 бита при ширине выборки данных из памяти 32 бита.

В этом случае для выборки одной команды требуется не менее двух обращений к памяти, что значительно уменьшает быстродействие.

Этим определяется стремление разработчиков уменьшить разрядность поля адреса в командах. Но здесь речь идет не об уменьшении адресного пространства программы (его всегда не хватает), а о более эффективной кодировке адресов данных.

Упрощение процедур обработки массивов

Обработка массива – это циклический процесс. Повторение тела цикла производится для новых элементов массива, поэтому в каждом цикле нужно задавать адрес очередного элемента.

В первых машинах для переадресации данных в массивах использовался способ изменения команд на сумматоре. Он заключался в том, что после каждого обращения к элементу массива, используемая команда обработки элемента массива выбиралась на сумматор как данные. К ее младшему разряду прибавлялась единица и результат (модифицированная команда) сохранялся в памяти для дальнейшего использования как команда с "продвинутым адресом операнда". Для первых ЭВМ эта процедура была единственным способом реализации процедуры обработки элементов массива в цикле. Но запись в командный сегмент несовместима с хранением программ в памяти с однократной записью (ПЗУ). Кроме этого, разрешение записи в командный сегмент часто приводит к ошибкам с тяжелыми последствиями. В современных процессорах, например, в МП Intel запись в кодовый сегмент в защищенном режиме запрещена.

Решить указанные проблемы (уменьшение разрядности поля адреса и упрощение процедур обработки массивов) можно декомпозицией адреса на компоненты. При этом часть компонент адреса (базовый адрес и индекс) можно хранить вне команды, например, в РОНах, а в самой команде указывать только короткие адреса используемых РОНов, т.е. применять косвенную адресацию.

Такое решение позволяет:

модифицировать адреса команд в циклах, изменяя компонент адреса (индекса, хранящегося в РОНе), и не модифицируя саму команду,

указывать в команде только короткий компонент адреса (адрес РОНа), где сохраняется 32-битовый адрес, а не полноразмерный адрес текущего элемента массива.

Для примера рассмотрим 32-разрядную структуру команды типа регистр-память процессора фирмы IBM (Семейство IBM/360). Структура команды представлена на рис. 2.9.

|

Код операции (8 бит.) |

№ РОН (4бит) |

Адрес операнда в памяти (20 разрядов) | |

|

|

|

| |

|

|

В (4бит) |

X (4бит) |

Смещение (D– 12 разрядов ) |

|

Рис. 2.9. структура команды регистр/память IBM-360 | |||

Команда (рис.2.9) двухадресная и содержит три поля:

поле кода операции (8 бит),

поле задания номера РОНа (4 бита), содержащего первый операнд (процессор содержит шестнадцать 32-битных регистров общего назначения),

поле адреса второго операнда в оперативной памяти (20 бит).

Адрес памяти задается тремя компонентами: базовым адресом кадра (B), индексом (Х) и смещением (D). Соответственно, поле адреса операнда в памяти содержит три поля:

четырехбитное поле базы (B) задает номер РОНа (кроме нулевого), содержащего базовый адрес кадра данных,

четырехбитное поле индекса (Х) задает номер РОНа (кроме нулевого), содержащего индекс (смещение адреса элемента в массиве),

двенадцатибитное поле смещения (D) задает адрес первого элемента массива относительно базового адреса кадра данных.

Это базово-индексная адресация со смещением.

Нулевое значение полей B, X или D означает отсутствие этих компонентов адреса. Структура памяти с базово-индексной адресацией представлена на рис. 2.10.

Рассмотрим случай, когда вторым операндом является элемент Аi массива А размерности n (А[n]), (см. рис. 2.10.).

Для задания элемента массива его адрес в памяти разбивается на три компонента:

базовый адрес кадра (окна) данных – (В),

смещение начала массива а кадре данных – (D),

смещение элемента в массиве (Х).

База (четырехбитное поле B) задает РОН, в котором находится 32-битный начальный адрес кадра, общий для всех данных кадра.

Прямой двенадцатибитный адрес смещения D задает адрес программного объекта относительно начала кадра (окна) данных (размер кадра здесь выбран 212 = 4096 байт).

Задание базового адреса В – это дополнительная команда (загрузки базового адреса в РОН), но ее результат позволяет использовать короткие шестнадцатибитные адреса (четырехбитный номер РОНа и двенадцатибитное смещение) для всех данных кадра.

Третий компонент (Х) индекс используется при обработке массивов. Его введение решает проблему переадресации данных в цикле без изменения команд на сумматоре.

На рис. 2.10 операндом является элемент массива Ai. Для задания его адреса дополнительно используется третий компонент адреса. Это четырехбитное поле, содержащее адрес РОНа, в котором хранится смещение элемента Ai в массиве A[n]. Номер элемента i связан со значением Х2 следующим соотношением:

Х2 = i L, где L - длина операнда в байтах.

При базово-индексной адресации возможны два варианта вычисления адреса элемента массива:

с последовательной выборкой элементов массива,

с выборкой элементов массива в произвольном порядке.

В первом случае смещение элемента в массиве вычисляется по формуле: Х2 (i) := X2 (i+1), при Х2(0) = 0.

Поле Х2 увеличивает разрядность адреса второго операнда, но решает проблему переадресации элементов массива (при переборе элементов массива) в циклических программах без использования записи в программный код.

Во втором случае смещение элемента в массиве вычисляется по формуле:

Х2 (i) := i L

Формирование адресов при базово-индексной адресации (с последовательной выборкой элементов массива) производится по схеме (рис.2.11):

Адрес элемента массива = Содержимое РОНа X2 + Содержимое РОНа B2 + Смещение D2.

Задавая нулевые значения полей Х, В или D можно получать:

относительно-базовую адресацию – (В)+D,

индексную адресацию – (Х)+D,

относительно-индексную адресацию (В)+(Х) без смещения,

прямую адресацию – D.

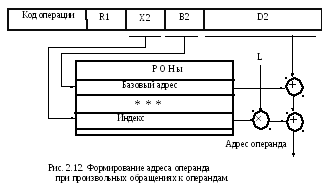

Формирование адресов при базово-индексной адресации (с произвольной выборкой элементов массива) производится по схеме (рис.2.12).

А дрес

элемента массива = Содержимое РОНа X2*L+

Содержимое РОНа B2 + Смещение D2.

дрес

элемента массива = Содержимое РОНа X2*L+

Содержимое РОНа B2 + Смещение D2.

Кроме указанных видов адресации возможны (например в МП PDP-11 фирмы DEC) дополнительные способы задания адресов данных:

адресации с автоиндексированием. В этих адресациях после использования адреса значение индекса автоматически изменяется на размер операнда в байтах, т.е. определяет адрес следующего элемента массива.

адресации (данных или точек переходов) относительно счетчика команд; это позволяет использовать короткие относительные адреса и формировать перемещаемые программы (безразличные к физическим адресам загрузки).

Если системы имеют несколько систем адресаций, то режимы адресаций могут задаваться:

кодом операции (процессор фирмы IBM),

полем режима адресации для каждого адреса в команде (процессор фирмы DEC),

общим полем режима адресации для всех адресов в команде – постбайтом (процессор фирмы Intel).

Вопросы для самопроверки.

1. Понятие "режим адресации".

2. Причина сокращения разрядности адресных полей при задании адресов компонентами.

3. Причина упрощения обработки элементов массива при задании адресов компонентами.

4. Основные компоненты адреса объекта в памяти.

5. Основные виды адресации с использованием трех компонентов адреса.