Архитектура микросхем ПЛИС семейства Cyclone II

Логические элементы

Логические элементы (далее ЛЭ) являются наименьшим элементом логики в ПЛИС (англ. – LE – logical element). Основными харктеристиками ЛЭ являются:

-

Наличие четырехвходовой таблицы соответствия (англ. LUT – look up table), на которых может быть реализована любая логическая функция 4-х переменных;

-

Наличие программируемого триггера;

-

Наличие цепи ускоренного переноса(?);

-

Наличие цепи сединения триггеров в цепочку;

-

Способность управлять всеми типами межсоединений: локальными, столбцами, строками, register chain, прямыми межсоединениями

-

Хх независимая работа таблиц соответствия и триггеров (register packing)

-

Хх

Функциональная схема ЛЭ приведена на рисунке 1.

Рисунок 1

Каждый триггер ЛЭ имеет входы данных, тактирования, разрешения, сброса и может быть сконфигурирован как D, T, JK, RS.

Каждый ЛЭ имеет три выхода, которые могут управлять локальными, вертикальными и горизонтальными ресурсами разводки. В свою очередь к этими выходам подключаются и могут управлять независимо либо таблица соответствия, либо триггер. Два из этих выходов ЛЭ выходят на вертикальные, горизонтальные ресурсы разводки, а также на ресурсы прямых межсоединений, третий выход выходит на локальные ресурсы трассировки, позволяя таблице соответствия работать независимо от триггера. Эта особенность повышет эффективность использования ресурсов ПЛИС, т.к. таблицы соответствия и триггеры могут использоваться для реализации независимых функций. Еще одна особенность ЛЭ – наличие обратной связи, когда выход триггера соединяется со входом таблицы соответствия. Т.к. оба элемента находятся в одном ЛЭ, это еще более повышает эффективность использования ресурсов. Кроме перечисленных трех выходов. ЛЭ имеет еще один – register chain output -, который позволяет соединять триггеры ЛЭ, находящихся в одном КЛБ в сдвиговый регистр, экономя локальные трассировочные ресурсы и повышая скорость работы устройства.

ЛЭ могут работать в двух режимах: нормальном и арифметическом. Нормальный режим применяется для создания комбинационых функций, арифметический режим является идеальным для реализации сумматоров, счетчиков, аккумуляторов и компараторов. ЛЭ в арифметическом режиме релизует 2-х битный полный сумматор. В обоих режимах можно использовать register packing и цепь обратной свяци от триггера в таблицу соответствия.

Про carry chain

Конфигурационные логические блоки

Каждый кофигурационный логический блок (далее – КЛБ) состоит из:

-

16-ти ЛЭ

-

контрольных сигналов КЛБ

-

цепи ускоренного переноса ЛЭ

-

цепочки регистров

-

локальных межсоединений.

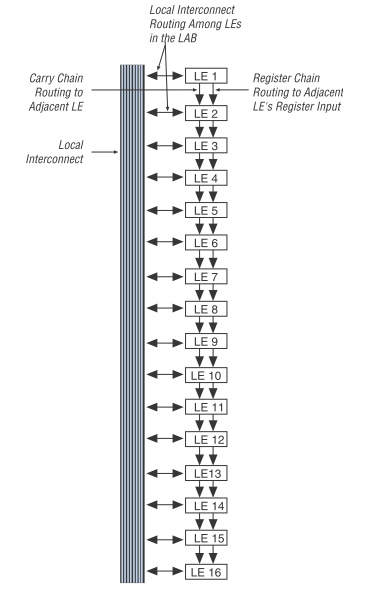

Локальные межсоединения передают сигналы между ЛЭ одного КЛБ. Соединения цепочки тригеров передают выход регистра одного ЛЭ в регистр соседнего ЛЭ. Компилятор среды Quartus II автоматически размещает логические функции внутри одного КЛБ или нескольких соседних, используя при этом локальные межсоединения и соединения цепочки триггеров для увеличения производительности (англ. performance) и уменьшения числа занимаемых ресурсов (area efficiency).

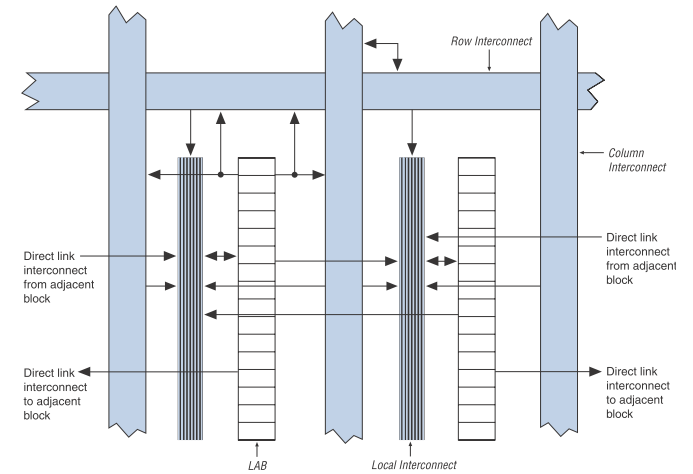

Рисунок 2

Локальные межсоединения КЛБ могут быть источником сигналов для ЛЭ внутри одного КЛБ. Сами локальные межсоединения управляются вертикальными и горизонтальными линиями соединений или выходами ЛЭ этого КЛБ. Соседние КЛБ, PLL, M4K RAM и встроенные умножители также могут управлять локальными межсоединениями КЛБ через прямые соединения. Использование этих прямых соединений повышает производительность, минимизируя использование горизонтальных и вертикальных линий связи. Каждый ЛЭ может выдавать сигнал на 48-м ЛЭ через быстрые локальные или прямые межсоединения. На рисунке 3 показано такое прямое соединение.

Рисунок 3

Каждый КЛБ содержит встроенную логику для управления контрольными сигналами ЛЭ. Такими сигналами являются:

-

Два тактовых входа

-

Два входа разрешения

-

Два входа асинхронного сброса

-

Вход синхронного сброса

-

Вход синхронной установки.

Синхронная установка и синхронный сброс используются для реализации счетчиков и других функций. Эти сигналы одновременно управляют всеми триггерами КЛБ. Каждый КЛБ может использовать два сигнала тактирования и два сигнала разрешения тактирования. Эти сигналы являются связанными, т.е. если ЛЭ использует сигнал тактирования labclk1, то им используется и сигнал разрешения labclkena1.

Межсоединения MultiTrack

Соединения между ЛЭ, блоками памяти M4K, встроенными умножителями, а также выводами микросхемы обеспечиваются MultiTrack структурой межсоединений, выполненных по технологии DirectDrive. Эта структура состоит из длинных, оптимизированных линий разводки, используемых для внутриблочных и межблочных соединений. Технология DirectDrive гарантирует эквивалентное использование ресурсов разводки для любых функций независимо от их положения в кристалле.

Структура межсоединений MultiTrack состоит из строк (прямые соединения, R4, R24) и столбцов (триггерные цепочки, C4, С16) межсоединений, имеющих определенную длину.

Встроенные строки межсоединений – горизонтальные ресурсы разводки – соединяют сигналы между КЛБ, PLL, блоками M4K, встроенными умножителями, которые располагаются в одной строке. Эти строки состоят из:

-

Прямых межсоединений между КЛБ и соседними блоками,

-

R4 межсоединений, распространяющихся на четыре блока вправо и влево

-

R24 межсоединений для быстрых соединений через весь кристалл.

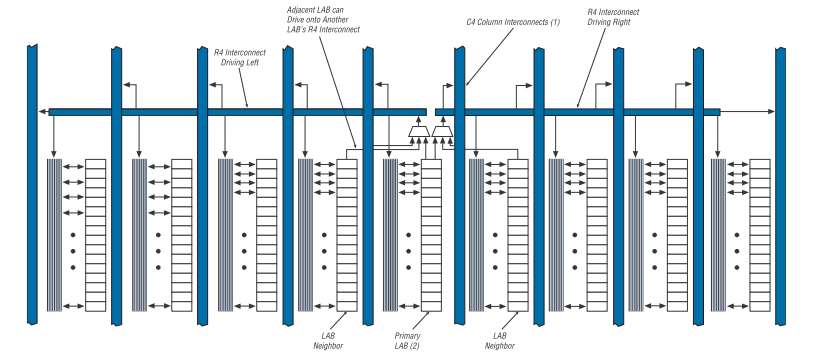

Прямые соединения позволяют блокам ПЛИС соединяться с соседними блоками справа и слева без использования горизонтальных ресурсов разводки, составляющих строки R4 и R24. Межсоединения R4 распространяются на четыре КЛБ, три КЛБ и один блок памяти M4K или три КЛБ и оди встроенный умножитель. Эти ресурсы разводки используются для быстрых горизонтальных соединений в пределах четырех блоков. На рисунке 4 показана топология R4 межсоединений.

Рисунок 4

Межсоединения могут управлять и управляться КЛБ, блоками памяти M4K, встроенными умножителями, PLL блоками и строками ЭВВ. Также межсоединения R4 могут управлять другими межсоединениями R4, увеличивая диапазон соединения одного КЛБ, R24 межсоединениями и C4, C16 межсоединениями для соединений из одной строки в другую. Строки межсоединений R24 распространяются на двадцать четыре КЛБ, обеспечивая быстрые соединения по всей длине кристалла, а не только между соседними КЛБ. Эти строки межсоединений могут управляться другими строками и столбцами.

Столбцы межсоединений аналогичны строкам. Каждая колонка КЛБ обслуживается встроенной колонкой межсоединений, которая разводит сигналы о вертикали между КЛБ, блочной памятью, встроенными умножителями, строками и столбцами ЭВВ. Эти вертикальные ресурсы разводки включают в себя:

-

межсоединения для триггерной цепочки внутри одного КЛБ,

-

межсоединения C4, распространяющиеся от каждого КЛБ вверх и вниз на четыре блока,

-

межсоединения C16 для быстрых соединений, проходящие через весь кристалл микросхемы.

Структура триггерных межсоединений приведена на рисунке 5. Эти месоединения располагаются внутри КЛБ и соединяют выход одного ЛЭ со входом другого для образования быстрых сдвиговых регистров. С4, подобно R4, могут соединять все типы блоков в ПЛИС, а также соединяться друг с другом для образования длинных соединений.

С16 – аналогично R14 распространяются на 16 КЛБ.

Рисунок 5

Рисунок 6

Глобальная тактовая сеть и PLL (ФАПЧ)

Глобальная тактовая сеть состоит из:

-

до 16-ти глобальных тактовых цепей,

-

до 4-х блоков PLL,

-

цепи динамического выбора источника тактовых сигналов,

-

цепи динамического разрешения/запрещения тактовых сигналов.

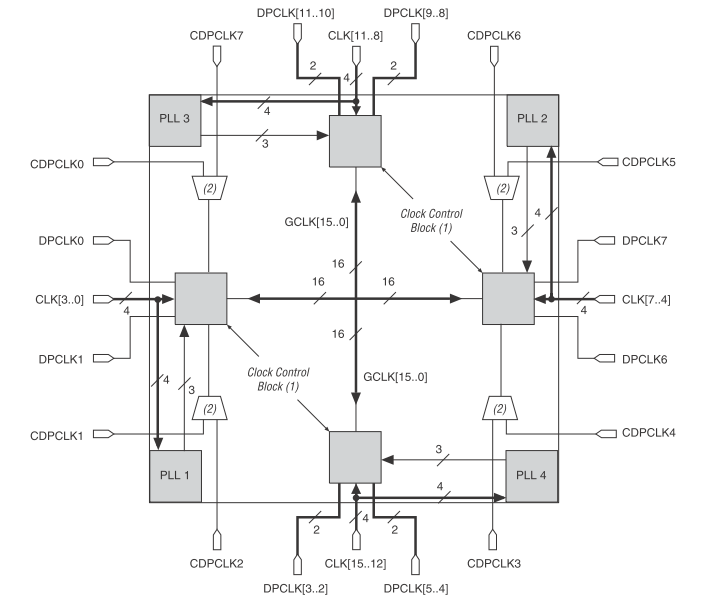

Каждая глобальная тактовая wtm уравляется блоком контроля, который осуществляет выбор источника тактовых импульсов, которым может быть блок PLL, выводы CLK и DPCLK микросхемы, внутренняя логика. На рисунке 7 показано расположение блоков PLL, выводов CLK и DPCLK, а также блоков контроля микросхемы EP2C20.

Рисунок 7

Тактовые выводы ПЛИС

Микросхемы семейства Cyclone II имеют разное количество тактовых выводов. Старшие в семействе микросхемы, в том числе EP2C20, имеют 16 тактовых выводов. Эти выводы на рисунке 7 обозначены как CLK. С каждой стороны микросхме расоложоено по четыре вывода. Эти выводы непосредственно связаны с глобальными тактовыми цепями. Если тактовые выводы не используются для тактирования, они могут исользоваться как входы/выходы общего назначения, которые соединяются с массивом КЛБ и других встроенных блоков ПЛИС через MultiTrack межсоединения. Однако при таком их использованииони для них не поддерживается использование регистров ввода вывода (I/O registers) и в данном качестве должны использоваться регистры, расположенные в ЛЭ.