- •1. Конфигурируемая система на кристалле e5 компании Triscend

- •2. Основные аппаратные блоки семейства е5

- •2.1. «Ускоренный» 8051 микроконтроллер

- •2.2 Контроллер прямого доступа к памяти (dma)

- •2.3. Конфигурируемая системная шина (csi)

- •2.4. Конфигурируемая логическая матрица (csl)

- •2.5. Программируемые порты ввода/вывода (pio)

- •2.6 Блок сопряжения с внешней памятью miu

- •2.7. Адресные координаторы

- •Значения старших байтов адреса адресных координаторов Таблица 23

- •2.8 Система отладки

- •2.9. Блок конфигурирующих регистров (cru)

- •2.10. Режимы конфигурации системы

- •2.11. Система тактирования

- •2.11. Архитектура микроконтроллера

- •2.12. Набор команд для управления системой

- •2.13. Система прерываний

- •2.14. Условия системного сброса

- •Содержимое регистров sfr после сброса Таблица 40

- •2.15. Блок управления энергопотреблением

- •3. Словарь

- •4. Политика реализации системы на кристалле

- •5. Описание выводов для кристаллов серии е5

- •Выводы микросхемы семейства е5 и их назначение Таблица 43

- •6. Маркировка кристаллов компании Triscend

- •Te5 20 s 40 - 40 q c

- •7. Область применения cSoC устройств

2.9. Блок конфигурирующих регистров (cru)

Блок конфигурирующих регистров состоит из контрольных регистров для функций, размещенных в пределах конфигурируемой системы на кристалле. Для большинства приложений блок CRU занимает верхние 256 байт внешней памяти данных.

Контрольные регистры представлены в таблице 24. Неиспользуемые области не имеют функционального назначения и не являются ячейками памяти ОЗУ.

Блок конфигурирующих регистров Таблица 24

2.10. Режимы конфигурации системы

Подобно большинству процессорных единиц, система на кристалле Е5 нуждается в предварительной конфигурации прежде, чем устройство станет функциональным, и предлагает 4 различных метода конфигурации, представленных в таблице 25. Доступными оказываются как активные, так и пассивные методы конфигурации.

Методы конфигурации Таблица 25

|

Метод конфигурации |

Позиция метода |

Источник данных |

|

Параллельный |

Активный |

Регистрово-параллельная Flash память |

|

Последовательный |

Активный |

ППЗУ с последовательной выборкой |

|

Безопасный |

Активный |

Внутреннее СПЗУ, питающееся от батареи |

|

Через JTAGинтерфейс |

Пассивный |

Компьютер (через порт JTAGинтерфейса) |

|

Подчиненный |

Пассивный |

Контроллер (через шинный интерфейс) |

В активном режиме конфигурации система сама обеспечивает сигналы управления, определяет направление передачи данных и контролирует внешние устройства.

В пассивном режиме передачу данных контролирует внешний контроллер.

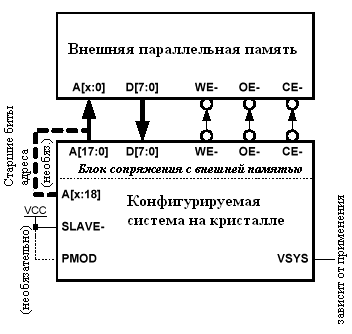

Параллельный режим конфигурации

Параллельный режим конфигурации, представленный на рис.37, позволяет пользователю хранить программы и осуществлять их выполнение из устройства стандартной восьмиразрядной параллельной внешней памяти. Данные конфигурации также содержатся в этой памяти. Процесс параллельной конфигурации протекает намного быстрее, чем процесс последовательной конфигурации, поскольку пользовательские программы не загружаются во внутреннее ОЗУ.

Рис.37. Параллельный режим конфигурации

Назначение сигналов:

D[7:0] – восьмиразрядная шина данных из устройства внешней памяти.

А[17:0] – младшие 18 разрядов адресной шины. При необходимости в пользовательском проекте адресная шина может быть расширена через вывод A[x:18].

WE –сигнал, разрешающий запись, предназначен для устройств памяти, доступных для записи: Flash, СППЗУ и СОЗУ.

ОЕ – сигнал, разрешающий вывод данных из устройства внешней памяти во время их считывания.

СЕ – сигнал активизации устройства внешней памяти.

Вывод PMOD во время конфигурации должен быть подтянут к уровню питания, что может быть осуществлено напрямую с помощью физического проводника либо через нагрузочный резистор во время процесса конфигурации.

Адресные линии A[17:0] предназначены для адресации памяти емкостью 256 Кбайт. Если в качестве устройства внешней памяти используется память большей емкости, то для расширения адресной шины используются дополнительные выводы, предназначенные для старших адресных битов A[x:18]. Микроконтроллер стандарта 8051 может непосредственно иметь доступ только к 64Кб кодовой памяти, тогда как ускоренный микроконтроллер конфигурируемой системы на кристалле Е5 обладает большими возможностями, располагая кодовыми координаторами, которые динамически изменяют базовый адрес микроконтроллера. Внешняя параллельная память может также содержать массивы данных в виде таблиц просмотра. С помощью координаторов данных внешняя память может быть определена как внешняя память данных процессора.

Режим параллельной конфигурации предполагает размещение какой-либо программы во внешней памяти, поскольку по окончании системной инициализации микроконтроллер приступит к выполнению программы с адреса 0000H внешней памяти. На начало выполнения программы кодовый координатор C1 будет ссылаться на область адресного пространства программ 0000H–7FFFH во внешней памяти. Пользовательский код должен инициализировать кодовые координаторы и координаторы данных.

В процессе конфигурации выводы портов ввода/вывода, неиспользуемые интерфейсом параллельной памяти, подтягиваются с помощью нагрузочных резисторов к уровню логической единицы, а по окончании процесса принимают конфигурацию, определенную в пользовательском проекте.

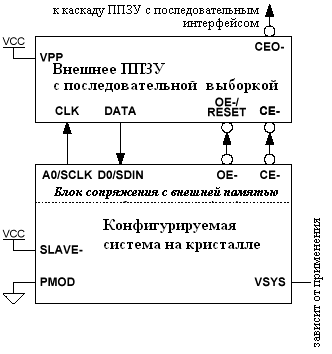

Последовательный режим конфигурации

Последовательный режим конфигурации, представленный на рис.38, предполагает размещение пользовательской программы и данных конфигурации во внешнем ППЗУ с последовательной выборкой, аналогично устройствам, используемым для программирования FPGA устройств. ППЗУ с последовательным интерфейсом отличается от последовательного ППЗУ формата I2C или SPI тем, что последние не адресуемы и обычно обладают большей плотностью.

В процессе последовательной конфигурации системы большинство выводов блока сопряжения с внешней памятью остаются незадействованными и могут быть использованы как выводы порта в пользовательском проекте. На рис.38 представлена картина взаимодействия конфигурируемой системы на кристалле и устройства внешней памяти с последовательным интерфейсом.

Организация интерфейса системы с памятью последовательного типа требует наличие четырех сигналов:

D0/SDIN – бит последовательных данных из внешнего ППЗУ.

А0/SCLK – сигнал синхронизации устройства внешней памяти.

ОЕ/SRST – сигнал сброса ППЗУ на стартовый адрес, если ОЕ/SRST=1, или сигнал разрешения вывода последовательных данных, если ОЕ/SRST=0.

СЕ – сигнал активизации устройства внешней памяти.

Рис.38. Последовательный режим конфигурации

Вывод PMOD во время конфигурации должен быть подтянут к уровню логического нуля для определения последовательного режима конфигурации. При этом вывод SLAVE- должен быть подтянут к уровню питания, чтобы гарантировать запуск системы в однокристальном режиме, самостоятельно определяющей для себя процесс конфигурации и не ссылающейся на другой интеллектуальный контроллер для обеспечения системы данными конфигурации.

После сброса при включении питания или другого системного сброса, система на кристалле автоматически определит режим конфигурации и начнет процесс выгрузки последовательных данных конфигурации в логическую матрицу. По окончании системной инициализации во внутреннее ОЗУ системы будет загружена пользовательская программа.

Режим последовательный конфигурации предполагает наличие программы во внутреннем ОЗУ системы, поскольку микроконтроллер начнет выполнение пользовательского кода с адреса 0000H внутренней памяти. На начало выполнения программы кодовый координатор C1 будет ссылаться на целую область адресного пространства программ во внутреннем ОЗУ размером 64Кб. Значения координаторов данных должны быть определены пользовательским кодом.

В процессе конфигурации выводы портов ввода/вывода и блока MIU, неиспользуемые в сопряжении с устройством с внешней памятью, подтягиваются с помощью нагрузочных резисторов к уровню логической единицы, а по окончании процесса принимают конфигурацию, определенную в пользовательском проекте.

Режим конфигурации через JTAG интерфейс

Процесс конфигурации системы через JTAG интерфейс предполагает наличие внешнего тестирующего устройства, персонального компьютера или другой интеллектуальной единицы, способной управлять процессом конфигурации, задавать управляющие команды и анализировать текущее состояние системы. Порт JTAG интерфейса используется для проведения отладочных мероприятий или для программирования устройств внешней памяти через блок сопряжения MIU. Если для конфигурации системы используется персональный компьютер, то блок JTAG интерфейса будет управляться серией команд разработанной компанией Trisend системы FastChip либо другого независимого аппаратного отладчика.

Этот метод конфигурации не предполагает использование каких-либо устройств внешней памяти, поскольку средства связи блока JTAG интерфейса позволяют напрямую инициализировать логическую матрицу, загрузить необходимую программу во внутреннее ОЗУ системы, задать значения кодовым координаторам и координаторам данных и направить микроконтроллер на выполнение кода во внутреннем системном ОЗУ.

Рис.39. Режим конфигурации через блок JTAG интерфейса

В этом режиме конфигурации любое устройство внешней памяти может быть допущено с момента использования блока JTAG интерфейса в качестве системного отладчика.

На рис.39 представлена стандартная конфигурация связи внешнего отладчика и системы на кристалле через порт JTAG интерфейса, при этом, как видно из рисунка, конфигурируемая система уже соединена с устройством внешней параллельной памяти. Порт JTAG интерфейса соответствует стандарту IEEE 1149.1, и четыре его вывода предназначены только для функций блока JTAG.

ТСК – сигнал тестовой синхронизации, если не используется, то вывод должен быть подтянут к уровню логической единицы.

TMS – сигнал выбора тестового режима, если не используется, то вывод должен быть подтянут к уровню логической единицы.

TDI – ввод тестовых данных в систему, если не используется, то вывод должен быть подтянут к уровню логической единицы

TDO – вывод тестовых данных из системы.

Блок JTAG интерфейса является мастером на системной шине и имеет доступ для чтения и записи к каждому адресуемому объекту системы.

Порт JTAG интерфейса контролирует работу микроконтроллера, назначив точки останова, по достижению которых работа микроконтроллера будет прекращена. Как только процессор будет «заморожен», блок JTAG интерфейса может перевести его в режим пошагового выполнения команд для проверки его внутренних регистров, после чего вернуть к нормальной работе.

При непосредственном участии микроконтроллера порт JTAG интерфейса может быть также использован для программирования устройства внешней Flash памяти. В режиме программирования блок JTAG интерфейса перемещает программные и тестовые алгоритмы во внутреннюю память ОЗУ системы, где могут быть размещены и новые данные для программирования Flash памяти. После того, как кодовые координаторы и координаторы данных будут соответствующим образом определены через порт JTAG интерфейса, микроконтроллер сможет приступить к выполнению всех алгоритмов, необходимых для организации записи новых данных в устройство внешней Flash памяти. При этом процессор будет взаимодействовать с блоком JTAG интерфейса через флаги и коллективные переменные или через прерывания.

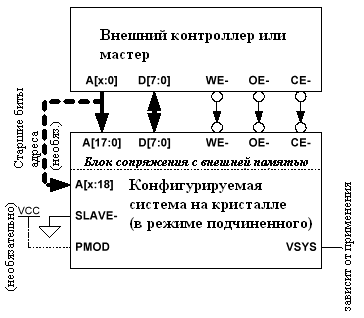

Пассивный режим конфигурации. Метод подчиненного

Этот метод предполагает загрузку данных конфигурации в систему через восьмиразрядный интерфейс, представленный на рис.40. Внешний контроллер, микропроцессор или мастер-устройство компании Trisend обращается к конфигурируемой системе на кристалле, как к подчиненному, c помощью сигнала СЕ. Для инициализации одной микросхемы требуется до 18 адресных линий. При необходимости адресная шина может быть расширена до 32 битов. Внешний контроллер предоставляет адрес, данные и необходимые сигналы управления.

Ведущий контроллер и ведомая конфигурируемая система на кристалле могут работать от одного и того же внешнего источника тактовых сигналов.

После инициализации ведущий контроллер выводит систему из состояния сброса, установив бит SRST_DIS в ее контрольном регистре MISC, после чего работа микроконтроллера возобновляется, но уже в условиях пассивной системы. Тем не менее, микроконтроллер не может позволить выполнение выборок внешнего кода, поскольку это противоречит его структуре, но способен выполнять команды ведущего контроллера, которые предварительно были загружены во внутреннее ОЗУ системы.

Рис.40 Пассивный режим конфигурации

Безопасный режим конфигурации

Конфигурируемая система на кристалле имеет регистр безопасности, разрешающий пользователям блокировать внешний доступ к системе через блок MIU или запретить выполнение протоколов системной шины блоку JTAG интерфейса. Этот режим конфигурации незаменим в случае питания функциональных узлов системы от батареи при отсутствии внешнего питания. В этом режиме данные конфигурации предварительно загружаются в память системы, и прикладной код выполняется из внутреннего ОЗУ. После того, как бит безопасности будет установлен, все операции системы станут невидимыми для внешнего наблюдения.

После восстановления питания, когда система находится в безопасном режиме, она начинает выполнение программы из памяти внутреннего СОЗУ.

Пользователь блокирует внешний доступ через блок MIU, тем самым, ориентируя микроконтроллер на выполнение кода только из памяти внутреннего ОЗУ. При этом выполняемая программа оказывается защищенной от выборок внешнего кода и данных, поступающих через порт блока сопряжения с внешней памятью, а хакеры лишаются возможности следить за программным потоком с момента, как только блок MIU окажется отключенным от системы.

Ограждение блока JTAG интерфейса от выполнения протоколов системной шины исключает возможность внешнего отладчика считать конфигурацию системы и код в ее памяти. После установки бита безопасности для блока JTAG интерфейса сканирование выводов будет продолжаться, не смотря на то, что выполнение протоколов системной шины окажется невозможным. При этом статус бита безопасности может быть считан через порт блока JTAG интерфейса.

Все случаи системного сброса оказываются недействительными для системы в безопасном режиме, кроме прикладного внешнего сигнала RSTC, который сохраняет свою функциональность даже в безопасном режиме. С его появлением на соответствующем выводе микросхемы микроконтроллер начинает выполнение программы со стартового адреса 0000H. Все случаи сброса микроконтроллера остаются функциональными.

Однажды установленные биты безопасности могут быть очищены только после выключения питания. Установленный бит безопасности для блока MIU способствует тому, что системный следящий уровень напряжения VSYS будет проигнорирован, и доступ к устройству внешней памяти через порт блока MIU будет запрещен.

Регистр синхронизированного доступа к регистру безопасности

Мнемоника: PROTECT Адрес:FF60H

Регистр синхронизированного доступа к регистру безопасности (PROTECT) предназначен для организации доступа к битам, отвечающим за безопасный режим системы. Аналогичный существует регистр синхронизированного доступа к контрольному регистру сторожевого таймера (ТА), который также контролирует доступ к защищенным от случайной записи битам.

Для доступа к битам безопасности пользователь должен предварительно записать в регистр PROTECT значение AAH, после чего незамедлительно записать значение 55H. Эти действия позволят открыть окно из трех машинных циклов, в течение которых охраняемые биты могут быть изменены программным обеспечением.

При чтении регистр PROTECT возвращает значение FFH.

Этот регистр обладает неограниченным доступом для записи. Операция чтения не требуется.

Регистр безопасности

![]()

Мнемоника:SECURITY Адрес: FF61H

Биты SECURITY.7-2 зарезервированы и при считывании возвращают значение логического нуля.

Бит MIU, когда установлен, запрещает любой доступ через порт блока сопряжения с внешней памятью и осуществлять микроконтроллеру выполнение выборок кода из внешней памяти. Очистка бита MIU возможна только после отключения питания.

Бит JTAG, когда установлен, запрещает любой доступ через порт JTAG интерфейса. Очистка бита JTAG возможна только после отключения питания.

Доступ к регистру безопасности может быть осуществлен только в случае правильной реализации синхронизированной записи двух предусмотренных значений в регистр доступа к регистру безопасности, т.е. в регистр PROTECT. Эти значения следует записывать в определенном порядке, сначала AAH, потом 55H, для чего предусмотрено два цикла записи. Ошибочное значение данных или неверный порядок их предоставления приведет к сбросу механизма доступа к регистру безопасности SECURITY. В случае правильно реализованного доступа регистр SECURITY окажется доступным для модификации на один цикл записи.

Биты MIU и JTAG принимают активное состояние после записи в них значения логической единицы. Сброс битов возможен только после отключения питания. Микроконтроллер всегда может прочитать значение регистра безопасности SECURITY для того, чтобы определить или проверить состояние безопасного режима системы.

Размер данных конфигурации

Размер файла данных конфигурации зависит от типа устройства семейства E5 и от используемого метода конфигурации.

Каждое устройство располагает определенным числом колонок и столбцов для предоставления информации о конфигурации, которые и определяют общий размер данных, как показано в таблице 26.

Размер данных конфигурации Таблица 26

|

Устройство |

Число колонок |

Число строк |

Всего байт |

|

ТЕ502 |

102 |

120 |

12240 |

|

ТЕ505 |

102 |

208 |

21216 |

|

ТЕ512 |

144 |

296 |

42624 |

|

ТЕ520 |

186 |

384 |

71424 |

|

ТЕ532 |

228 |

472 |

107616 |

Второстепенная программа конфигурации для параллельного режима

Второстепенная программа конфигурации загружается в устройство Е5 вместе с данными конфигурации и состоит из команд микроконтроллера стандарта 8051. Общий размер данных второстепенной программы конфигурации для параллельного режима конфигурации определяется следующим образом:

967 байт команд, предназначенных для организации процесса загрузки данных конфигурации в устройство;

19 байт заголовочной и заключительной частей программы;

файл данных конфигурации, определяемый согласно таблице 26;

94 байта команд, предназначенных для формирования адресных и кодовых координаторов после загрузки данных конфигурации.

Поскольку второстепенная программа конфигурации всегда размещается в пределах верхней части внешней памяти, размером 256 Кб и разделенной на области по 16 Кб, то абсолютный размер данных оказывается больше, чем фактический. В таблице 27 представлены итоговые значения размера памяти, необходимой для сохранения второстепенной программы конфигурации, с учетом самой программы и требований по распределению памяти на области по 16Кб.

Требования к памяти в параллельном режиме Таблица 27

|

Устройство |

Размер данных вторичной конфигурации |

Требования к общей памяти |

|

ТЕ502 |

13320 |

16К |

|

ТЕ505 |

22296 |

32К |

|

ТЕ512 |

43704 |

48К |

|

ТЕ520 |

72504 |

80К |

|

ТЕ532 |

108696 |

112К |

Время конфигурации системы на кристалле Е5

Время конфигурации определяется типом используемой микросхемы семейства Е5 и ее тактовой частотой. После сброса системы при включении питания или сброса внешним сигналом RST начинается процесс ее конфигурации, синхронизируемый внутренним генератором. Частота внутреннего генератора колеблется в пределах 5 – 20 МГц. В процессе конфигурации источником тактовых сигналов также может быть внешний генератор или внутренний генератор, стабилизированный внешним кварцевым резонатором, оба из которых поддерживают частоту в пределах 25 - 40 МГц.

В таблице 28 представлены значения затрачиваемого времени конфигурации системы, использующей различные источники тактовых сигналов. В случае использования внутреннего генератора, стабилизированного внешним кварцевым резонатором, к значению времени, представленного в таблице, прибавляется 5 мс установочного времени кристалла. А при использовании специального режима синхронизации системы от внутреннего генератора, стабилизированного внешним кварцевым резонатором, с частотой 32 КГц – прибавляется 200 мс установочного времени.

Предполагаемое время конфигурации системы в параллельном режиме при различных значениях тактовой частоты

Таблица 28

|

Устройство |

Частота шины тактирования | |||

|

1МГц |

5МГц |

25МГц |

40МГц | |

|

ТЕ502 |

94 мс |

19 мс |

4,5 мс |

3,1 мс |

|

ТЕ505 |

112 мс |

23 мс |

5,2 мс |

3,6 мс |

|

ТЕ512 |

181 мс |

37 мс |

8 мс |

5,3 мс |

|

ТЕ520 |

265 мс |

54 мс |

11,4 мс |

7,4 мс |

|

ТЕ532 |

364 мс |

73 мс |

15,3 мс |

9,9 мс |

Управление VSYS

После сброса при включении питания или других аппаратных сбросов конфигурируемая система на кристалле начинает процесс конфигурации в соответствии с таблицей 39. Вывод микросхемы VSYS предопределяет поведение системы в случае, когда действительные внешние данные конфигурации не будут найдены.

Если в процессе конфигурации на выводе VSYS будет удерживаться значение логической единицы, то после неудачной попытки конфигурации система автоматически перейдет в режим Power Dawn. Для перезапуска процесса конфигурации потребуется очередной сброс системы, вызванный включением питания или другим системным событием.

Если в процессе конфигурации на выводе VSYS будет удерживаться значение логического нуля, то после неудачной попытки конфигурации система попытается перезапустить процесс. Режим конфигурации, последовательный или параллельный, определяется через вывод PMOD. Если вывод VSYS подключить к земле, то система будет сама перезапускать процесс конфигурации до тех пор, пока не будут найдены действительные данные конфигурации. Этот вариант очень удобен, если система работает в шумной среде.

! Вывод VSYS должен быть подключен к одному из логических уровней. Нельзя оставлять вывод не подключенным.

В приложениях, использующих системный управляющий чип, вывод VSYS может быть подключен к выводу VCC управляющей микросхемы, чтобы гарантировать запуск процесса конфигурации системы только в случае, когда уровень VCC будет находиться в определенном действующем диапазоне напряжений.

При установленном бите безопасности MIU положение вывода VSYS окажется проигнорированным, и конфигурируемая система на кристалле не будет иметь доступ к внешней памяти через порт блока сопряжения с внешней памятью.