- •16. ADVANCED LADDER LOGIC FUNCTIONS

- •16.1 INTRODUCTION

- •16.2 LIST FUNCTIONS

- •16.2.1 Shift Registers

- •16.2.2 Stacks

- •16.2.3 Sequencers

- •16.3 PROGRAM CONTROL

- •16.3.1 Branching and Looping

- •16.3.2 Fault Detection and Interrupts

- •16.4 INPUT AND OUTPUT FUNCTIONS

- •16.4.1 Immediate I/O Instructions

- •16.4.2 Block Transfer Functions

- •16.5 DESIGN TECHNIQUES

- •16.5.1 State Diagrams

- •16.6 DESIGN CASES

- •16.6.1 If-Then

- •16.6.2 Traffic Light

- •16.7 SUMMARY

- •16.8 PRACTICE PROBLEMS

- •16.9 PRACTICE PROBLEM SOLUTIONS

- •16.10 ASSIGNMENT PROBLEMS

- •17. OPEN CONTROLLERS

- •17.1 INTRODUCTION

- •17.3 OPEN ARCHITECTURE CONTROLLERS

- •17.4 SUMMARY

- •17.5 PRACTICE PROBLEMS

- •17.6 PRACTICE PROBLEM SOLUTIONS

- •17.7 ASSIGNMENT PROBLEMS

- •18. INSTRUCTION LIST PROGRAMMING

- •18.1 INTRODUCTION

- •18.2 THE IEC 61131 VERSION

- •18.3 THE ALLEN-BRADLEY VERSION

- •18.4 SUMMARY

- •18.5 PRACTICE PROBLEMS

- •18.6 PRACTICE PROBLEM SOLUTIONS

- •18.7 ASSIGNMENT PROBLEMS

- •19. STRUCTURED TEXT PROGRAMMING

- •19.1 INTRODUCTION

- •19.2 THE LANGUAGE

- •19.3 SUMMARY

- •19.4 PRACTICE PROBLEMS

- •19.5 PRACTICE PROBLEM SOLUTIONS

- •19.6 ASSIGNMENT PROBLEMS

- •20. SEQUENTIAL FUNCTION CHARTS

- •20.1 INTRODUCTION

- •20.2 A COMPARISON OF METHODS

- •20.3 SUMMARY

- •20.4 PRACTICE PROBLEMS

- •20.5 PRACTICE PROBLEM SOLUTIONS

- •20.6 ASSIGNMENT PROBLEMS

- •21. FUNCTION BLOCK PROGRAMMING

- •21.1 INTRODUCTION

- •21.2 CREATING FUNCTION BLOCKS

- •21.3 DESIGN CASE

- •21.4 SUMMARY

- •21.5 PRACTICE PROBLEMS

- •21.6 PRACTICE PROBLEM SOLUTIONS

- •21.7 ASSIGNMENT PROBLEMS

- •22. ANALOG INPUTS AND OUTPUTS

- •22.1 INTRODUCTION

- •22.2 ANALOG INPUTS

- •22.2.1 Analog Inputs With a PLC

- •22.3 ANALOG OUTPUTS

- •22.3.1 Analog Outputs With A PLC

- •22.3.2 Pulse Width Modulation (PWM) Outputs

- •22.3.3 Shielding

- •22.4 DESIGN CASES

- •22.4.1 Process Monitor

- •22.5 SUMMARY

- •22.6 PRACTICE PROBLEMS

- •22.7 PRACTICE PROBLEM SOLUTIONS

- •22.8 ASSIGNMENT PROBLEMS

- •23. CONTINUOUS SENSORS

- •23.1 INTRODUCTION

- •23.2 INDUSTRIAL SENSORS

- •23.2.1 Angular Displacement

- •23.2.1.1 - Potentiometers

- •23.2.2 Encoders

- •23.2.2.1 - Tachometers

- •23.2.3 Linear Position

- •23.2.3.1 - Potentiometers

- •23.2.3.2 - Linear Variable Differential Transformers (LVDT)

- •23.2.3.3 - Moire Fringes

- •23.2.3.4 - Accelerometers

- •23.2.4 Forces and Moments

- •23.2.4.1 - Strain Gages

- •23.2.4.2 - Piezoelectric

- •23.2.5 Liquids and Gases

- •23.2.5.1 - Pressure

- •23.2.5.2 - Venturi Valves

- •23.2.5.3 - Coriolis Flow Meter

- •23.2.5.4 - Magnetic Flow Meter

- •23.2.5.5 - Ultrasonic Flow Meter

- •23.2.5.6 - Vortex Flow Meter

- •23.2.5.7 - Positive Displacement Meters

- •23.2.5.8 - Pitot Tubes

- •23.2.6 Temperature

- •23.2.6.1 - Resistive Temperature Detectors (RTDs)

- •23.2.6.2 - Thermocouples

- •23.2.6.3 - Thermistors

- •23.2.6.4 - Other Sensors

- •23.2.7 Light

- •23.2.7.1 - Light Dependant Resistors (LDR)

- •23.2.8 Chemical

- •23.2.8.2 - Conductivity

- •23.2.9 Others

- •23.3 INPUT ISSUES

- •23.4 SENSOR GLOSSARY

- •23.5 SUMMARY

- •23.6 REFERENCES

- •23.7 PRACTICE PROBLEMS

- •23.8 PRACTICE PROBLEM SOLUTIONS

- •23.9 ASSIGNMENT PROBLEMS

- •24. CONTINUOUS ACTUATORS

- •24.1 INTRODUCTION

- •24.2 ELECTRIC MOTORS

- •24.2.1 Basic Brushed DC Motors

- •24.2.2 AC Motors

- •24.2.3 Brushless DC Motors

- •24.2.4 Stepper Motors

- •24.2.5 Wound Field Motors

plc advanced functions - 16.22

16.5 DESIGN TECHNIQUES

16.5.1 State Diagrams

The block logic method was introduced in chapter 8 to implement state diagrams using MCR blocks. A better implementation of this method is possible using subroutines in program files. The ladder logic for each state will be put in separate subroutines.

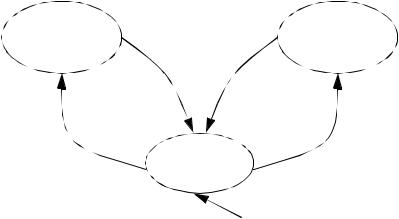

Consider the state diagram in Figure 16.23. This state diagram shows three states with four transitions. There is a potential conflict between transitions A and C.

STA |

STC |

B |

D |

A |

C |

|

STB |

|

first scan |

Figure 16.23 A State Diagram |

|

O:000/00 = STA O:000/01 = STB O:000/02 = STC

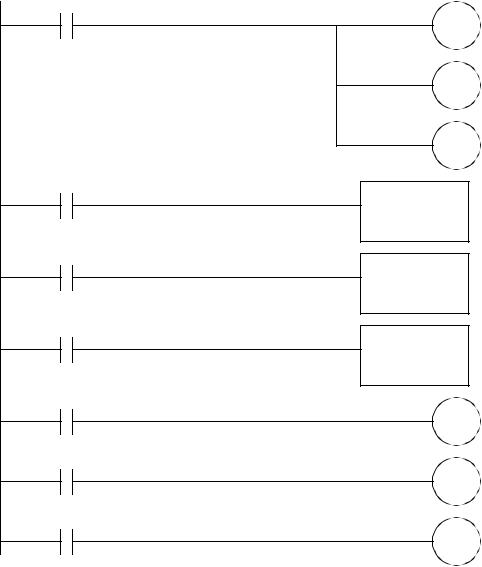

The main program for the state diagram is shown in Figure 16.24. This program is stored in program file 2 so that it is run by default. The first rung in the program resets the states so that the first scan state is on, while the other states are turned off. Each state in the diagram is given a value in bit memory, so STA=B3/0, STB=B3/1 and STC=B3/2. The following logic will call the subroutine for each state. The logic that uses the current state is placed in the main program. It is also possible to put this logic in the state subroutines.

plc advanced functions - 16.23

S2:1/15 - first scan

L B3/1 - STB

U B3/0 - STA

U B3/2 - STC

B3/0 - STA

JSR program 3

B3/1 - STB

JSR program 4

B3/2 - STC

JSR program 5

B3/0 - STA

L O:000/0

B3/1 - STB

L O:000/1

B3/2 - STC

L O:000/2

Figure 16.24 The Main Program for the State Diagram (Program File 2)

The ladder logic for each of the state subroutines is shown in Figure 16.25. These blocks of logic examine the transitions and change states as required. Note that state STB includes logic to give state C higher priority, by blocking A when C is active.

plc advanced functions - 16.24

Program 3 for STA

B

U B3/0 - STA

L B3/1 - STB

Program 4 for STB

C

U B3/1 - STB

L B3/2 - STC

A C

U B3/1 - STB

L B3/0 - STA

Program 5 for STC

D

U B3/2 - STC

L B3/1 - STB

Figure 16.25 Subroutines for the States

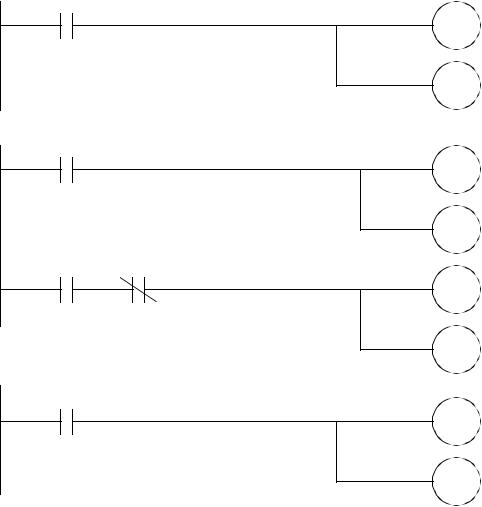

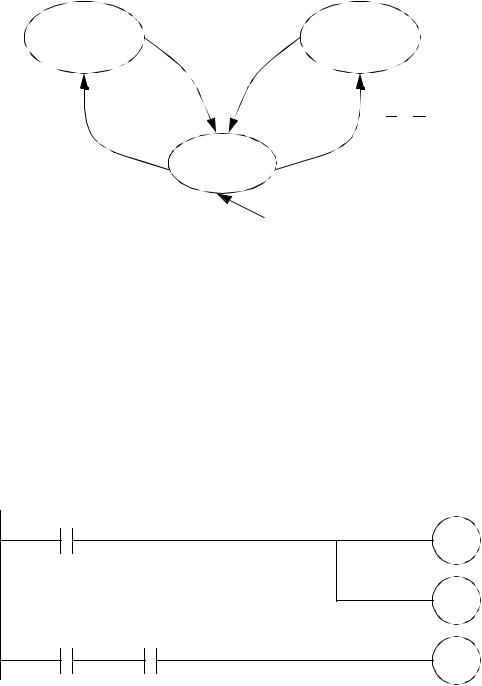

The arrangement of the subroutines in Figure 16.24 and Figure 16.25 could experience problems with racing conditions. For example, if STA is active, and both B and C are true at the same time the main program would jump to subroutine 3 where STB would be turned on. then the main program would jump to subroutine 4 where STC would be turned on. For the output logic STB would never have been on. If this problem might occur, the state diagram can be modified to slow down these race conditions. Figure 16.26 shows a technique that blocks race conditions by blocking a transition out of a state until the transition into a state is finished. The solution may not always be appropriate.

plc advanced functions - 16.25

STA |

|

|

|

|

|

STC |

|

|

|

|

D*C |

||||

B*A |

|||||||

|

|

||||||

|

|

|

|

||||

|

|

|

|

|

C*(B + D) |

|

A*(B + D) |

||||||

|

||||||

|

|

|

|

|

STB |

|

first scan

Figure 16.26 A Modified State Diagram to Prevent Racing

Another solution is to force the transition to wait for one scan as shown in Figure 16.27 for state STA. A wait bit is used to indicate when a delay of at least one scan has occurred since the transition out of the state B became true. The wait bit is set by having the exit transition B true. The B3/0-STA will turn off the wait B3/10-wait when the transition to state B3/1-STB has occurred. If the wait was not turned off, it would still be on the next time we return to this state.

Program 3 for STA

B3/10 - wait

U B3/0 - STA

L B3/1 - STB

B B3/0 - STA

B3/10 - wait

Figure 16.27 Subroutines for State STA to Prevent Racing