Микроэлектроника.-1

.pdf

41

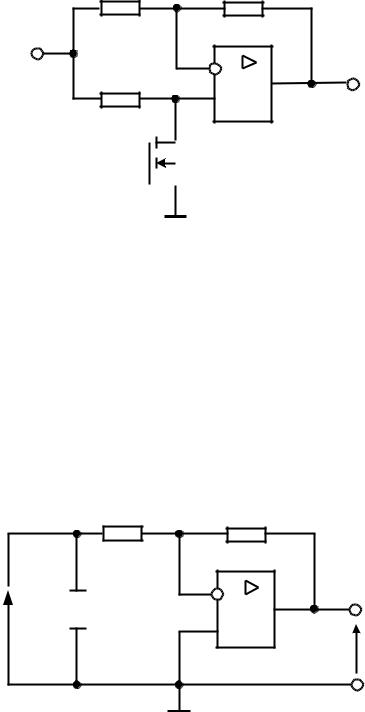

R1 |

R2 |

|

DA |

Uвх |

|

R3 |

Uвых |

|

VT

Uупр

Рис. 2.26 – Усилитель постоянного тока

Решение. Входящие в состав схемы операционный усилитель и поле-

вой транзистор будем считать идеальными. Сопротивление идеального поле-

вого транзистора во включенном состоянии равно нулю, а выключенном – бесконечности.

Для случая, соответствующего включенному состоянию транзистора,

справедлива схема замещения, приведенная на рис. 2.27.

R1 |

R2 |

|

DA |

Uвх

Uвх

R3

R3

Uвых

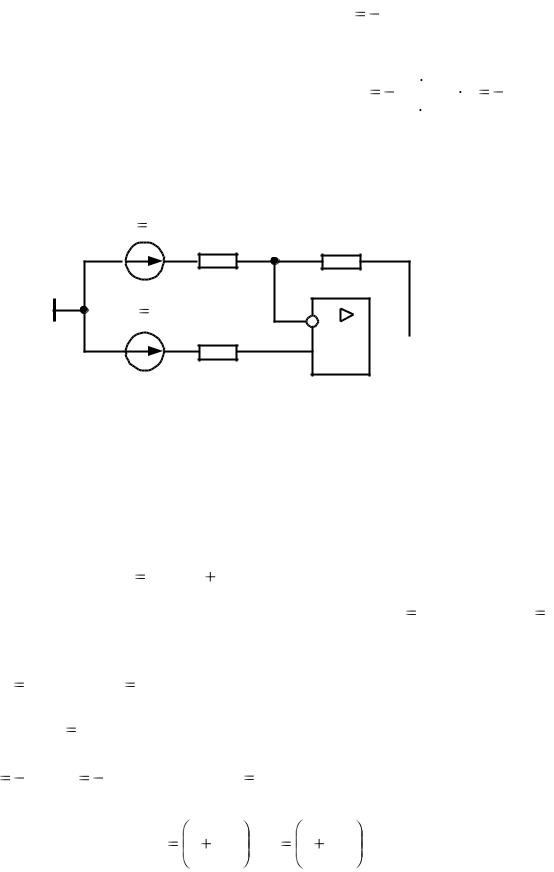

Рис. 2.27 – Эквивалентная схема усилителя постоянного тока Схема замещения соответствует инвертирующему УПТ на операцион-

ном усилителе. Резистор R3 оказывается включенным параллельно идеаль-

ному источнику ЭДС и не влияет на потенциал входного узла схемы. Выход-

42

ное напряжение определяется соотношением Uвых |

R2 |

Uвх . |

|

||

R1 |

|

||||

|

|

|

|||

Подставляя числовые значения, находим Uвых |

|

30 103 |

2 6 (В). |

||

10 103 |

|||||

|

|

||||

Для случая, соответствующего включенному состоянию транзистора,

справедлива схема замещения, представленная на рис. 2.28.

U1 Uвх R1

U2 Uвх

R3

R2

DA

Uвых

Uвых

Рис. 2.28 – Схема замещения усилителя постоянного тока

Если операционный усилитель охвачен цепью отрицательной обратной связи и выходное напряжение не превышает напряжения насыщения, то опе-

рационный усилитель работает в линейном режиме. В этом случае к расчету схемы применим принцип суперпозиции, а выходное напряжение определя-

ется выражением Uвых |

|

Uвых.1 Uвых.2 , где Uвых.1 – составляющая выход- |

||||||||||||

ного напряжения, обусловленная действием |

ЭДС U1 Uвх при |

U2 0 ; |

||||||||||||

Uвых.2 – составляющая выходного напряжения, обусловленная действием |

||||||||||||||

ЭДС U2 |

Uвх при U1 |

0 . |

|

|

|

|

|

|

|

|||||

|

При |

U2 |

0 схема |

эквивалентна |

инвертирующему УПТ, |

поэтому |

||||||||

U |

вых.1 |

R2 |

U |

|

R2 |

U |

вх |

. При U |

0 |

схема эквивалентна неинвертирую- |

||||

|

|

|||||||||||||

|

1 |

|

R1 |

|

|

1 |

|

|

|

|

|

|||

|

|

R1 |

|

|

|

|

|

|

|

|

|

|

||

щему УПТ, поэтому Uвых.2 |

1 |

R2 |

U2 |

1 |

R2 |

Uвх . |

|

|||||||

R1 |

R1 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

43

В итоге получаем выражение выходного напряжения в виде

Uвых |

1 |

R2 |

Uвх |

R2 |

Uвх |

Uвх . |

|

R1 |

R1 |

||||||

|

|

|

|

|

|||

Подставляя числовые данные, находим Uвых |

2 В. |

||||||

2.3 Методические указания к практическим занятиям

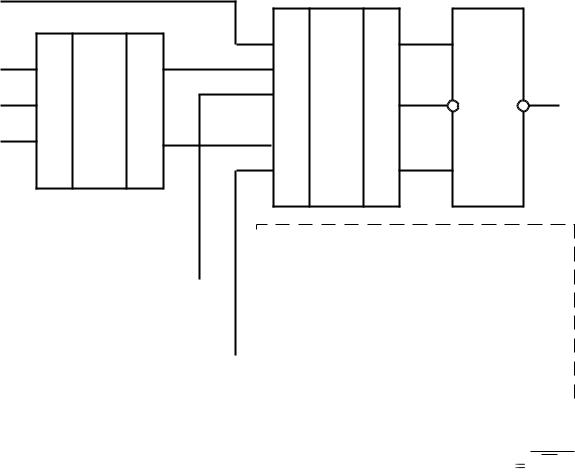

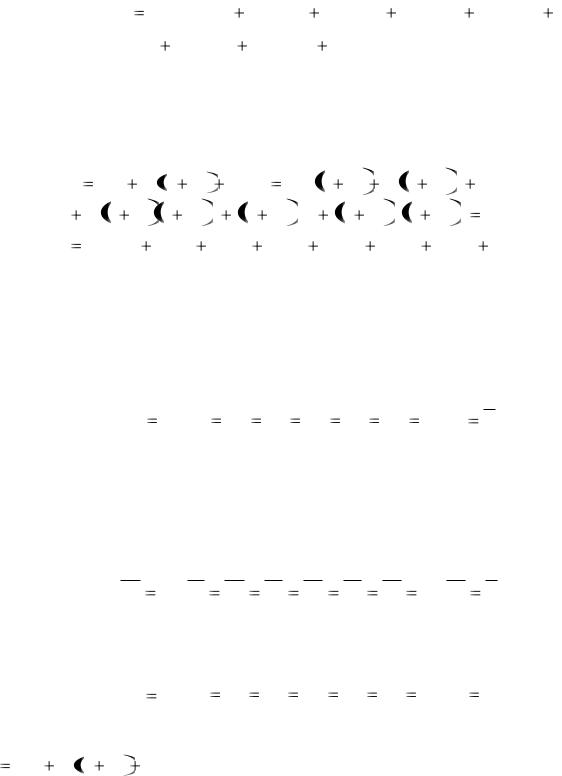

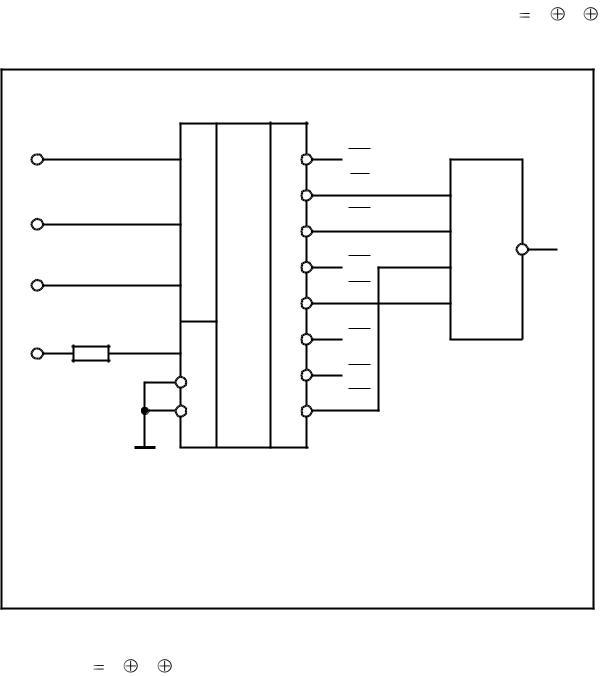

Проектирование устройства, зажигающего светодиод, если пять

из семи входных двоичных сигналов принимают единичное значение.

Для определения числа входных двоичных сигналов, принимающих единичное значение, необходимо просуммировать все входные сигналы с одинаковым (единичным) весом. Для суммирования семи входных сигналов можно использовать два полных одноразрядных и один двухразрядный дво-

ичные сумматоры (рис. 6.4).

Для включения светодиода при пяти единичных входных сигналов необходимо использовать комбинационную логическую схему, формирую-

щую уровень логического нуля только при наличии на выходе сумматора двоичного кода числа 5=101В. Такая комбинационная схема должна реализо-

вать булеву функцию f ps1s0 (рис. 2.29).

44

x0 |

|

|

|

|

|

|

|

|

|

p |

SM |

s0 |

& |

|

SM |

|

0 |

|

1 |

|

|

|

a0 |

|

|

||

x1 |

|

1 |

1 |

|

|

|

|

b0 |

|

|

|||

|

|

|

|

s1 |

f |

|

x2 |

1 |

|

|

|

||

|

|

|

2 |

|

||

x3 |

|

2 |

a1 |

|

|

|

|

b1 |

2 |

p |

|

||

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

реализация двухразрядного сумматора |

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||

|

|

|

SM |

|

|

||||||||||||||||||||||||||||||||||||||

x4 |

|

|

1 |

|

|

|

|

|

на полных одноразрядных сумматорах |

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

p0 |

|

|

|

|

|

|

|

|

|

s0 |

a1 |

|

|

|

|

|

|

|

|

|

|

|

s1 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

SM |

1 |

|

|

|

SM |

1 |

|

|

|

|||||||||||||||||||||||

x5 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

a0 |

1 |

|

|

|

|

|

|

|

|

|

|

b1 |

1 |

|

|

|

|

|

|

p |

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

x6 |

|

|

|

2 |

|

|

|

|

b0 |

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 2.29 – Комбинационная схема, реализующая булеву функцию f ps1s0

Принципиальную схему проектируемого устройства реализуем на ин-

тегральных микросхемах ТТЛШ серии К555. В состав серии К555 входит микросхема К555ИМ5, содержащая в одном корпусе два одноразрядных полных двоичных сумматора. С целью сокращения номенклатуры использу-

емых микросхем двухразрядный сумматор выполним на двух одноразрядных полных сумматорах.

Для реализации логической части устройства необходимы инвертор и логический элемент 3И-НЕ. Подключение светодиода предполагает приме-

нение микросхемы с открытым коллекторным выходом. С целью сокращения номенклатуры микросхем логическую часть можно построить на микросхеме К555ЛА10, содержащей 3 логических элемента 3И-НЕ с открытым коллекто-

ром. Схема электрическая принципиальная представлена на рис. 2.30.

45

x0

x1 x 2

x3

x4

x5

x6

1

3

4

13

12

11

|

DD1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

SM |

|

|

6 |

|

|

1 |

|

S |

|

|

|

|||

|

|

|

|

|

3 |

||

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pn |

|

5 |

|

|

4 |

|

|

|

|

|

|

|||

Pn |

|

|

|

|

|||

|

1 |

|

|

|

|

||

|

|

|

|

|

|

|

|

A |

SM |

|

|

8 |

|

13 |

|

|

S |

|

|

||||

|

|

|

|

12 |

|||

B |

|

|

|

|

|

||

|

Pn |

|

10 |

|

11 |

||

|

|

|

|

||||

Pn |

|

|

|

||||

|

1 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD2 |

|

|

|

|

A |

SM |

6 |

|

|

|

S |

|

|

|||

|

|

|

|||

B |

|

|

|

|

|

Pn |

Pn |

5 |

|

DD3.1 |

|

1 |

|

& |

|||

|

|

|

1 |

||

|

|

|

|

||

A |

SM |

8 |

2 |

12 |

|

S |

|||||

|

|

|

|||

B |

|

|

13 |

|

|

|

|

|

|

||

Pn |

Pn |

10 |

|

|

|

1 |

|

|

+5В

R1

1к |

R2

330

|

DD3.2 |

|

VD |

3 |

& |

|

4 6

5

DD1, DD 2 - К555ИМ5 DD3 - К555ЛА10

Выводы 7 микросхем подключить к общей шине

Выводы 14 микросхем подключить к +5 В

Рис. 2.30 – Схема электрическая принципиальная, реализующая булевой функции f ps1s0

46

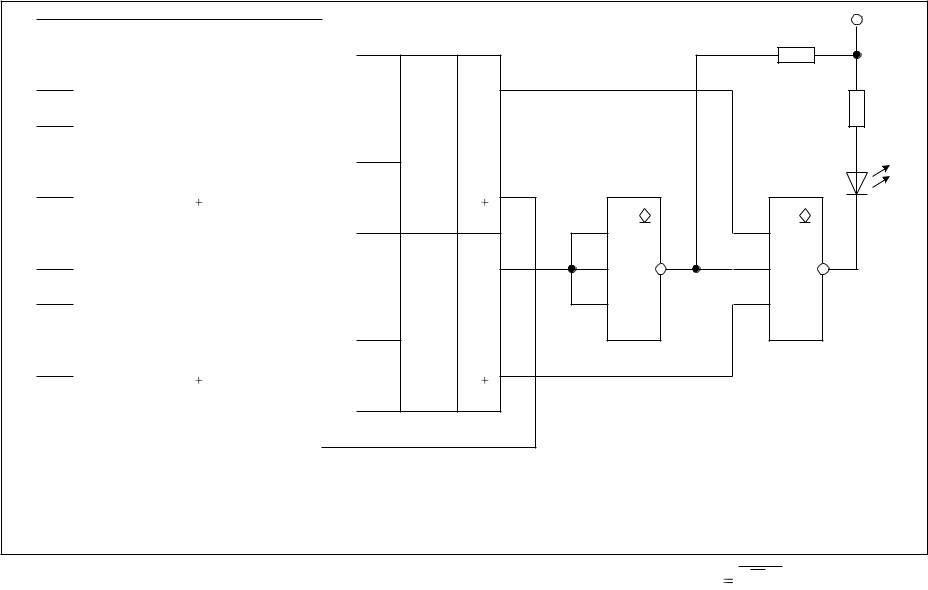

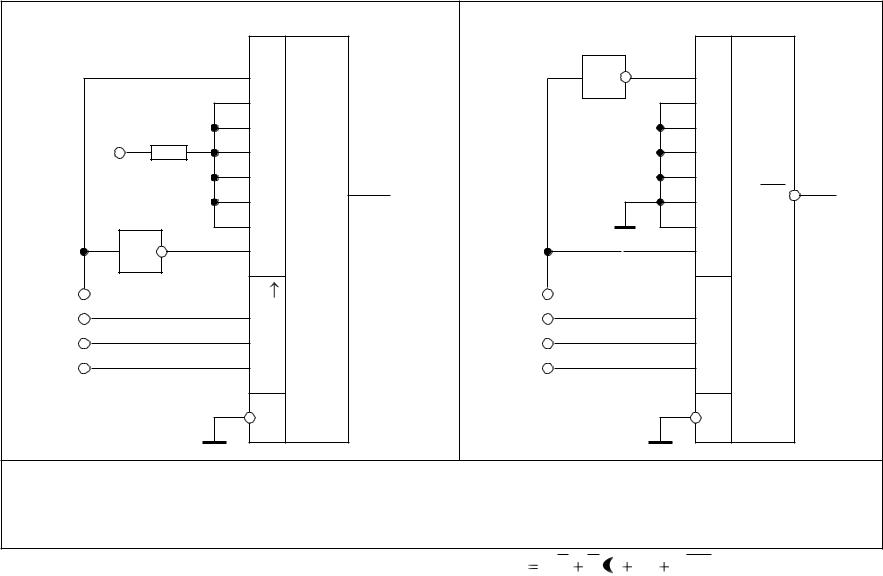

Проектирование комбинационной схемы, реализующей булеву функцию f AB A C D BCD с использованием мультиплексора.

BCD с использованием мультиплексора.

Любую логическую функцию четырех переменных можно реализо-

вать на восьмиканальном мультиплексоре (рис. 2.31). Выберем восьмика-

нальный мультиплексор К555КП7. Мультиплексор К555КП7 имеет ин-

версный вход разрешения, прямой и инверсный выходы. Сигналы А, В, С

будем подавать на адресные входы мультиплексора, а сигнал D будем ис-

пользовать как настроечный.

|

|

|

x0 |

|

0 |

|

MS |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|||

|

|

|

|

|

|

|||

|

|

|

x1 |

|

1 |

|

|

|

информационные |

|

|

|

|

|

|||

|

|

|

|

|

||||

|

x2 |

|

2 |

|

|

|

||

|

входы |

|

|

|

|

|

||

|

|

x3 |

|

3 |

|

|

|

|

|

|

|

|

|||||

|

|

|

x4 |

|

4 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

x5 |

|

5 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

x6 |

|

6 |

|

|

|

|

|

|

|

|

|

|

||

|

адресные |

|

x7 |

|

7 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

||||

|

|

C |

|

1 |

|

|

|

|

|

входы |

|

|

|

|

|

||

|

|

|

|

|

|

|||

|

|

|

B |

|

2 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

||

|

|

|

A |

|

4 |

|

|

|

|

|

|

|

|

|

|

||

|

вход разрешения |

|

|

|

||||

|

E |

|

|

|

|

|

||

|

|

E |

|

|

|

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

fMS ,пр.

fMS ,инв.

Рис. 2.31 – Восьмиканальный мультиплексор

Выражение булевой функции, реализуемой мультиплексором на прямом выходе, имеет вид:

fMS,пр E( ABCx0 ABCx1 ABCx2 ABCx3 ABCx4

ABCx5 ABCx6 ABCx 7 ) .

Выражение булевой функции, реализуемой мультиплексором на ин-

версном выходе, имеет вид:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

fMS,инв E( ABC x0 |

ABC x1 |

ABC x2 ABC x3 ABC x4 |

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

ABC x5 |

ABC x6 |

ABC x7 ) . |

||||||||||||||||||||||||||||||||||||

Используя законы булевой алгебры, преобразуем выражение задан-

ной булевой функции:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f AB |

A C D |

|

BCD |

|

|

|

AB C C |

|

|

A B |

B C |

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

A B B C C D A A BC A A B C C D |

|||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

ABCD |

|

|

ABC |

ABC |

ABC ABC |

ABC |

ABC ABCD . |

||||||||||||||||||||||||||||||||||

Сравнивая преобразованное выражение заданной функции с выра-

жением fMS.пр , определяем, что для реализации булевой функции на пря-

мом выходе мультиплексора необходимо на его информационные входы подать сигналы:

x0 D , x1 x2 x3 x4 x5 x6 1, x7 D .

Сравнивая преобразованное выражение заданной функции с выра-

жением fMS.инв , определяем, что для реализации булевой функции на ин-

версном выходе мультиплексора необходимо на его информационные вхо-

ды подать сигналы, удовлетворяющие условиям:

x0 D , x1 x2 x3 x4 x5 x6 1, x7 D .

Прямые значения этих сигналов получим, применяя логическую операцию “инверсия”:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x0 |

|

|

D , x1 |

x2 |

x3 x4 x5 |

x6 |

0 , x7 D . |

|

|||

|

Комбинационная |

схема, |

реализующая |

булеву |

функцию |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

f AB A C D |

BCD |

с |

использованием |

мультиплексора |

К555КП7, |

||||||||||

представлена на рис. 2.32.

48

|

|

|

|

DD2 |

|

|

|

|

|

|

|

DI |

MS |

|

|

DD1.1 |

|

|

|

4 |

|

|

1 |

4 |

||

|

|

|

0 |

|

|

|

|

|

|

|

3 |

|

|

|

|

3 |

|

|

|

1 |

|

|

|

|

||

|

|

2 |

|

|

|

|

2 |

|

+5 B |

1к |

2 |

|

|

|

|

||

1 |

|

|

|

|

1 |

|||

|

|

3 |

|

|

|

|

||

|

|

15 |

|

|

|

|

15 |

|

|

|

4 |

|

|

|

|

||

|

|

14 |

DO |

5 |

|

|

14 |

|

|

|

|

f |

|

||||

|

|

5 |

|

|

||||

|

|

|

|

|

|

|||

DD1.1 |

13 |

|

|

|

|

13 |

||

6 |

|

|

|

|

||||

|

|

12 |

|

|

|

|

12 |

|

1 |

|

7 |

|

|

|

|

||

|

|

|

|

|

|

|

||

D |

11 |

A |

D |

11 |

|

C |

0 |

C |

|||

10 |

10 |

||||

B |

1 |

B |

|||

9 |

9 |

||||

A |

2 |

A |

|||

|

|

||||

|

7 |

E |

|

7 |

|

|

|

|

|

DD2

DI MS

0

1

2

3

4 |

DO |

6 |

|

5 |

f |

||

|

|||

|

|

6

7

A

0

1

2

E

DD 1 - К555ЛН1 DD 2 - К555КП7

Вывод 7 микросхемы DD1 и 8 микросхемы DD2 подключить к общей шине Выводы 14 микросхемы DD1 и 16 микросхемы DD2 подключить к +5 В

Рис. 2.32 – Комбинационная схема, реализующая булеву функцию f AB A C D BCD с использованием мультиплексора К555КП7

BCD с использованием мультиплексора К555КП7

49

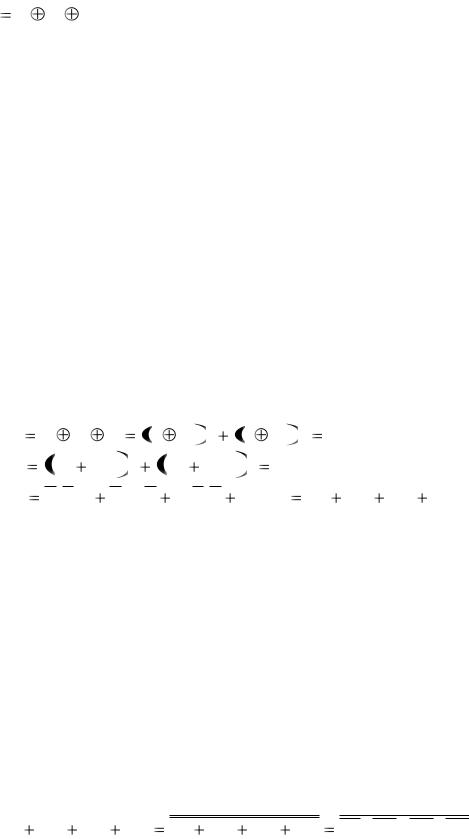

Проектирование комбинационной схемы, реализующей булеву

функцию f A B C с использованием дешифратора.

Любую булеву функцию трех переменных можно реализовать с ис-

пользованием полного дешифратора на три входа. Для этого переменные бу-

левой функции необходимо подать на информационные входы дешифратора.

Если выходы дешифратора являются прямыми, на них формируются все воз-

можные минтермы входных переменных. Если выходы дешифратора явля-

ются инверсными, на них формируются все возможные инверсии минтермов

(макстермы) входных переменных.

Наиболее удобной формой представления булевой функции для ее реа-

лизации с использованием дешифратора является выражение в совершенной дизъюнктивной нормальной форме.

Представим выражение заданной булевой функции в совершенной дизъюнктивной нормальной форме:

|

|

|

|

|

|

|

|

|

|

|

|

|

f A |

B C |

A B C A B C |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

AB |

|

AB C |

AB A B C |

|||||||||

A B C A B C A B C A B C m1 m2 m4 m7 .

Заданную булеву функцию реализуем с использованием дешифратора К555ИД7 (трехвходовой полный дещифратор с инверсными выходами, с од-

ним прямым и двумя инверсными входами разрешения, связанными логиче-

ской функцией “конъюнкция”).

Для реализации дизъюнкции минтермов заданной булевой функции необходимо сигналы с соответствующих выходов дешифратора подать на комбинационную логическую схему “4ИЛИ”. Так как выходы дешифратора К555ИД7 являются инверсными, комбинационную логическую схему синте-

зируем на основе соотношения:

m1 m2 m4 m7 m1 m2 m4 m7 m1  m2

m2  m4

m4  m7 .

m7 .

Соотношение показывает необходимость применения четырехвходово-

|

|

|

|

|

50 |

|

|

|

|

|

|

го логического элемента И-НЕ. Из состава микросхем серии К555 выберем |

|||||||||||

микросхему К555ЛА1 (два четырехвходовых логических элемента И-НЕ). |

|

||||||||||

Комбинационная схема, |

реализующая булеву функцию f |

A |

B |

C |

|||||||

с использованием дешифратора К555ИД7, представлена на рис. 2.33. |

|

|

|||||||||

|

|

|

DD1 |

|

|

|

|

|

|

|

|

|

|

1 |

DC |

15 |

m |

|

DD2.1 |

|

|

|

|

C |

|

1 |

0 |

|

|

|

|

|

|||

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

1 |

14 |

m1 |

1 |

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

2 |

2 |

|

13 |

m2 |

2 |

|

|

|

|

|

|

2 |

|

6 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

f |

|

|

|

|

|

|

3 |

12 |

m |

4 |

|

|

|

|

|

|

|

|

|

|

|

|

||||

A |

|

3 |

4 |

|

|

3 |

|

|

|

|

|

|

|

|

11 |

m4 |

5 |

|

|

|

|

||

|

|

|

|

4 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

+5 B |

1к |

6 |

&E |

5 |

10 |

m5 |

|

|

|

|

|

|

|

5 |

|

6 |

9 |

m6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

||

|

|

4 |

|

7 |

7 |

m7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DD 1 - К555ИД7 |

DD 2 - К555ЛА1 |

|

|

|

|

|

|||

Вывод 8 микросхемы DD1 и 7 микросхемы DD2 подключить к общей шине |

|

|

|||||||||

Выводы 16 микросхемы DD1 и 14 микросхемы DD2 подключить к +5 В |

|

|

|

||||||||

Рис. 2.33 – Комбинационная схема, реализующая булеву функцию f A B C с использованием дешифратора К555ИД7

Для разрешения работы дешифратора на его прямой вход разрешения следует подать напряжение уровня логической единицы, а на инверсные вхо-

ды разрешения – напряжения уровней логического нуля. С этой целью пря-

мой вход дешифратора подключен к источнику напряжения +5 В через рези-