Verilog_radar1

.pdf

while Loop

n while loop – выполняется если выражение истинно

initial begin

count = 0;

while (count < 101) begin $display (“Count = %d”, count); count = count + 1;

end end

Считает от 0 до 100 Выходит из цикла когда count=101

Данный пример не синтезируется!

for Loop

for loop -

выполняется один раз в начале цикла и затем выполняется если выражение истинно

4-bit Left Shifter

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

// declare the index for the FOR LOOP integer i;

always @(inp, cnt) begin result[7:4] = 0;

result[3:0] = inp; if (cnt == 1) begin

for (i = 4; i <= 7; i = i + 1) begin

result[i] = result[i-4]; end

result[3:0] = 0; end

end

Оптимизация использования операторов в Verilog описании

253 |

© 2014 СПбГПУ, каф. КСПТ, доц. Антонов А.П. ( dilab@scideco.ru ) |

Замена операторов арифметическими блоками

1 Comparator |

< |

|

Компилятор распознает |

2 Adders |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

операторы и заменяет их |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|||||

оптимизированными |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

блоками |

|

|

+ |

|

|

|

+ |

|||

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 Mulitplexer

254 |

© 2014 СПбГПУ, каф. КСПТ, доц. Антонов А.П. ( dilab@scideco.ru ) |

Оптимизация Verilog описания

n Симметрирование операторов n Конвейеризация

n Совместное использование ресурсов

255 |

© 2014 СПбГПУ, каф. КСПТ, доц. Антонов А.П. ( dilab@scideco.ru ) |

Симметрирование операторов

nИспользуйте скобки для группировки операторов

-Позволяет увеличить быстродействие

-Может уменьшить аппаратные затраты

-Симметричная задержка от всех входов до выхода

Не симметрированный |

Симметрированный |

z <= a * b * c * d |

z <= (a * b) * (c * d) |

a |

a |

|

X |

|

b |

X |

b |

|

||

c |

X z |

c |

d |

|

|

|

|

d |

X

X  z

z

X

256 |

© 2014 СПбГПУ, каф. КСПТ, доц. Антонов А.П. ( dilab@scideco.ru ) |

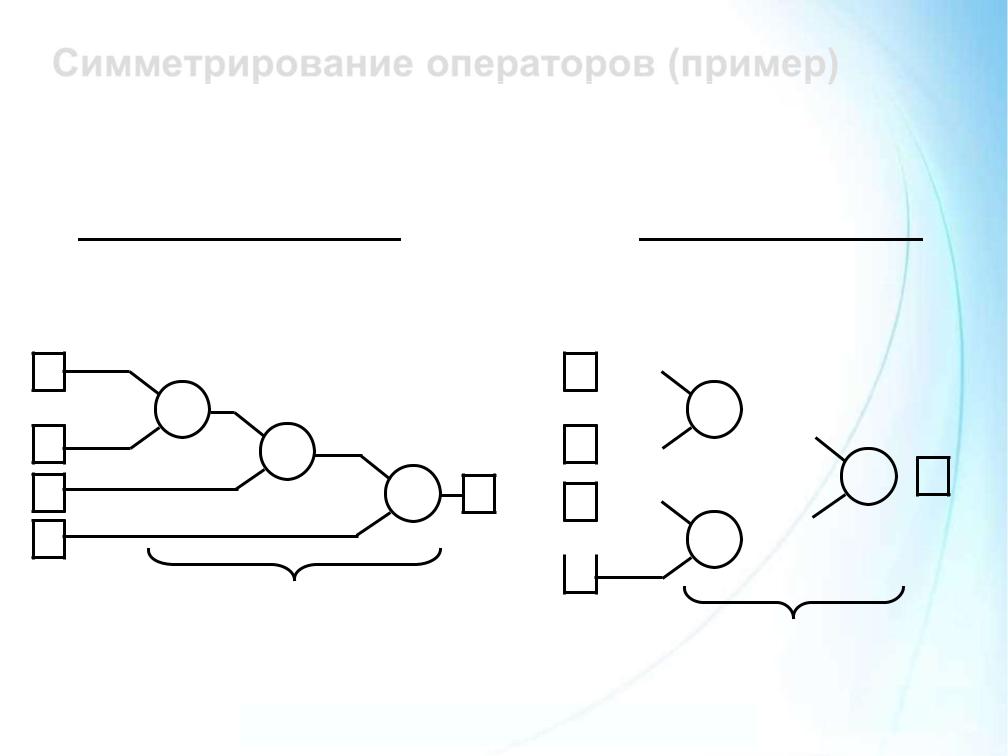

Симметрирование операторов (пример)

n a, b, c, d: 4-bit векторы

Не симметрированный

z <= a * b * c * d

a |

4 x 4 |

|

|

|

|

X |

8 x 4 |

|

|

b |

X |

12 x 4 |

||

|

||||

c |

|

X z |

||

|

|

|||

d |

|

|

16-bit |

Задержка – 3 умножителя

Симметрированный

z <= (a * b) * (c * d)

a |

|

|

|

4 x 4 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

b |

|

|

|

X |

|

|

8 x 8 |

||

|

|

|

|

|

|||||

|

|

|

4 x 4 |

|

|

X |

|

z |

|

|

|

|

|

|

|

||||

c |

|

|

|

|

|

|

|||

|

|

|

|

|

|

||||

|

|

|

|||||||

|

|

|

|

X |

|

|

|

16-bit |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d

Задержка – 2 умножителя

257 |

© 2014 СПбГПУ, каф. КСПТ, доц. Антонов А.П. ( dilab@scideco.ru ) |

Конвейеризация

nЦеленаправленное добавление триггеров в критическую цепь распространения комбинационных сигналов

n Увеличивает максимальную частоту работы

nДобавляет такт (такты) задержки

-Больше тактов требуется для получения результата на выходе

nНекоторые компиляторы могут осуществлять конвейеризацию автоматически

258 |

© 2014 СПбГПУ, каф. КСПТ, доц. Антонов А.П. ( dilab@scideco.ru ) |

Добавление уровня конвейеризации

|

25 MHz System |

|

Counter, |

Decode |

Logic |

State |

Value |

|

Machine |

x |

|

|

40 ns |

|

|

|

50 MHz System |

Counter, |

Decode |

Logic |

State |

Value |

|

Machine |

x-1 |

|

|

20 ns |

20 ns |

259 |

© 2014 СПбГПУ, каф. КСПТ, доц. Антонов А.П. ( dilab@scideco.ru ) |

|

Конвейеризация 4-х входового умножителя

a

X |

|

b |

|

X |

z |

c |

|

X

d

260 |

© 2014 СПбГПУ, каф. КСПТ, доц. Антонов А.П. ( dilab@scideco.ru ) |