Verilog_radar1

.pdf

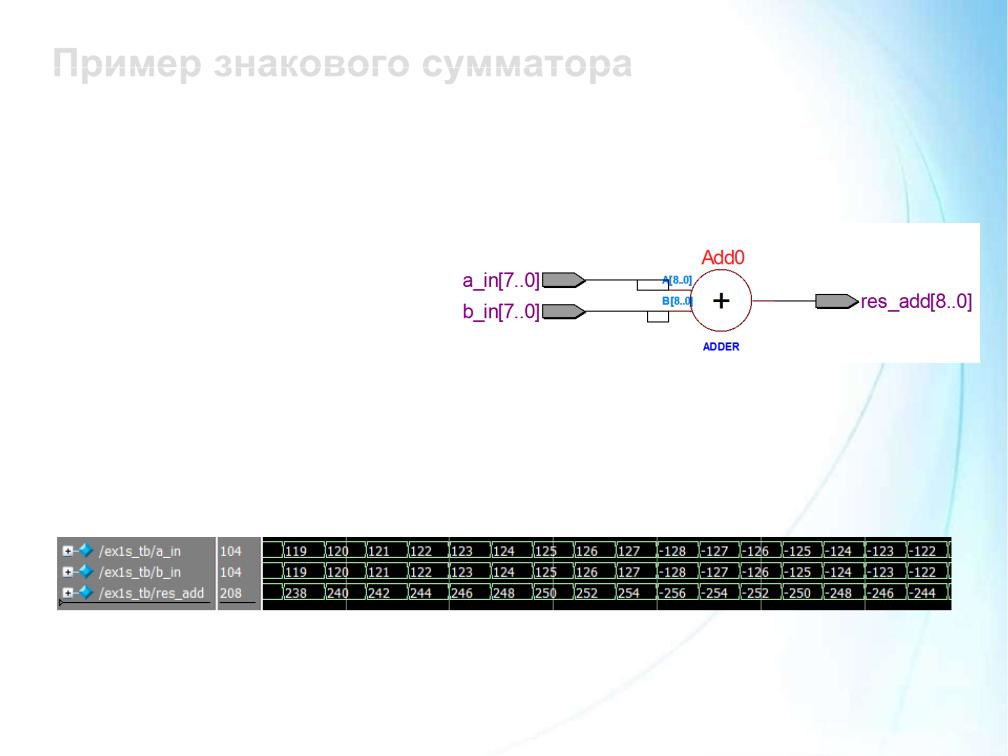

Пример знакового сумматора

module ex1s (a_in, b_in, res_add );

input signed [7:0] a_in, b_in; Output signed [8:0] res_add;

assign res_add = a_in + b_in;

endmodule

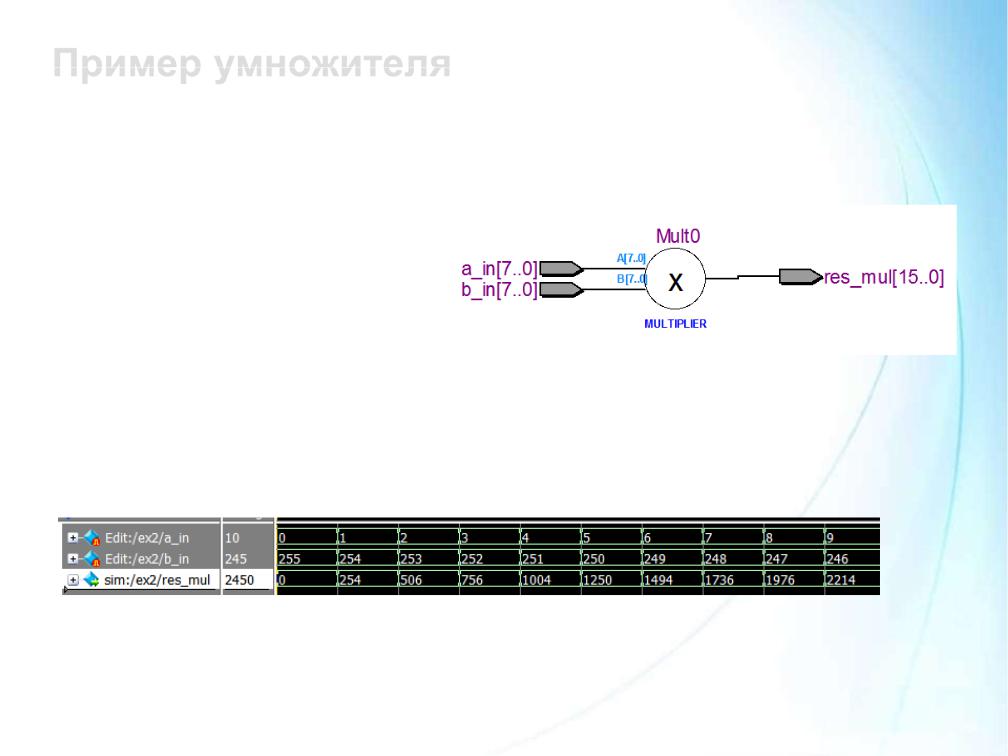

Пример умножителя

module ex2 (a_in, b_in, res_mul );

input [7:0] a_in, b_in; output [15:0] res_mul;

assign res_mul = a_in * b_in;

endmodule

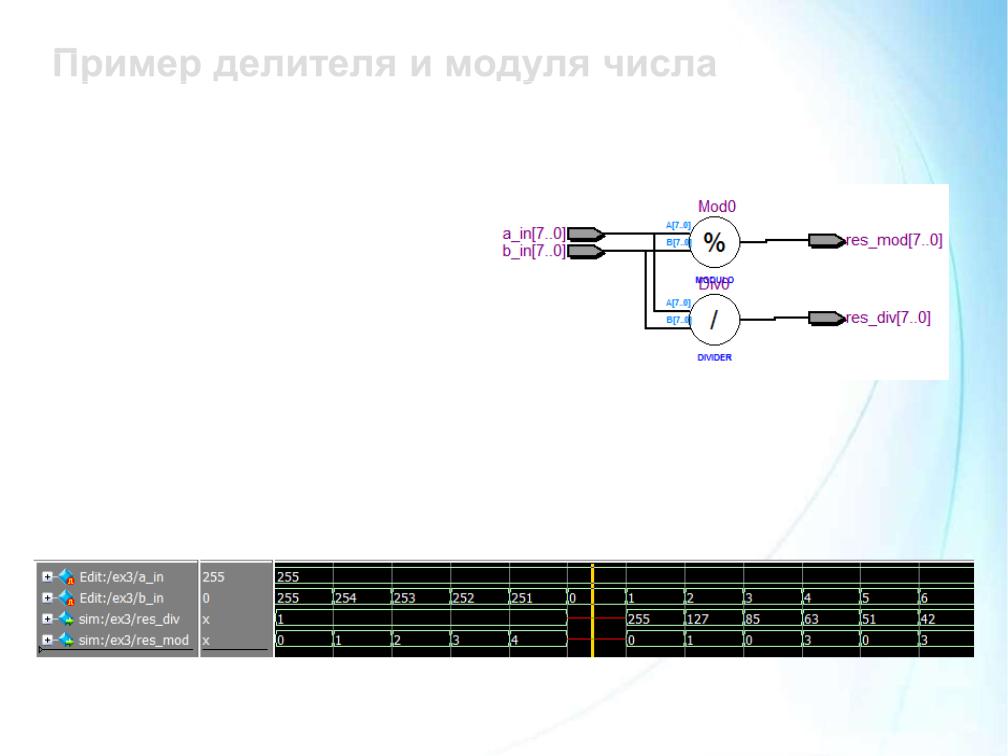

Пример делителя и модуля числа

module ex3 (a_in, b_in, res_div, res_mod );

input [7:0] a_in, b_in;

output [7:0] res_div, res_mod;

assign res_div = a_in / b_in; assign res_mod = a_in % b_in;

endmodule

Пример возведения в степень

module ex4 (a_in, res_exp);

input [7:0] a_in; output [31:0] res_exp;

assign res_exp = a_in ** 3;

endmodule

Приоритет операторов

|

Операторы |

Приоритет |

||

|

|

|

|

|

+ - ! ~ |

& |

~& |

etc. (unary* operators) |

Высокий |

|

|

|

|

|

|

|

|

** |

|

|

|

|

|

|

|

|

* |

/ % |

|

|

|

|

|

|

+ |

- |

(binary operators) |

|

|

<< >> <<< >>>

<> <= >=

== != === |

!== |

|

|

|

|

||

& (binary operator) |

|||

|

|

|

|

^ ~^ |

^~ (binary operators) |

||

|

|

|

|

| |

(binary operator) |

||

|

|

|

|

|

&& |

|

|

|

|

|

|

|

|| |

|

|

|

|

|

|

|

?: |

|

Низкий |

|

|

|

|

|

{ } { { } } |

|

|

|

|

|

|

n( ) используются для изменения порядка выполнения операторов

Упражнение 3

136 |

© 2014 СПбГПУ, каф. КСПТ, доц. Антонов А.П. ( dilab@scideco.ru ) |

Упражнение 3 (задание)

n На языке Verilog описать представленную ниже схему

pba |

|

|

|

|

|

|

mux |

||

sw[7..4] |

* |

|

||

m[7..0] |

||||

sw[3..0] |

|

|

|

led[7..0] |

|

|

|

|

|

sw[7..4] + s[7..0] sw[3..0]

n Осуществить функциональное моделирование

nПосмотреть синтезированную пакетом QII схему (RTL Viewer)

n Назначить выводы СБИС

nОсуществить полную компиляцию, программирование платы и проверить работу проекта на плате.

137 |

© 2014 СПбГПУ, каф. КСПТ, доц. Антонов А.П. ( dilab@scideco.ru ) |

Порядок выполнения упражнения 3

nСоздать проект:

-Имя проекта – lab3, имя модуля верхнего уровня иерархии – lab1, Рабочая папка - …\lab 3

-СБИС – EP4CE6E22C8

n Создать новый файл: File=>New=>Verilog HDL file n Сохранить его под именем lab3.

138 |

© 2014 СПбГПУ, каф. КСПТ, доц. Антонов А.П. ( dilab@scideco.ru ) |

Упражнение 3 (задание)

pba |

|

|

|

|

|

|

mux |

||

sw[7..4] |

* |

|

||

m[7..0] |

||||

sw[3..0] |

|

|

|

led[7..0] |

|

|

|

|

|

sw[7..4] + s[7..0] sw[3..0]

139 |

© 2014 СПбГПУ, каф. КСПТ, доц. Антонов А.П. ( dilab@scideco.ru ) |

Порядок выполнения упражнения 3

n Введите текстовое описание схемы на языке Verilog

pba |

|

|

|

|

|

|

mux |

||

sw[7..4] |

* |

|

||

m[7..0] |

||||

sw[3..0] |

|

|

|

led[7..0] |

|

|

|

|

|

sw[7..4] + s[7..0] sw[3..0]

140