5laba_otchet

.docxМИНИСТЕРСТВО ЦИФРОВОГО РАЗВИТИЯ,

СВЯЗИ И МАССОВЫХ КОММУНИКАЦИЙ РОССИЙСКОЙ ФЕДЕРАЦИИ

ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ

«САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ТЕЛЕКОММУНИКАЦИЙ ИМ. ПРОФ. М.А. БОНЧ-БРУЕВИЧА»

(СПБГУТ)

_________________________________________________________________________

Кафедра радиосистем и обработки сигналов (РОС)

Лабораторная работа №5

Исследование синхронной логики на языке описания Verilog

Выполнила

студентка группы РТ-01

Проверил: Чернов И.Н.

____________________

Цель работы

Закрепить знания по применению языка Verilog для описания синхронной логики (D-триггеры, регистры, счетчики).

1. Исследование D-триггера

Модуль

module lab5_flip_flop

(

input d, clk,

output reg q

);

always @( posedge clk )

q <= d ;

endmodule

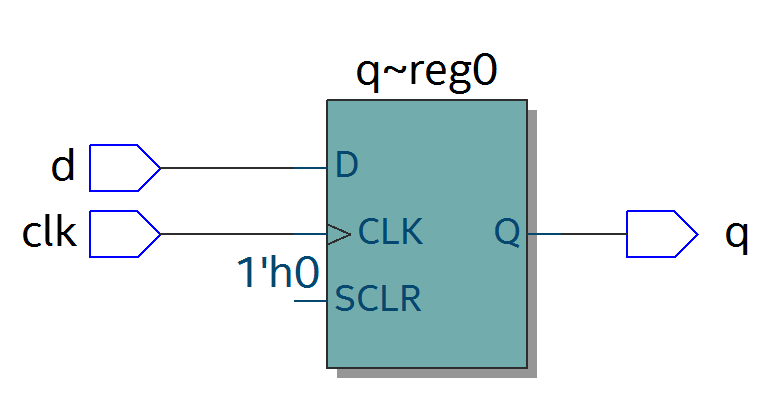

RTL

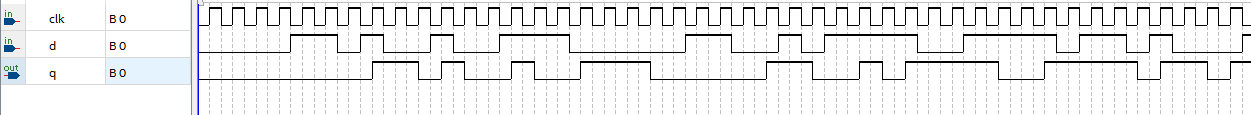

Testbench

Сигнал управления синхронной логикой (D-триггером)

Модуль

module lab5_flip_flop_2

(

input d, clk, sclr,

output reg q

);

always @( posedge clk )

begin

if (sclr)

q <= 1'b0;

else

q <= d;

end

endmodule

RTL

Testbench

2. Исследование регистра

а) регистр памяти (параллельный регистр)

Модуль

module lab5_reg

(

input [7:0]d,

input ena, aclr, clk,

output reg [7:0]q

);

always @( posedge clk or negedge aclr )

begin

if (aclr == 0) q = 0;

else if (ena)

q <= d;

end

endmodule

RTL

Testbench

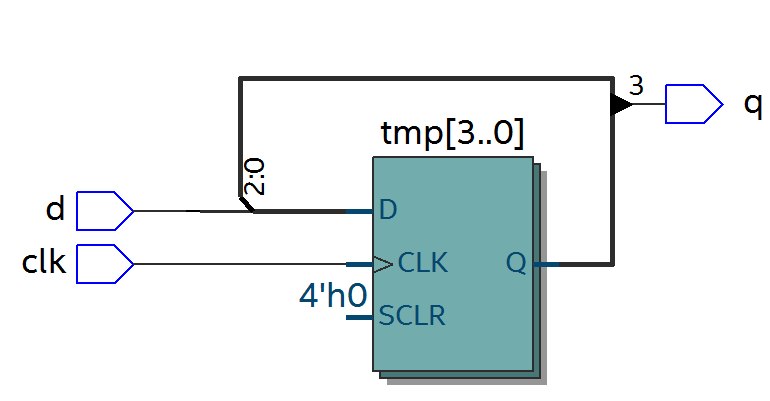

б) регистр сдвига

Модуль

module lab5_shift_reg

(

input d,

input clk,

output q

);

reg [3:0]tmp;

always @( posedge clk )

tmp = { tmp[2:0], d };

assign q = tmp[3];

endmodule

RTL

Testbench

3. Двоично-десятичный счётчик (0 ÷ 9)

Модуль

module lab5_counter

(

input clk, aclr, ena,

output reg [3:0]q

);

always @( posedge clk, negedge aclr )

begin

if(aclr == 0) q = 0;

else if(ena)

begin

if(q == 4'h9) q = 4'h0;

else q = q + 4'h1;

end

end

endmodule

RTL

Testbench

Вывод

В ходе работы была изучена работа D-триггеров: асинхронного и синхронного. Также выполнены схемы регистра памяти и сдвигового регистра. Выполнена схема двоично-десятичного счётчика.