3laba_otchet

.docxМИНИСТЕРСТВО ЦИФРОВОГО РАЗВИТИЯ,

СВЯЗИ И МАССОВЫХ КОММУНИКАЦИЙ РОССИЙСКОЙ ФЕДЕРАЦИИ

ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ

«САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ТЕЛЕКОММУНИКАЦИЙ ИМ. ПРОФ. М.А. БОНЧ-БРУЕВИЧА»

(СПБГУТ)

_________________________________________________________________________

Кафедра радиосистем и обработки сигналов (РОС)

Лабораторная работа №3

АСИНХРОННЫЕ И СИНХРОННЫЕ RS-TPИГГЕРЫ

Выполнила

студентка группы РТ-01

Проверил: Чернов И.Н.

____________________

Цель работы

Изучение правил функционирования асинхронного и синхронного RS-триггеров.

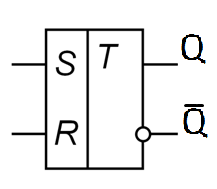

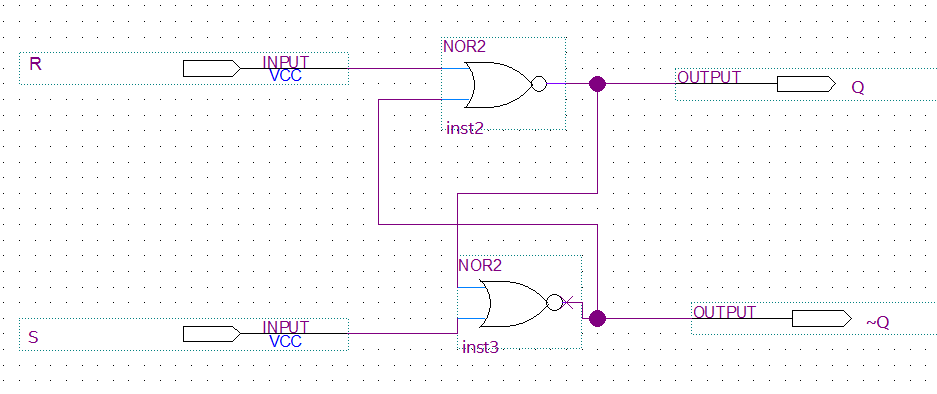

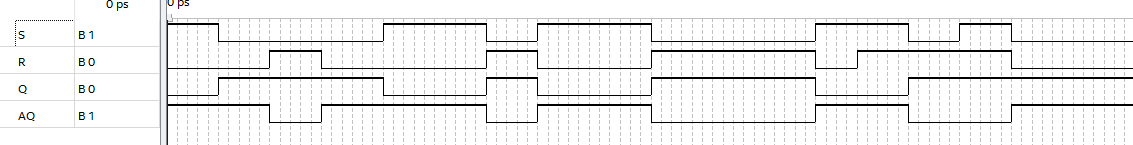

2.2.1. Исследование асинхронного RS-триггера с прямыми входами

Схема триггера

Симуляция

Таблица переключений

Номер набора |

|

|

|

|

|

Состояние триггера |

0 |

1 |

0 |

z |

1 |

0 |

set |

1 |

0 |

0 |

1 |

1 |

0 |

storage |

2 |

0 |

1 |

1 |

0 |

1 |

reset |

3 |

0 |

0 |

0 |

0 |

1 |

storage |

4 |

1 |

0 |

0 |

1 |

0 |

set |

5 |

1 |

0 |

1 |

1 |

0 |

set |

6 |

0 |

1 |

1 |

0 |

1 |

reset |

7 |

1 |

0 |

0 |

1 |

0 |

set |

8 |

1 |

0 |

1 |

1 |

0 |

set |

9 |

0 |

1 |

1 |

0 |

1 |

reset |

10 |

0 |

1 |

0 |

0 |

1 |

reset |

11 |

0 |

1 |

0 |

0 |

1 |

reset |

12 |

1 |

0 |

0 |

1 |

0 |

set |

13 |

1 |

1 |

1 |

x(0) |

x(0) |

illegal |

14 |

0 |

1 |

x(0) |

0 |

1 |

reset |

15 |

1 |

1 |

0 |

x(0) |

x(0) |

illegal |

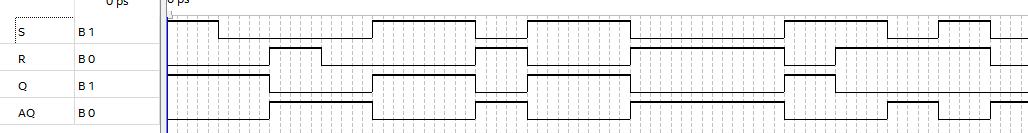

2.2.2. Исследование асинхронного RS-триггера с инверсными входами

Схема

Симуляция

Таблица переключений

Номер набора |

|

|

|

|

|

Состояние триггера |

0 |

1 |

0 |

z |

0 |

1 |

set |

1 |

0 |

0 |

0 |

x(1) |

x(1) |

illegal |

2 |

0 |

1 |

x(1) |

1 |

0 |

reset |

3 |

0 |

0 |

1 |

x(1) |

x(1) |

illegal |

4 |

1 |

0 |

x(1) |

0 |

1 |

set |

5 |

1 |

0 |

0 |

0 |

1 |

set |

6 |

0 |

1 |

0 |

1 |

0 |

reset |

7 |

1 |

0 |

1 |

0 |

1 |

set |

8 |

1 |

0 |

0 |

0 |

1 |

set |

9 |

0 |

1 |

0 |

1 |

0 |

reset |

10 |

0 |

1 |

1 |

1 |

0 |

reset |

11 |

0 |

1 |

1 |

1 |

0 |

reset |

12 |

1 |

0 |

1 |

0 |

1 |

set |

13 |

1 |

1 |

0 |

0 |

1 |

storage |

14 |

0 |

1 |

0 |

1 |

0 |

reset |

15 |

1 |

1 |

1 |

1 |

0 |

storage |

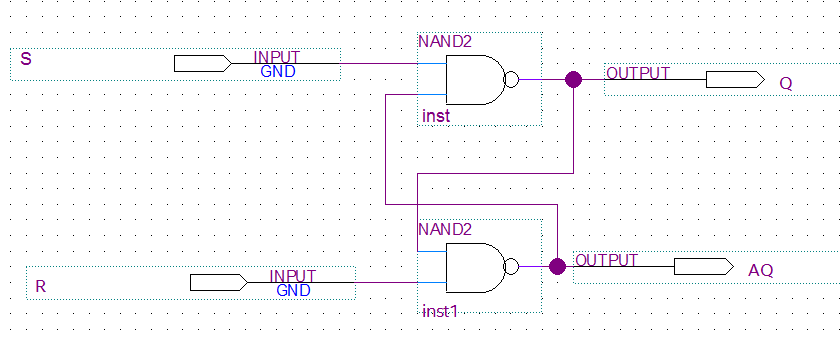

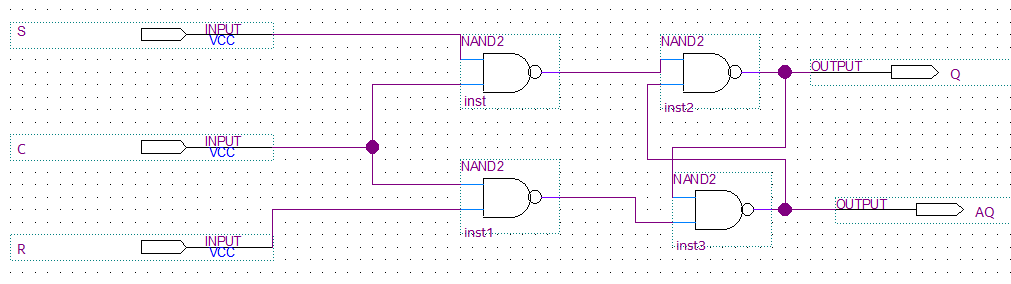

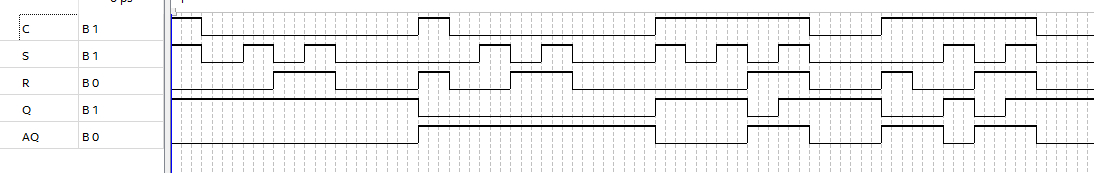

2.2.3. Исследование синхронного RS-триггера с прямыми входами

Схема

Симуляция

Таблица переключений

Номер набора |

|

|

C |

|

|

|

Состояние триггера |

0 |

1 |

0 |

1 |

z |

1 |

0 |

set |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

storage |

2 |

1 |

0 |

0 |

1 |

1 |

0 |

storage |

3 |

0 |

1 |

0 |

1 |

1 |

0 |

storage |

4 |

1 |

1 |

0 |

1 |

1 |

0 |

storage |

5 |

0 |

0 |

0 |

1 |

1 |

0 |

storage |

6 |

0 |

0 |

0 |

1 |

1 |

0 |

storage |

7 |

0 |

0 |

0 |

1 |

1 |

0 |

storage |

8 |

0 |

1 |

1 |

1 |

0 |

1 |

reset |

9 |

0 |

0 |

0 |

0 |

0 |

1 |

storage |

10 |

1 |

0 |

0 |

0 |

0 |

1 |

storage |

11 |

0 |

1 |

0 |

0 |

0 |

1 |

storage |

12 |

1 |

1 |

0 |

0 |

0 |

1 |

storage |

13 |

0 |

0 |

0 |

0 |

0 |

1 |

storage |

14 |

0 |

0 |

0 |

0 |

0 |

1 |

storage |

15 |

0 |

0 |

0 |

0 |

0 |

1 |

storage |

16 |

1 |

0 |

1 |

0 |

1 |

0 |

set |

17 |

0 |

0 |

1 |

1 |

1 |

0 |

storage |

18 |

1 |

0 |

1 |

1 |

1 |

0 |

set |

19 |

0 |

1 |

1 |

1 |

0 |

1 |

reset |

20 |

1 |

1 |

1 |

0 |

x(1) |

x(1) |

illegal |

21 |

0 |

0 |

0 |

x(1) |

x(1) |

x(0) |

illegal |

22 |

0 |

0 |

0 |

x(1) |

x(1) |

x(0) |

illegal |

23 |

0 |

1 |

1 |

x(1) |

0 |

1 |

reset |

24 |

0 |

0 |

1 |

0 |

0 |

1 |

storage |

25 |

1 |

0 |

1 |

0 |

1 |

0 |

set |

26 |

0 |

1 |

1 |

1 |

0 |

1 |

reset |

27 |

1 |

1 |

1 |

0 |

x(1) |

x(1) |

illegal |

Вывод:

RS-триггеры с прямыми входами имеют запрещённое состояние при включении S = 1, R = 1. Комбинационная логика построена на элементах NOR, а ключи замыкаются на логическую единицу, значит при S = 1, R = 1 на выходе такого триггера Q = 0, ~Q = 0, т.к. NOR выдаёт 0, когда есть хотя бы одна единица на входе. Когда на входе 1 и 0, соответственно S и R, то триггер выдаёт Q = 1 (~Q = 0) и наоборот 0 и 1 -> Q = 0 (~Q = 1). Состояние хранения S = 0, R = 0 зависит от предыдущего состояния триггера. Если на вход NOR подать S = 0 и ~Q = 0, то будет Q = 1, если S = 0 и ~Q = 1, то Q = 0, аналогично с ключом R.

RS-триггеры с инверсными входами отличаются тем, что ключи S и R замыкаются на логический ноль и построены на элементах NAND. Их запрещённое состояние S = 0, R = 0, т.к. NAND выдаёт 1, если хотя бы один вход 0. Set (S = 1, R = 0) -> Q = 0, ~Q = 1, storage (S = 1, R = 1).

На синхронный RS-триггер подаётся три входа: R, S и CLK. Он состоит из четырёх логических элементов NAND. Суть этого триггера заключается в том, что тактовый сигнал разрешает считывать R и S сигналы. При CLK = 1, триггер работает так же как обычный RS-триггер, но при CLK = 0, триггер перестаёт считывать какие либо изменения на входах и переходит в режим хранени.