4laba_otchet

.docxМИНИСТЕРСТВО ЦИФРОВОГО РАЗВИТИЯ,

СВЯЗИ И МАССОВЫХ КОММУНИКАЦИЙ РОССИЙСКОЙ ФЕДЕРАЦИИ

ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ

«САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ТЕЛЕКОММУНИКАЦИЙ ИМ. ПРОФ. М.А. БОНЧ-БРУЕВИЧА»

(СПБГУТ)

_________________________________________________________________________

Кафедра радиосистем и обработки сигналов (РОС)

Лабораторная работа №4

Разработка мультиплексоров и сумматоров на ПЛИС

Выполнила

студентка группы РТ-01

Проверил: Чернов И.Н.

____________________

1. Разработка мультиплексоров на ПЛИС

1.1 Описание схемы мультиплексора на языке Verilog

Модуль:

module lab_4

(

input A0, A1, D0, D1, D2, D3,

output Y

);

wire S1, S2, S3, S4, S5, S6;

NOT my_1_not ( .out(S1), .in(A0));

NOT my_2_not ( .out(S2), .in(A1));

AND3 my_1_and ( .out(S3), .in_0(S1), .in_1(S2), .in_2(D0));

AND2 my_2_and ( .out(S4), .in_0(A0), .in_1(D1));

AND3 my_3_and ( .out(S5), .in_0(S1), .in_1(A1), .in_2(D2));

AND3 my_4_and ( .out(S6), .in_0(A0), .in_1(A1), .in_2(D3));

OR4 my_or ( .out(Y), .in_0(S3), .in_1(S4), .in_2(S5), .in_3(S6));

endmodule

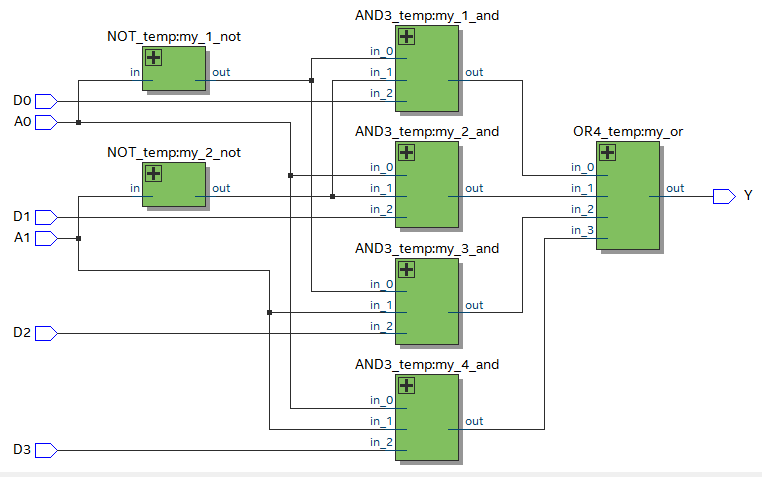

RTL

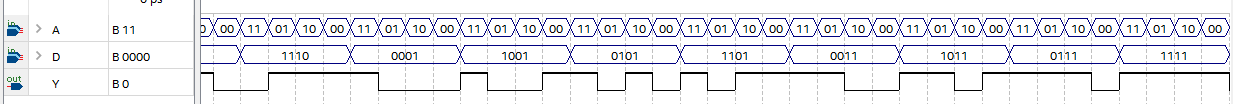

Testbench

2. Разработка модулей высокого уровня на ПЛИС на примере одно и 4-х битного сумматоров.

Однобитный сумматор

module sum

(

input a, b,

input c_in,

output sum,

output c_out

);

wire s1, s2, s3;

XOR my_xor_1(.IN1(a), .IN2(b), .OUT(s1));

AND2 my_and_1(.IN1(a), .IN2(b), .OUT(s2));

and2 my_and_2(.IN1(s1), .IN2(c_in), .OUT(s3));

XOR my_xor_2(.IN1(s1), .IN2(c_in), .OUT(sum));

OR2 my_xor_3(.IN1(s3), .IN2(s2), .OUT(c_out));

endmodule

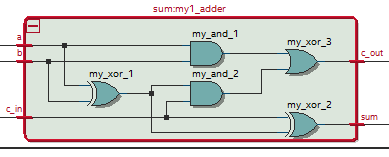

RTL

Четырёх-битный сумматор

module lab_4_2

(

output [3:0]sum,

output c_out,

input [3:0]l_a,

input [3:0]h_a,

input c_in,

input c

);

wire c0, c1, c2;

adder_my my1_adder( .sum(sum[0]), .c_out(c0), .a_0(l_a[0]), .a_1(h_a[0]), .c_in(c) );

adder_my my2_adder( .sum(sum[1]), .c_out(c1), .a_0(l_a[1]), .a_1(h_a[1]), .c_in(c0) );

adder_my my3_adder( .sum(sum[2]), .c_out(c2), .a_0(l_a[2]), .a_1(h_a[2]), .c_in(c1) );

adder_my my4_adder( .sum(sum[3]), .c_out(c_out), .a_0(l_a[3]), .a_1(h_a[3]), .c_in(c2) );

endmodule

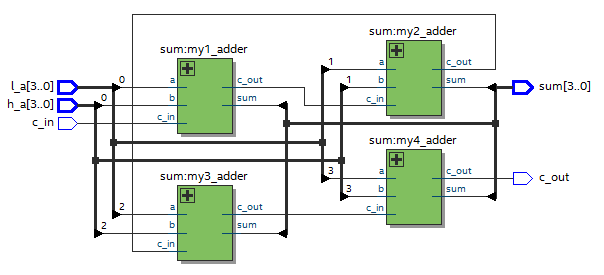

RTL

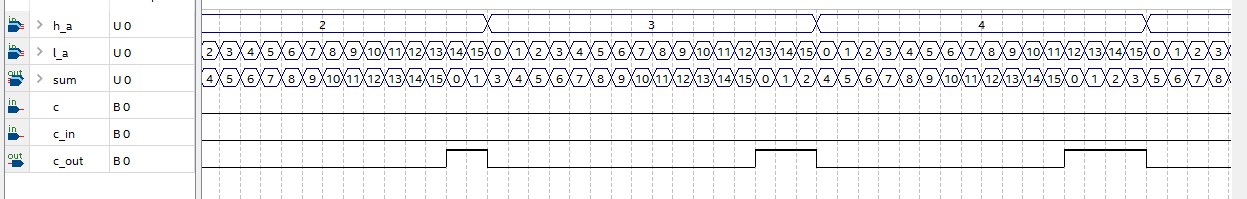

Testbench

Вывод:

В ходе лабораторной работы был изучен принцип работы мультиплексора.

Также описаны схемы однобитного и четырёхбитного сумматоров. Сделаны временные диаграммы, подтверждающие правильность выполнения.