Самосадный Автоматизированное проектирование устройств систем сбора-обработки Ч2 2015

.pdf

Time step=844.9E-21, minimum allowable step size =1.000E-18

Указываются проблемы с расчетами матрицы:

ERROR -- The circuit matrix is too close to being singular to solve. The diagonal entry for device V_V1 is -2.59E-18 which is too close to 0.

Указываются возможные причины возникновения проблем, связанные с высоким значением коэффициента усиления или чрезвычайно высоким сопротивлением узла схемы в начальный момент времени.

There are two main causes of a singular matrix:

1)A path ending at device V_V1 has a large gain, of the order of -3.87E+17.

Or,

2)device V_V1 has a very high impedance to ground, of the order of -3.87E+17

ohms. |

The readin does a topology check for nodes that float, but it cannot |

catch |

nodes which almost float |

Также указывается проблемный компонент D_D1:

These devices failed to converge: D_D1

и причина прекращения расчетов из-за слишком резкого, скачкообразного переключения напряжения и/или тока источника, а также наличие предельных величин напряжений и токов (в определенные моменты расчетов)

These voltages failed to converge:

V(IN) = 1.000V \ 1.429uV

These supply currents failed to converge:

I(V_V1) = -10.00GA \ -10.00GA

Указывается последняя величина напряжения в цепи

Last node voltages tried were:

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( IN) 1.0000

Помимо этого может предлагаться решение проблемы, связанное с уменьшением градиента характеристики проблемного компонента путем уменьшения шага расчетов

Reducing minimum delta to make the circuit converge.

Внимание!

Состав сообщений, их характер и практические рекомендации по обеспечению расчетов могут меняться в зависимости от версии САПР. Некоторые оценочные версии не поддерживают в полном объеме указание сообщений о причинах срыва расчетов и выдачу рекомендаций по их устранению.

Вывод.

Используйте корректные модели компонентов в схемах, а также правильные схемотехнические решения, соответствующие параметрам используемых реальных компонентов. Программа расчетов обнаружила полупроводниковый элемент с особыми нестандартными свойствами, отличающимися от реальных компонентов. При этом в схеме имеется резистивный элемент RLoad, обеспечивающий протекание приемлемых величин токов в начальный момент, при фактически запертом (неоткрытом) «диоде» D1.

161

Проверка на допустимые скорости изменения основных параметров (величины производных)

В зависимости от типа устройства, физической интерпретацией этих производных может являться:

•проводимость, например диодов в режиме малых сигналов (small-signal conductance);

•крутизна передаточной характеристики, например транзисторов (transconductance);

•коэффициент усиления схемы (gain).

Модели, оторванные от реальных электронных компонентов, могут превысить лимит 1·1014 для скорости изменения величин (производных).

Резкие нарушения непрерывности или скачкообразный ход характеристик моделей может приводить к следующим последствиям:

•неопределенность в вычислении производных в точках перегиба;

•проводимость, вычисленная в ходе итерации вблизи точки перегиба, не может обеспечить приемлемый уровень приближения для следующей итерации;

•не прогнозируемый выход за пределы допустимых границ рабочей зоны (operating region) и, как следствие, получение неверных для сходимости решений (несовпадающих значений).

Меры по обеспечению задания начальных условий

Метод Ньютона-Рафсона гарантирует сходимость только в случае начала вычислений вблизи конечных значений расчетов. Не существует методов оценок, позволяющих определить необходимую точность начального (исходного) приближения.

PSpice-расчеты обеспечивают приемлемое решение за счет многократного повторения расчетов с вариацией параметров. Если полученное решение не сходится, программа расчетов уменьшает шаг, возвращается назад и повторяет расчеты.

Неверные исходные оценки могут приводить к отсутствию сходимости вычислений или получению неверных результатов.

На что следует обратить внимание.

1)Мощные электронные схемы могут не требовать обеспечения особо точного вычисления токов и напряжений (жестких допусков). Установка значений для ABSTOL=1мкА может помочь в проведении расчетов, если в схеме текут токи более нескольких ампер.

2)Вместе с тем, для токов на уровне 1000А и выше, увеличение ABSTOL до значений более 1мкА, скорее создаст проблемы, чем поможет их решить.

3)PSpice-расчеты не всегда обеспечивают лучшую сходимость при увеличении допустимых отклонений получаемых параметров или снижении точности расчетов (relaxed tolerances). Например, установка параметра RELTOL>0,01 может в действительности инициировать проблемы со сходимостью.

4)Установка значений GMIN в пределах от 1нСм до 10нСм часто обеспечивает решение проблем сходимости.

5)Установка значений GMIN > 10нСм может приводить к возникновению проблем сходимости.

Для решения проблем со сходимостью расчетов, в случае их возникновения, рекоменду-

ется следующая последовательность действий.

1.Проверка принципиальных схем (Circuit topology and connectivity). Подразумевается в первую очередь проведение проверки принципиальных схем на наличие ошибок и правильности подключения компонентов, а также настроек их параметров и атрибутов. Вы-

явленные ошибки и некорректные решения, с точки зрения проектирования принципиальных схем в САПР OrCAD, необходимо устранить.

2.Проверка корректности моделей и адекватности имитации реальных схем (Modelling Checks). Подразумевается проверка правильности и адекватности применения моделей

162

устройств и схем. Также подразумевается проверка правильности применяемых схемотехнических решений схем для моделирования и адекватности таких решений в совокупности с используемыми моделями устройств для получения параметров реальных схем (имитации их работы). При необходимости можно осуществлять определенную доработку принципиальных схем и корректировку настроек компонентов, если это допустимо с точки зрения имитации работы реальных схем. Также можно изменять модели и параметры моделей, если это не существенно снижает степень соответствия имитирующих схем реальным схемам. В ряде случаев может допускаться применение модели компонента, близкого по параметрам и назначению, в том случае, если модель требуемого компонента отсутствует или не работает должным образом.

3.Проверка настроек расчетов (PSpice Options). Подразумевается проведение проверки правильности настроек расчетов и соответствия настроек моделируемым схемам и видам расчетов.

Особенности указанной последовательности действий для обеспечения сходимости расчетов при проведении отдельных видов анализа представлены ниже.

4. Сходимость решений при проведении анализа Bias Point

Наиболее проблематичными расчетами с точки зрения обеспечения сходимости результатов можно считать выбор рабочих и начальных точек для основных видов анализа. Вначале программа расчетов пытается найти решение для полных величин (100%) токов и напряжений, задаваемых подключенными к схеме источниками питания. При этом решение не гарантируется. Но, в большинстве случаев, находится «сразу». Если этого не происходит, то уровни источников снижаются до низких, почти нулевых значений. При этом используются значения настолько низкие, чтобы можно было не учитывать нелинейности схем. Когда цепь линейна («линеаризована»), то решение может быть найдено относительно легко. Это решение будет найдено вблизи нулевой точки, естественно. Далее, программа расчетов поднимает значение источников питания вплоть до их 100%-значений. При этом варьируются шаги переменных.

Проверка принципиальных схем

Проверка правильности подключения компонентов и настроек их параметров является одной из основных проверок схемы на готовность к проведению расчетов. При этом необходимо обратить внимание на следующее:

•правильность и уникальность введения позиционных обозначений компонентов;

•правильность и уникальность введения имен цепей.

Помощь в проведении указанной проверки может обеспечить стандартная процедура

проверки схемы, осуществляемая средствами редактора CAPTURE. Проверка DRC (Design Rules Check) выполняется в окне организатора проекта редактора CAPTURE путем

выполнения команды: Tools>Design Rules Check…, для выбранного проекта. Результат проверки помещается в текстовый файл *.drc, доступный для просмотра и редактирования (при необходимости). В частности осуществляется проверка схем проекта:

•Checking Pins and Pin Connections – проверка контактов и подключений контактов компонентов;

•Checking for Unconnected Nets – проверка схем на наличие неподключенных цепей;

•Checking for Invalid References – проверка позиционных обозначений компонентов;

•Checking for Duplicate References – проверка дублирования позиционных обозначений компонентов;

•и др.

163

Кроме того необходимо проверять соблюдение синтаксиса входного языка управления заданием. Особое место в таких проверках занимает проверка правильности применения и описания источников сигнала и источников питания. Необходимо также проверять правильность задания величин размерности физических величин компонентов с использованием приставок для образования кратных и дольных единиц. В частности как показано в разделе 7

части 1 пособия необходимо отличать запись масштабного коэффициента «Мега» от «мили»:

1m = 1M ≠ 1MEG.

Особое внимание следует уделить проверке правильности подключения полярности

компонентов, в частности источников токов и напряжений.

При появлении сообщений типа “Floating node" или "No DC path to ground" необходимо обратить внимание на следующие схемотехнические решения:

•в схеме имеются цепи (узлы) к которым подключено менее двух контактов (полюсов)

компонентов (at least two connections at every node) см. первое ограничение PSpice-

расчетов в разделе 7 части 1 пособия;

•в схеме имеются цепи (узлы) или фрагменты схемы, от которых нет пути с конечным сопротивлением по постоянному току к земле (DC path from every node to ground), см. второе ограничение PSpice-расчетов в разделе 7 части 1 пособия;

Вчастности необходима проверка на правильность соединения компонентов схемы, как показано в разделе 7.3 «Правила подключения компонентов» части 1 пособия. Определен-

ную помощь в проверке на отсутствие неправильных подключений может обеспечить проверка DRC средствами редактора CAPTURE.

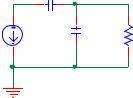

Кроме того, необходима проверка на наличие последовательно соединенных конденсаторов и/или источников токов, как показано, например на рис.П2.5.

|

C1 |

|

|

|

In |

|

Out |

0.1Adc |

I1 1uF |

C2 |

RLoad |

|

|

|

|

|

|

1uF |

4.7K |

|

|

|

10% |

0

Рис. П2.5. Схема с использованием последовательно соединенных конденсаторов и источника тока и изолированного от «земли» конденсатора C1

При запуске расчетов для схемы см. рис. П2.5 вычисления прерываются со следующим сообщением об ошибке.

ERROR – Node In is floating

Последовательные соединения источников тока и/или конденсаторов рекомендуется дополнять параллельным соединением резисторов, например имитирующих сопротивление изоляции проводников или сопротивление реального источника тока. «Плавающие» цепи рекомендуется дополнять резисторами, обеспечивающими путь с конечным сопротивлением

по постоянному току к земле и имитирующими, например, сопротивление изоляции проводников. В частности схему на рис. П2.5 можно дополнить резистором R=1MEG, подключен-

ным к цепи «In» и «земле», и имитирующим сопротивление изоляции или входное сопротивление осциллографа, используемого при проверке реальной цепи.

Примечание.

К проверке на отсутствие «плавающих» цепей можно отнести проверку правильности использования символа «глобальной земли» в принципиальной схеме. Этот символ является специальным и предназначен для введения в задание на моделирование 0-цепи. Все отдельные фрагменты принципиальной схемы должны тем или иным способом быть подключены к «глобальной земле». Для этого рекомендуется прямое подключение к

164

отдельным фрагментам схемы (если схема содержит такие фрагменты) символа «глобальной земли» или пря-

мое соединение проводниками с одним таким символом. Использование иных символов «земли» для этой цели, например «корпусной земли» (chassis ground), не допускается.

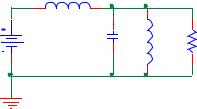

При появлении сообщений типа "Voltage source or inductor loop" необходимо обратить внимание на то, что программа расчетов не допускает использование контуров с нулевым сопротивлением по постоянному току, которые могут образовываться за счет последователь-

ного включения индуктивностей и/или источников напряжений, см. третье ограничение PSpice-расчетов в разделе 7 части 1 пособия. Пример указанной схемы показан на рис. П2.6.

|

L1 |

|

|

|

In |

|

|

Out |

|

V1 |

10uH |

C2 |

L2 |

|

|

RLoad |

|||

|

|

|

|

|

5Vdc |

|

1uF |

|

4.7K |

|

|

|

10uH |

10% |

0

Рис. П2.6. Схема с использованием последовательно соединенных индуктивностей и источники напряжения, образующие контур с нулевым сопротивлением по постоянному току

При запуске расчетов для схемы см. рис. П2.6 вычисления прерываются со следующим сообщением об ошибке.

ERROR -- Voltage source and/or inductor loop involving L_L1 You may break the loop by adding a series resistance

Контур с нулевым сопротивлением по постоянному току в схеме на рис. П2.6 образуется за счет последовательного включения индуктивностей L1 и L2 и источника напряжения V1. Последовательные соединения источников напряжения и/или индуктивностей рекомендуется дополнять небольшими по величине последовательными резисторами имитирующими сопротивление проводников или сопротивление реального источника напряжения.

Помимо представленного выше, при проведении проверки правильности применяемых схемотехнических решений и подключения компонентов необходимо обратить внимание следующее.

1)При использовании ABM-блоков и зависимых источников следует обеспечить использование корректных величин скоростей изменения параметров, в частности усиления. Также

необходимо использовать приемлемые представления элементов зависимых источников тока и напряжения, управляемых напряжением (E,G). Необходимо учитывать, чтобы не выполнялись операции LOG(0) и деление на 0.

2)Следует обеспечить использование достоверных моделей компонентов, особенно в случае разработки или редактирования моделей пользователем.

3)Следует использовать цифровые компоненты только в тех в схемах, где их применение действительно необходимо. В случае применения цифровых компонентов рекомендуется задавать начальные условия их работы, избегая неопределенных состояний.

Проверка корректности моделей и адекватности имитации реальных схем

При проверке моделей и условий применения моделей компонентов необходимо обратить внимание на следующие модели и особенности их применения.

Полупроводниковые приборы

165

В первую очередь необходимо осуществить проверку на реалистичность параметров используемой модели. Заданный параметр N=1e-6 модели диода (см. пример 3 данного раздела) явился причиной резкого перегиба (knee) ВАХ диода, настолько резкой, что стало прак-

тически невозможным обеспечить целостный, связный, непрерывный характер расчетов с учетом минимального шага изменения питания 1Е-6 (power supply step size limit of 1e-6).

Решение проблемы может заключаться в следующем:

•наиболее предпочтительным является использование моделей компонентов, разработанных производителем этих компонентов и в схемотехнических условиях применения, соответствующих рекомендованным для этих компонентов;

•при необходимости, можно разрабатывать и использовать собственные модели компонентов; такие разработки рекомендуется проводить опытным пользователям после всесторонней проверки правильности модели и адекватности ее применения.

Используемые математические выражения для поведенческого моделирования

Ограничение диапазона значений для тока и напряжений ±1Е10, при проведении PSpiceрасчетов, заставляет обеспечивать не выход результатов вычислений для токов и напряже-

ний за эти границы. Это особенно актуально при использовании зависимых источников и ABM-блоков.

Одним из возможных способов решения проблемы ограничения результатов расчетов, является использования ABM-блока (ограничителя) LIMIT, выполняющего функцию ограничения действия тех или иных блоков схемы. Примером оправданного применения подобных блоков может явиться схема усилителя с высоким коэффициентом усиления. Например, для компаратора или операционного усилителя с разомкнутой петлей обратной связи на низких частотах, усиление может составлять 105. Без использования ABM-блока (ограничителя) LIMIT, ограничивающего выходной сигнал усилителя величинами питающих напряжений, на выходе устройства может появиться высокий потенциал. Такой потенциал может вызвать цепную реакцию увеличения токов и напряжений в последующих каскадах схемы с выходом значений токов и напряжений за допустимые пределы. Также может быть превышена максимальная скорость изменения сигналов в последующих частях схемы.

Кроме того, зависимые источники требуется «выключать» в тех случаях, когда для источников питания осуществляется уменьшение их величин до значений вблизи 0 (0,001%). Это делается для того, чтобы избежать появления операции «деление на 0».

Незащищенные p-n переходы

Незащищенный p-n перехода без использования токоограничивающих резисторов может приводить к протеканию слишком высоких токов, обеспечивать слишком высокую скорость изменения сигналов или требовать использования слишком малых шагов (time step) для описания поведения устройства во временной области. Пример подобного включения диода приведен выше (см. пример 2 данного раздела).

Решение проблемы может заключаться в установке реального резистора, включенного последовательно с p-n переходом или диодом, если это не противоречит схемотехническим решениям, выбранным при проектировании данного устройства. Также можно воспользоваться установкой «фиктивного» резистора, имитирующего сопротивление проводников или сопротивление реального источника сигнала или питания.

Отсутствие пути протекания токов

Отсутствие резисторов (leakage resistance), обеспечивающих протекание приемлемого уровня тока в схеме, имеющей компоненты с высоким сопротивлением (входным сопротив-

лением), приводит к появлению высокого напряжения (потенциала), который может превысить лимит 1,0E10 вольт.

166

Одним из примеров подобных схемотехнических решений является выбор неверного направления источника тока. При попытке задать ток от идеального источника в запертый p-n переход без использования шунтирующего резистора, обеспечивающего протекания тока в петле: подача тока - возврат тока, можно получить очень высокие уровни напряжения. Напряжение на p-n переходе может превысить величину 1.0Е10 вольт.

Другой пример подобных схемотехнических решений, относится к типичным ошибкам в проектировании усилителей или буферов систем сбора-обработки данных. Операционный усилитель с полевыми транзисторами на входе используется в неинвертирующем или буферном включении. Без специальных решений, обеспечивающих протекание токов в схеме подобный усилитель «запирает» ее, что также может приводить к появлению высокого потенциала в схеме. Кроме того, могут возникнуть проблемы детектирования нежелательных источников токов со снижением уровней С/Ш. Также это может приводить к снижению скорости перезаряда емкостей (паразитных емкостей) и деградации динамических характеристик схемы.

Решение проблемы может заключаться в установке, при проектировании данного устройства, реального резистора, обеспечивающего возврат тока схемы (например, от сигнальной линии на землю). Также можно воспользоваться установкой «фиктивного» резистора, имитирующего сопротивление изоляции проводников.

Ключевые элементы

При проведении PSpice-расчетов такие компонента как ключи могут сильно влиять на формируемые параметры схемы в области «усиления» или скорости изменения величин (производных). В PSpice-расчетах они ограничены величинами 1.0Е14. Особое внимание следует обратить на каскадное последовательное соединение подобных компонентов. Такая ситуация может возникнуть, например, при проектировании схем, имитирующих работу выходных элементов цифровых устройств (totem-pole switches) и использующую несколько таких узлов.

При разработке таких схем необходимо учитывать, что каскадное включение двух таких ключей, как правило, работает надлежащим образом, но включение более чем двух ключей часто может приводить к возникновению проблем.

Общего и универсального решения проблемы для любых используемых компонентов не существует. Особое внимание следует обращать на схемы, использующие несколько элемен-

тов в ключевом включении. К числу таких можно отнести смешанные схемы с использованием ключевых элементов (с PSpice-моделями), ABM-блоков и МОП-транзисторов в ключе-

вом включении. Особого внимания требуют высоковольтные схемы, например драйверы верхних ключей мостовой схемы управления электродвигателями (High-Side Switch).

Решение проблемы может заключаться в надлежащем использовании моделей реальных компонентов, разработанных специалистами. Применение моделирующих компонентов должно осуществляться в схемотехнических решениях и в условиях, предусмотренных для работы имитируемых реальных компонентов.

Использование настроек расчетов

При проведении проверки настроек расчетов необходимо обратить внимание на использование следующих операторов и опций, а также особенностей их применения.

Использование настроек опции ITL1

Вместе с оператором .OPTIONS можно использовать опцию ITL1, ограничивающую максимальное число итераций при расчетах по постоянному току Bias Point и DC. По умолчанию ITL1=150. С помощью введения в задании на моделирование следующей строки

167

.OPTIONS ITL1=400

осуществляется увеличение до 400 числа итераций при расчетах по постоянному току перед отказом программы расчетов от дальнейшего проведения расчетов на текущем уровне. Увеличение числа итераций более 400, обычно не способствует решению проблем со сходимостью расчетов, тем более для сложных схем.

Задание начальных условий

Для задания начального приближения величин напряжения в цепи используется оператор .NODESET. Обычно его рекомендуется использовать для наиболее «проблемных» цепей схемы. В том случае, если расчеты прекращены из-за отсутствия сходимости при расчетах рабочих точек необходимо выяснить достигнуты ли при расчетах величины потенциалов. В первую очередь надо попытаться задать условия для тех узлов, в которых выведенные в выходной файл потенциалы последней попытки расчета, наиболее отличаются от ожидаемых [1]. Особенно важно задание приближенных значений потенциалов для схем с использованием высокоимпедансных входов и входов компонентов с высоким усилением.

Оператор .NODESET не «фиксирует» окончательно исходные значения напряжений для выбранных цепей. Он удерживает потенциалы указанных в операторе узлов или цепей схемы на время проведение расчетов потенциалов остальных цепей, вплоть до достижения по остальным цепям достаточно правдоподобных стабильных потенциалов. Затем «фиксированные источники» снимаются и путем проведения дополнительных итераций осуществляются расчеты окончательных потенциалов схемы.

В ряде случаев, отказ от задания всех или некоторых потенциалов цепей, может помочь программе расчетов решить проблему со сходимостью вычислений.

Использование флаг-опции STEPGMIN и варьирование GMIN

С помощью введения в задании на моделирование следующей строки

.OPTIONS STEPGMIN

разрешается пошаговая вариация параметра GMIN. Будучи разрешенной, эта опция обеспечивает включение алгоритма расчета режима по постоянному току с вариацией проводимости GMIN в случае отсутствия сходимости метода Ньютона – Рафсона.

Включение опции позволяет в случае отсутствия сходимости метода Ньютона – Рафсона при 100%-величинах источников питания, осуществить поиск решения с использованием алгоритма вариации параметра GMIN. Затем, в случае неудачи, с использованием алгоритма вариации параметра GMIN, применяется метод вариации источников питания. Метод вариации источников питания предусматривает снижение параметров источников питания до величин, близких к нулевым величинам. Далее, осуществляется пошаговое увеличение вели-

чин источников питания.

Алгоритм вариации параметра GMIN (GMIN stepping algorithm) предусматривает поиск решения при старте повторяющихся циклов расчетов с начальной величиной GMIN, вычисляемой как произведение 1.0E10 на номинальную величину GMIN. По умолчанию номинальная величина GMIN составляет 1,0E-12. Если решение находится, то текущая величина GMIN уменьшается в 10 раз и делается новая попытка расчетов. Так продолжается до тех пор, пока или GMIN не возвращается к номинальной величине, или расчеты не прекращаются по причине отсутствия сходимости решений на очередном этапе с промежуточным значе-

нием GMIN. В последнем случае, значением GMIN восстанавливается до номинальной величины и осуществляется пошаговое увеличение величин источников питания (power supplies are stepped).

168

Пошаговая вариация параметров источников питания

Пошаговая вариация параметров источников питания (Power supply stepping) использует специальный алгоритм непрерывного поиска решений при варьировании параметров источ-

ников от величин, близких к нулевым (0,001%), до возврата к 100%-уровням. Минимальный шаг составляет 1e-6 (0,0001%). Первые шаги расчетов используют малые величины парамет-

ров источников питания, для напряжений могут использоваться нулевые величины, поэтому нужно с особой осторожностью относиться к проведению расчетов, где могут использоваться напряжения в знаменателях.

5. Сходимость решений при проведении анализа DC Sweep

При проведении анализа DC Sweep используется комбинированный подход (hybrid approach) к обеспечению сходимости результатов.

Вначале, как и для анализа Bias Point, применяется решение, связанное с вариацией параметров источников питания. То есть, программа расчетов пытается найти решение для полных величин (100%) токов и напряжений, задаваемых подключенными к схеме источниками питания. Если решение отсутствует, то уровни источников снижаются до низких, почти нулевых значений. При этом решение может быть найдено относительно легко. Далее, программа расчетов поднимает значение источников питания вплоть до их 100%-значений.

В отличие от последовательности шагов расчетов для анализа Bias Point, при проведении анализа DC Sweep не производится варьирование шага, а результаты расчетов параметров предыдущего шага учитываются как начальные условия для последующих расчетов текуще-

го шага. Если решение для текущего шага не находится, то для этого шага применяется ме-

тод расчета как и для анализа Bias Point (Bias Point algorithm).

Этот процесс в целом сильно зависит от непрерывности или связности в расчетах. Требуется, чтобы цепи были линейны при выключении источников питания.

Проверка принципиальных схем и проверка корректности моделей и адекватности имитации реальных схем в данном виде анализа соответствует аналогичной последовательности действий при проведении анализа Bias Point.

Использование настроек расчетов

При проведении проверки настроек расчетов необходимо обратить внимание на использование следующих операторов и опций, а также особенностей их применения.

Использование настроек опции ITL2

Вместе с оператором .OPTIONS можно использовать опцию ITL2, ограничивающую максимальное число итераций при расчетах по постоянному току Bias Point и DC, после которого повышаются питающие напряжения. По умолчанию ITL2=20. С помощью введения в

задании на моделирование следующей строки

.OPTIONS ITL2=100

осуществляется увеличение до 100 числа итераций.

Варьирование величины шага

Нарушение непрерывности хода изменения тех или иных характеристик исследуемых объектов может привести к проблемам сходимости. Для выхода из подобной ситуации при проведении расчетов DC Sweep можно воспользоваться увеличением или уменьшением величины шага изменения параметров расчетов.

169

Увеличение шага может помочь «обойти неоднородность», тогда как уменьшение шага может помочь найти последовательность «промежуточных» значений, которые также способны обеспечить непрерывность хода изменения характеристик исследуемой схемы. В ряде случаев уменьшение шага является более предпочтительным и обеспечивающим непрерывный путь решений от точки к точке.

Смена вида расчетов

В ряде случаев помочь в решении проблем сходимости может расчеты рабочей точки с помощью другого вида анализа. Для этого можно попробовать заменить расчет по постоянному току расчетом переходного процесса при включении питания схемы. Конкретные действия в этом случае могут быть следующие [1]:

•источники постоянного напряжения и тока надо заменить на импульсные источники сигналов, обеспечивающих подачу постепенно нарастающих от нуля до номинала сигналов с достаточно большими фронтами;

•источники входных сигналов, если таковые имеются в схеме, должны быть заменены ис-

точниками питания с постоянными уровнями, равными начальным значениям источников сигналов.

Затем просчитывается переходной процесс в схеме в течение некоторого отрезка времени T, достаточного для того, чтобы все потенциалы схемы достигли своих установившихся значений [1]. Время расчета переходного процесса T должно заведомо превышать максимальную постоянную времени в схеме. Недостаточная величина T приведет к ошибкам в определении установившегося режима, который будет отличаться от расчета по постоянному току [1].

Полученное в результате расчета состояние схемы можно запомнить оператором

.SAVEBIAS и далее воспользоваться оператором .LOADBIAS. Также для задания полученных потенциалов схемы можно воспользоваться оператором .NODESET.

Примечание.

В ряде схем с использованием высокоскоростных переключений (компараторы, триггеры Шмитта, детекторы пониженного питания и др.) уменьшение шага может не помочь, так как в них при бесконечно малом изменении входного сигнала режим изменяется скачком [1]. В этих случаях решение проблемы может сводиться к замене DC анализа расчетом переходного процесса при медленном квазистатическом изменении входного сигнала. На вход при этом подается линейно изменяющийся сигнал, скорость изменения которого должна выбираться такой, чтобы на результатах расчета не сказывались реактивности схемы [1]. Если желательно получить гистерезисную характеристику, то после нарастания сигнала следует предусмотреть столь же медленный его спад, чтобы просчитать обе ветви характеристики [1].

6. Сходимость решений при проведении анализа Transient

Расчеты анализа переходных процессов начинаются при известном начальном условии (bias point). Затем для последующей (по временному отрезку) точки расчетов последнее известное решение предыдущей точки используется как исходное (нулевое) приближение. Если необходимо шаг по времени дает «обратный ход» для создания новой точки с целью добиться сходимости метода Ньютона-Рафсона.

Теоретически для проведении анализа Transient используются подходы, которые применялись и для обеспечения расчетов Bias Point. Однако на практике такие подходы нуждаются

в коррекции.

Transient-анализ может быть не выполнен если шаг во времени слишком мал. Это может быть по двум причинам:

•итерации метода Ньютона-Рафсона не могут обеспечить сходимость решения даже при наименьшем шаге по времени;

170