ФОЭ / СлайдыФОЭчасть2

.pdf

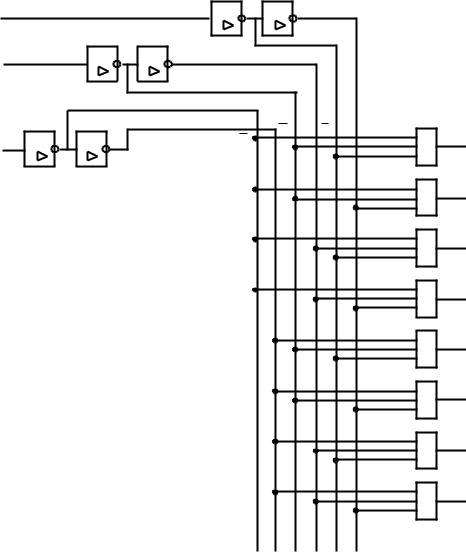

Демультиплексоры

Демультиплексоры в функциональном отношении противоположны мультиплексорам. Здесь сигналы с одного информационного входа распределяются в желаемой последовательности по нескольким выходам. Выбор нужной выходной шины, как и в мультиплексоре, обеспечивается кодом на адресных входах. При n адресных входах демультиплексор может иметь в зависимости от конструкции до 2n выходов.

Логическая структура простого демультиплексора вида 1 : 4 представлена на рисунке.. Здесь В я А — адресные входы, х-—информационный вход, V — разрешающий.

ДЕШИФРАТОРЫ И ШИФРАТОРЫ

Дешифратором или декодером называют комбинационное устройство, позволяющее распознавать числа, представленные позиционным n – разрядным кодом. Можно также сказать, что декодер это устройство, преобразующее двоичный код в унитарный. В общем случае дешифратор имеет N входов и m выходов. Из всех m выходов дешифратора активный уровень имеется только на одном, а именно на том, номер которого равен поданному на вход двоичному числу. На остальных выходах дешифратора уровни напряжения неактивные.

Если декодер имеет n входов и m выходов, то m=2n. Такой декодер называют полным. У неполного декодера используется лишь часть возможных наборов, и имеется меньшее число выходов.

Декодер используют, когда нужно обращаться к различным цифровым устройствам, и при этом номер устройства – его адрес – представляется двоичным кодом. Входы декодера (их иногда называют адресными входами) часто нумеруют не порядковыми номерами, а в соответствии с весами двоичных разрядов, т. е. не 1, 2, 3, 4…, а 1, 2, 4, 8, 16… . Число входов декодера указывают таким образом: декодер 3-8 (три в восемь)

|

|

|

DC |

0 |

|

|

|

|

|

||

|

|

|

|

1 |

|

|

|

|

|

|

|

a1 |

|

1 |

|

2 |

|

|

|

|

|||

|

|

3 |

|

||

a2 |

|

2 |

|

|

|

|

|

4 |

|

||

|

|

|

|||

a4 |

|

4 |

|

5 |

|

|

|

|

|||

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

E |

|

7 |

|

|

|

|

|

||

|

|

|

|

|

|

|

Дешифратор 3-8 |

|

|

|

|

|

||

|

|

1 |

1 |

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

1 |

1 |

|

|

|

|

|

|

a2 |

|

|

|

|

|

|

|

|

1 |

1 |

a4 |

a4 a2 |

a2 |

a1 |

a1 |

& |

|

|

|

|

|

Y0 |

||||

a4 |

|

|

|

|

|

|

|

|

|

000 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

001 |

|

|

|

|

& |

Y1 |

|

|

|

|

|

|

|

|

|

|

|

010 |

|

|

|

|

& |

Y2 |

|

|

|

|

|

|

|

|

|

|

|

011 |

|

|

|

|

& |

Y3 |

|

|

|

|

|

|

|

|

|

|

|

100 |

|

|

|

|

& |

Y4 |

|

|

|

|

|

|

|

|

|

|

|

101 |

|

|

|

|

& |

Y5 |

|

|

|

|

|

|

|

|

|

|

|

110 |

|

|

|

|

& |

Y6 |

|

|

|

|

|

|

|

|

|

|

|

111 |

|

|

|

|

& |

Y7 |

|

|

|

|

|

|

|

|

|

а – условное обозначение, б – структурная схема линейного дешифратора

Каскадное соединение дешифраторов

E a16 a8

1 DC 0

1

2 2

E 4 3

a4 a2 a1

E DC 0

1

1  2 4 0 7

2 4 0 7

E DC 0

1

2

2  4 1 7

4 1 7

E DC 0

1

1  2 4 2 7

2 4 2 7

E DC 0

1

2

4 3 7

0

7

8

15

16

23

24

31

Для наращивания разрядности дешифратора стандартные ИМС объединяются в группы, соединенные в два каскада.

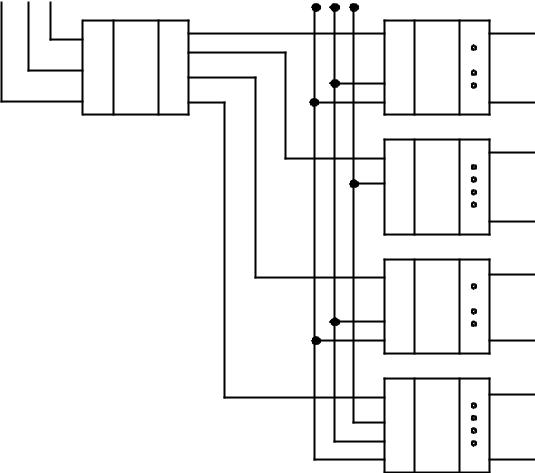

Двухкаскадный дешифратор с прямоугольным (матричным) дешифратором во втором каскаде

Разряды адреса здесь разбиты на две группы, каждая из которых не зависимо от другой расшифровывается своим дешифратором первого каскада DC1 и DC2. При любой комбинации значений входных переменных оказывается выбранными одна строка и один столбец сетки, в узлах которой расположены элементы И второй ступени. В результате каждый входной набор возбуждает выход единственного соответствующего ему элемента И.

Шифраторы

Шифраторы – устройства, обеспечивающие выдачу определенного кода в ответ на возбуждение одного из входов. Шифраторы широко применяются для преобразования десятичных чисел и буквенных символов в двоичный код при вводе информации в цифровые устройства. Например, при нажатии клавиши на клавиатуре шифратор формирует код, соответствующий этой клавише.

Шифраторы выполняют функцию, обратную дешифратору. Шифратор имеет m входов и n выходов. При подаче сигнала на один из входов (обязательно на один и не более) на выходе шифратора появляется двоичный код номера возбужденного выхода. Заметим, что m=2n.

Шифраторы применяют в устройствах, преобразующих один вид кода в другой. При этом вначале дешифрируется комбинация исходного кода, в результате чего на соответствующем выходе дешифратора появляется лог. 1. Это отображение входного кода, значение которого определено номером возбужденного выхода дешифратора, подается на шифратор, организованный с таким расчетом, чтобы каждый код на входе дешифратора вызывал появление заданного кода на выходе шифратора.

Схема шифратора

На выходах шифратора (кодера) устанавливается двоичный код, соответствующий десятичному номеру возбужденного информационного входа. При построении шифратора для получения на выходе натурального двоичного кода учитывают, что единицу в младшем разряде такого кода имеют нечетные десятичные цифры 1, 3, 5, 7, ... , т. е. на выходе младшего разряда должна быть 1, если она есть на входе № 1 или на входе № 3 и т. д.

Поэтому входы под указанными номерами через элемент ИЛИ соединяются с выходом младшего разряда. Единицу во втором разряде двоичного кода имеют десятичные цифры 2, 3, 6, 7, . . .; входы с этими номерами через элемент ИЛИ должны подключаться к выходу шифратора, на котором устанавливается второй разряд кода. Аналогично, входы 4, 5, 6, 7,...

через элемент ИЛИ должны быть соединены с выходом, на котором устанавливается третий разряд, так как их коды имеют в этом разряде единицу, и т. д.

Триггеры

Триггером называется устройство, имеющее два устойчивых состояния и сохраняющее любое из них сколь угодно долго после снятия внешнего воздействия, вызвавшего переход триггера из одного состояния в другое. Поэтому говорят, что триггер обладает памятью.

По способу записи информации триггеры могут быть асинхронными и синхронными. Триггер называют асинхронным, если сам сигнал, несущий информацию, вызывает его переключение. В синхронных (тактируемых) триггерах информация записывается при одновременном воздействии информационного сигнала и синхронизирующего (разрешающего) импульса.

Синхронизация может осуществляться импульсом (потенциалом) или перепадом потенциала (фронтом или срезом импульса). В первом случае (статическое управление) сигналы на информационных входах оказывают влияние на состояние триггера в течение всего времени наличия синхроимпульса. Во втором случае (динамическое управление) воздействие информационных сигналов проявляется только в моменты изменения потенциала на входе синхронизации, т.е. при переходе его от 0 к 1 (фронт) или от 1 к 0 (срез).

По функциональному признаку различают RS-триггеры, D-триггеры, Т-триггеры и JK-триггеры, а также их комбинации.

Асинхронный RS-триггер с прямым (а) и инверсным (б) управлением

S

R

Q

Самый простой из триггеров – статический RS-триггер. Он имеет два входа: S (set) – установка и R (reset)

– сброс.

У RS-триггеров с прямым управлением (управлением уровнем логической 1) при приходе на вход S сигнала высокого уровня (логической 1) на прямом выходе Q устанавливается сигнал логической единицы. Этот сигнал присутствует на выходе до тех пор, пока не придет сигнал сброса на

вход R.

Тактируемый RS-триггер

Тактируемый (синхронный) RS-триггер отличается от асинхронного наличием дополнительного входа C, на который подаются импульсы синхронизации. Переключение такого триггера осуществляется не сразу после изменения состояния входов S и R, которое должно вызвать переключение триггера, а по приходу первого после такого изменения синхронизирующего импульса.

В зависимости от внутренней структуры триггер может переключаться или по фронту тактового импульса, или по его срезу. Активные сигналы на управляющих входах R и S также могут иметь либо уровень логической единицы, либо уровень логического нуля. Как правило, в микросхемах ТТЛ активный уровень – уровень логического нуля.