ФОЭ / СлайдыФОЭчасть2

.pdf

Микросхемы ТТЛ с транзисторами Шотки

Транзисторы с диодами Шотки часто называют транзисторами с барьером Шотки или просто транзисторами Шотки. Когда транзистор заперт или находится в ненасыщенном режиме, потенциал коллектора выше потенциала базы, а значит, диод смещен в обратном направлении и не влияет на работу транзистора

Распределение напряжения на переходах биполярного транзистора:

а — распределение напряжений в насыщенном транзисторе; б — биполярный транзистор с диодами Шотки

Базовый элемент маломощных микросхем ТТЛШ

а—принципиальная схема; б—передаточные характеристики

Принципиальная схема логического элемента ТТЛ с открытым коллектором

Выходы некоторых микросхем выполнены так, что верхний выходной транзистор и относящиеся к нему элементы отсутствуют. Это так называемые элементы со свободным (открытым) коллектором. На выходе его формируется только сигнал низкого уровня, поэтому для нормальной работы выходного транзистора коллектор следует подключать к источнику питания через внешнюю нагрузку-резистор, элемент индикации, реле и т. п.

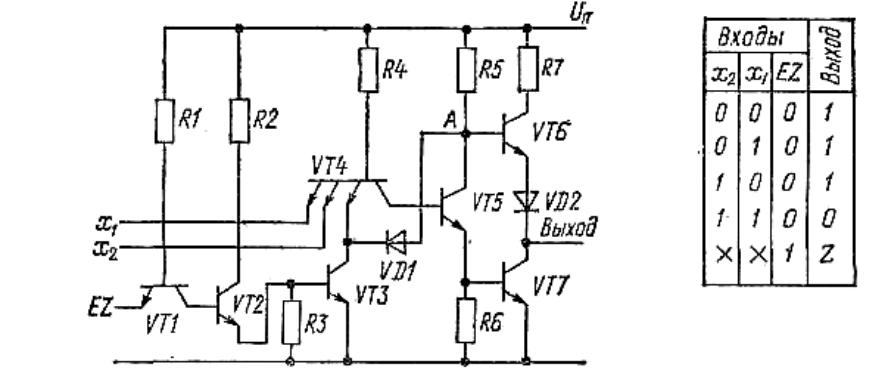

Логические элементы ТТЛ с тремя выходными состояниями

На рисунке показан один из способов обеспечения трех состояний в микросхемах ТТЛ. Эта схема отличается от базовой наличием дополнительных транзисторов VT1—VT3 и диода VD1, Когда транзистор VT3 заперт, схема действует подобно обычному логическому элементу, поскольку диод VD1 смещен в обратном направлении. При открытом транзисторе VT3 диод VD1 также открыт и напряжение в точке А близко к нулю. Транзистор VT6 при этом заперт.

В таблице Z — высокоимпедансное состояние, X — любое логическое состояние (О или 1)

Оценка задержки сигналов

Физическая структура полевых транзисторов КМОП (инвертор с входной защитной цепочкой)

Особенность конструкции приборов КМОП-структуры состоит в том, что транзисторы с каналами n- и р-типа выполнены на общей подложке.

Особый р-карман служит для электрической изоляции n-канального транзистора от подложки, имеющей тот же тип проводимости. Электрические и временные параметры обоих транзисторов близки. На рисунке показана также схема защиты входов транзисторов от перегрузок.

Принципиальная схема инвертора КМОП-структуры

Базовыми элементами для различных функциональных узлов КМОП-структуры являются инвертор и двунаправленный тактируемый ключ. Эти элементы состоят только из МОПтранзисторов с каналами обоих видов проводимости и не содержат резисторов и конденсаторов. Простой инвертор состоит из двух встречно включенных МОП-транзисторов с индуцированными каналами р- и n-типа. Оба затвора соединены между собой и являются общим входом.

Логические элементы КМОП-микросхем

Для организации логических элементов вида И—НЕ (И) либо ИЛИ—НЕ (ИЛИ) транзисторы одного типа соединяются параллельно, а другого — последовательно. Особенностью логических элементов является наличие двух ярусов транзисторов относительно выходного вывода. Логическая функция, выполняемая всей схемой, определяется транзисторами нижнего яруса. Для реализации операции И—НЕ в положительной логике транзисторы с n-каналом включаются последовательно друг с другом, с р-каналом — параллельно, а для операции ИЛИ—НЕ

— наоборот.

МУЛЬТИПЛЕКСОРЫ

Назначение мультиплексоров (от англ. multiplex — многократный) — коммутировать в желаемом порядке информацию, поступающую с нескольких входных шин, на одну выходную в зависимости от управляющего сигнала, заданного двоичным кодом. С помощью мультиплексора осуществляется временное разделение информации, поступающей по разным каналам. Мультиплексор можно уподобить бесконтактному многопозиционному переключателю.

Мультиплексор-селектор вида 2:1:

управляемый контактами (а); управляемый сигналом (б)

Пирамидальный мультиплексор вида 32: 1

Пирамидальные мультиплексоры строятся по ступенчатому принципу, причем обычно применяются две, реже — три и более ступени. Пирамидальный характер схемы состоит в том, что каждая ступень, начиная с первой, имеет больше входов, чем последующая. Младшие разряды кода адреса подаются на адресные входы первой ступени, а ступеням более высокого ранга соответствуют старшие разряды адресного кода.

Недостатками пирамидального наращивания следует считать повышенный расход микросхем, а также сравнительно невысокое быстродействие из-за суммирования задержек при последовательном прохождении сигналов по ступеням пирамиды