Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение

высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ

УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

РАЗРАБОТКА ВЫЧИСЛИТЕЛЬНОГО БЛОКА

Отчет по лабораторной работе №8 по дисциплине «Электроника и схемотехника 2»

Вариант №18

__.__.2022

Руководитель

__.__.2022

Томск 2022

Введение

Цель работы – научиться совместно применять устройства средней степени интеграции.

Постановка задачи. Разработать обобщённую схему устройства. Составить таблицы функционирования операционных блоков. Создать схему реализации вычислительного блока, выполняющего заданные функции. Составить план моделирования в двух режимах. Описать построенную схему на коде hdl и

промоделировать его.

2. ОБОЩЕННАЯ ФУНКЦИОНАЛЬНАЯ СХЕМА

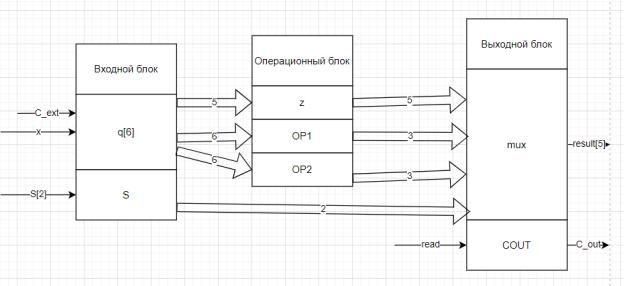

На рисунке 2.1 представлена обобщенная функциональная схема.

Рисунок 2.1 – Функциональная схема Устройство на вход получает последовательный код, который

преобразуется в параллельный во входном блоке. После преобразования коды целиком или частично передаются в операционный блок, где выполняются требуемые по варианту задачи. В выходном блоке mux выдает результат зависимо от кода S.

3.ТАБЛИЦЫ ФУНКЦИОНИРОВАНИЯ

Втаблице 3.1 представлена таблица функционирования проверки 4b5b-

кода.

Таблица 3.1 – таблица функционирования

Код операции |

|

|

Входы |

|

|

|

|

Выходы |

|

|

|||||

x4 |

x3 |

|

x2 |

|

x1 |

x0 |

ST2 |

ST1 |

|

SP2 |

|

SP1 |

FB |

||

|

|

|

|

|

|

||||||||||

0 |

1 |

1 |

1 |

|

0 |

|

0 |

0 |

0 |

1 |

|

0 |

|

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

|

0 |

1 |

1 |

0 |

|

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

|

0 |

1 |

0 |

0 |

|

0 |

|

1 |

0 |

0 |

1 |

0 |

0 |

|

1 |

|

1 |

1 |

0 |

0 |

|

1 |

|

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

|

1 |

1 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

0 |

1 |

|

1 |

|

0 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

|

0 |

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

|

0 |

|

1 |

1 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

|

1 |

|

0 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

|

1 |

|

0 |

1 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

|

1 |

|

1 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

|

0 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

1 |

0 |

|

0 |

|

0 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

0 |

1 |

1 |

1 |

|

0 |

|

0 |

1 |

0 |

0 |

|

0 |

|

0 |

1 |

В таблице 3.2 представлена таблица истинности для логической

операции

Таблица 3.2 – таблица функционирования

|

Код |

|

|

Входы |

|

|

|

Выходы |

|

|||

операции |

A2 |

A1 |

A0 |

B2 |

B1 |

B0 |

OP1-2 |

|

OP1-1 |

OP1-0 |

||

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

Продолжение таблицы 3.2

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

Продолжение таблицы 3.2

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

В таблице 3.3 представлена таблица истинности арифметической операции A – B + 1

Таблица 3.2 – таблица функционирования

|

Код |

|

|

Входы |

|

|

|

Выходы |

|

|||

операции |

A2 |

A1 |

A0 |

B2 |

B1 |

B0 |

OP1-2 |

|

OP1-1 |

OP1-0 |

||

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

|

0 |

0 |

Продолжение таблицы 3.3

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

В таблице 3.4 представлен план моделирования.

Таблица 3.4 – План моделирования

|

|

|

|

|

Входы |

|

|

|

|

|

|

Выход |

|

|

||||

|

Код |

|

A |

|

|

|

|

B |

|

R |

Q4 |

Q3 |

|

Q2 |

|

Q1 |

Q0 |

|

операции |

X5 |

X4 |

|

X3 |

|

X2 |

X1 |

X0 |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||

0 |

|

1 |

- |

0 |

|

1 |

|

1 |

0 |

1 |

0 |

0 |

0 |

|

0 |

|

1 |

0 |

0 |

|

1 |

- |

0 |

|

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

1 |

|

0 |

0 |

1 |

|

0 |

|

0 |

0 |

1 |

0 |

- |

- |

|

1 |

|

0 |

1 |

1 |

|

0 |

1 |

0 |

|

1 |

|

1 |

1 |

0 |

0 |

- |

- |

|

1 |

|

1 |

0 |

1 |

|

1 |

0 |

1 |

|

0 |

|

1 |

0 |

0 |

0 |

- |

- |

|

1 |

|

1 |

1 |

1 |

|

1 |

1 |

0 |

|

0 |

|

1 |

0 |

0 |

0 |

- |

- |

|

0 |

|

0 |

1 |

0 |

|

0 |

- |

- |

|

- |

|

- |

- |

- |

0 |

0 |

0 |

|

1 |

|

0 |

1 |

x |

|

x |

- |

- |

|

- |

|

- |

- |

- |

1 |

0 |

0 |

|

0 |

|

0 |

0 |

0 |

|

0 |

- |

- |

|

- |

|

- |

- |

- |

0 |

0 |

0 |

|

0 |

|

0 |

1 |

На рисунке 5.1 можно увидеть план моделирования. На временном интервале от 0 до 1.6us можно увидеть код операции 01 и ввод данных в последовательности 001101. На следующем интервале так же представлен код операции 01, где вводятся данные 001100. На интервале от 4us до 5.6 us

представлен код операции 10, где вводятся данные 010001. На следующем интервале 6-7.2us представлено моделирование для кода операции 11 с вводом данных 010100. На интервале 7.6-8.8us представлено моделирование для кода операции 10 с вводом данных 101110. На последнем интервале 9.2-10.8us

представлено моделирование для кода операции 11 и ввода данных 100100. На

5.6us есть активный уровень сигнала R, который сбрасывает данные, которые уже записаны в result и q.

4. ФУНКЦИОНАЛЬНАЯ СХЕМА

На рисунке 4.1 приведена функциональная схема.

Рисунок 4.1 – функциональная схема На рисунке 4.2 представлен входной блок схемы. В регистры по

убывающему фронту внешнего синхросигнала C_ext сохраняются входные данные х, данные для выполнения операции и код операции.

Рисунок 4.2 – Входной блок На рисунке 4.3 представлен операционный блок. Счетчик по заднему

фронту C_ext считает количество операций. С помощью дешифраторов и функций И выполнена задача. Элементы or и not выполняют логическую операцию, а add_sub – арифметическую.

Рисунок 4.3 – Операционный блок

На рисунке 4.4 представлен выходной блок. При подачи сигнала read

формируются 2 выхода, C_out1 и C_out2. Мультиплексор выбирает, какой из выходов будет осуществляться.