Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронновычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ СЧЕТЧИКОВ

Отчет по лабораторной работе №5 по дисциплине «Электроника и схемотехника 2»

Вариант №19

Студент гр.

Руководитель

Томск 2022

Введение

Цель работы – изучить двоичные счетчики, их принципы построения и

работы.

Постановка задачи:

1.Составить таблицы истинности для схем согласно варианту.

2.Собрать заданные схемы счетчиков, делителя частоты и формирования задержки.

3.Описать устройства с помощью HDL.

3. Промоделировать работу схем и проверить с таблицами функционирования.

Задания по варианту:

- описать асинхронный вычитающий счетчик на основе Т-триггера,

модуль счета – 30;

-описать синхронный суммирующий счетчик с синхронным сбором и нарастающим фронтом, модуль счета – 24;

-решить задачу формирования на выходе сигнала с частотой 1785714

Гц;

- реализовать схему формирования импульсов с задержкой между ними

500 нс, при частоте 50 МГц.

2

1 АСИНХРОННЫЙ ВЫЧИТАЮЩИЙ СЧЕТЧИК

1.1 ТАБЛИЦА ИСТИННОСТИ

Ниже приведена таблица истинности 1.1 для вычитающего счетчика с

модулем счета 30.

Таблица 1.1 – Таблица истинности вычитающего счетчика

№ |

Выходы |

|

|

|

|

сигнала |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|

|

|

|

|

|

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

2 |

1 |

1 |

0 |

1 |

1 |

3 |

1 |

1 |

0 |

1 |

0 |

4 |

1 |

1 |

0 |

0 |

1 |

5 |

1 |

1 |

0 |

0 |

0 |

6 |

1 |

0 |

1 |

1 |

1 |

7 |

1 |

0 |

1 |

1 |

0 |

8 |

1 |

0 |

1 |

0 |

1 |

9 |

1 |

0 |

1 |

0 |

0 |

10 |

1 |

0 |

0 |

1 |

1 |

11 |

1 |

0 |

0 |

1 |

0 |

12 |

1 |

0 |

0 |

0 |

1 |

13 |

1 |

0 |

0 |

0 |

0 |

14 |

0 |

1 |

1 |

1 |

1 |

15 |

0 |

1 |

1 |

1 |

0 |

16 |

0 |

1 |

1 |

0 |

1 |

17 |

0 |

1 |

1 |

0 |

0 |

18 |

0 |

1 |

0 |

1 |

1 |

19 |

0 |

1 |

0 |

1 |

0 |

20 |

0 |

1 |

0 |

0 |

1 |

21 |

0 |

1 |

0 |

0 |

0 |

22 |

0 |

0 |

1 |

1 |

1 |

23 |

0 |

0 |

1 |

1 |

0 |

24 |

0 |

0 |

1 |

0 |

1 |

25 |

0 |

0 |

1 |

0 |

0 |

26 |

0 |

0 |

0 |

1 |

1 |

27 |

0 |

0 |

0 |

1 |

0 |

28 |

0 |

0 |

0 |

0 |

1 |

29 |

0 |

0 |

0 |

0 |

0 |

30 |

1 |

1 |

1 |

0 |

1 |

|

|

|

3 |

|

|

1.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

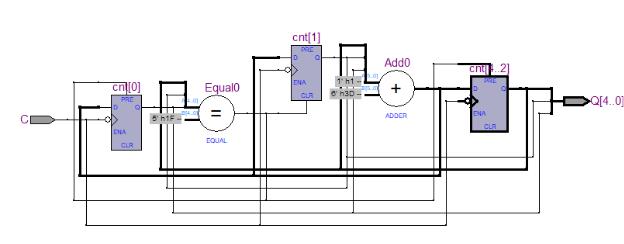

На рисунке 1.1 представлена функциональная схема асинхронного вычитающего счетчика.

Рисунок 1.1 – Функциональная схема асинхронного вычитающего счетчика

1.3 МОДЕЛИРОВАНИЕ

Было выполнено моделирование составленной функциональной схемы из пункта 1.2. На рисунке 1.2 изображен результат моделирования в режиме

Timing.

Рисунок 1.2 – Моделирование вычитающего счетчика в режиме Timing

На рисунке 1.3 представлен результат моделирования в режиме

Functional.

Рисунок 1.3 – Моделирование вычитающего счетчика в режиме Functional

По результатам моделирования можно сделать вывод, что схема выполнена в соответствии с таблицей истинности асинхронного вычитающего счетчика 1.1.

4

1.4 ОПИСАНИЕ С ПОМОЩЬЮ HDL

Ниже представлен код на VHDL:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity asc is

port(C: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR(4 downto 0)); end;

architecture synth of asc is

signal cnt: STD_LOGIC_VECTOR(4 downto 0) := "11101"; begin

Q <= cnt; process(C) begin

if cnt = "11111" then cnt <= "11101"; elsif falling_edge(C) then cnt <= cnt - '1'; end if;

end process; end;

На рисунке 1.4 представлено моделирование асинхронного вычитающего счетчика в режиме Timing.

Рисунок 1.4 – Моделирование вычитающего счетчика в режиме Timing

На рисунке 1.5 представлено моделирование асинхронного

вычитающего счетчика в режиме Functional.

Рисунок 1.5 – Моделирование вычитающего счетчика в режиме Functional

На рисунке 1.6 представлено изображение схемы с помощью RTL

Viewer.

5

Рисунок 1.6 – RTL Viewer представление

6

2 СИНХРОННЫЙ СУММИРУЮЩИЙ СЧЕТЧИК

2.1 ТАБЛИЦА ИСТИННОСТИ

Ниже приведена таблица истинности 2.1 для суммирующего счетчика с

модулем счета 24.

Таблица 2.1 – Таблица истинности вычитающего счетчика

№ |

Выходы |

|

|

|

|

сигнала |

Q4 |

Q3 |

Q2 |

Q1 |

Q0 |

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

0 |

1 |

0 |

3 |

0 |

0 |

0 |

1 |

1 |

4 |

0 |

0 |

1 |

0 |

0 |

5 |

0 |

0 |

1 |

0 |

1 |

6 |

0 |

0 |

1 |

1 |

0 |

7 |

0 |

0 |

1 |

1 |

1 |

8 |

0 |

1 |

0 |

0 |

0 |

9 |

0 |

1 |

0 |

0 |

1 |

10 |

0 |

1 |

0 |

1 |

0 |

11 |

0 |

1 |

0 |

1 |

1 |

12 |

0 |

1 |

1 |

0 |

0 |

13 |

0 |

1 |

1 |

0 |

1 |

14 |

0 |

1 |

1 |

1 |

0 |

15 |

0 |

1 |

1 |

1 |

1 |

16 |

1 |

0 |

0 |

0 |

0 |

17 |

1 |

0 |

0 |

0 |

1 |

18 |

1 |

0 |

0 |

1 |

0 |

19 |

1 |

0 |

0 |

1 |

1 |

20 |

1 |

0 |

1 |

0 |

0 |

21 |

1 |

0 |

1 |

0 |

1 |

22 |

1 |

0 |

1 |

1 |

0 |

23 |

1 |

0 |

1 |

1 |

1 |

24 |

0 |

0 |

0 |

0 |

0 |

2.2 ФУНКЦИОНАЛЬНАЯ СХЕМА

Для данного счетчика необходимо реализовать синхронный сброс и

прием сигнала по нарастающему фронту.

7

На рисунке 2.1 представлена функциональная схема синхронного суммирующего счетчика.

Рисунок 2.1 – Функциональная схема синхронного суммирующего счетчика

2.3 МОДЕЛИРОВАНИЕ

Было выполнено моделирование составленной функциональной схемы из пункта 2.2. На рисунке 2.2 изображен результат моделирования в режиме

Timing.

Рисунок 2.2 – Моделирование суммирующего счетчика в режиме Timing

На рисунке 2.3 представлен результат моделирования в режиме

Functional.

Рисунок 2.3 – Моделирование суммирующего счетчика в режиме Functional

По результатам моделирования можно сделать вывод, что схема выполнена в соответствии с таблицей истинности синхронного суммирующего счетчика 2.1.

8

2.4 ОПИСАНИЕ С ПОМОЩЬЮ HDL

Ниже представлен код на VHDL:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity scn is

port(C: in STD_LOGIC; PR: in STD_LOGIC;

Q: out STD_LOGIC_VECTOR(4 downto 0) );

end;

architecture synth of scn is

signal cnt: STD_LOGIC_VECTOR(4 downto 0) := "00000"; begin

Q <= cnt; process(C) begin

if cnt = "10111" then cnt <= "00000"; elsif rising_edge(C) then

cnt <= cnt + '1'; end if;

if PR = '1' then cnt <= "00000"; end if;

end process; end;

На рисунке 2.4 представлено моделирование синхронного суммирующего счетчика в режиме Timing.

Рисунок 2.4 – Моделирование суммирующего счетчика в режиме Timing

На рисунке 2.5 представлено моделирование асинхронного

вычитающего счетчика в режиме Functional.

Рисунок 2.5 – Моделирование суммирующего счетчика в режиме Functional

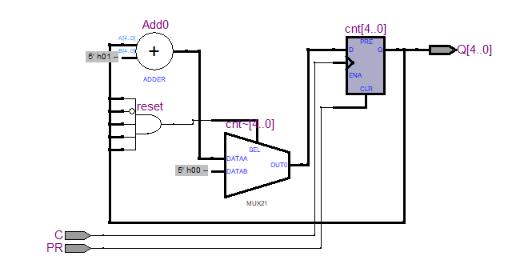

На рисунке 2.6 представлено изображение схемы с помощью RTL

Viewer.

9

Рисунок 2.6 – RTL Viewer представление

10