Отчеты / ЛАБ4

.1.pdfМинистерство образования и науки Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-

вычислительных систем (КИБЭВС)

ИЗУЧЕНИЕ РАБОТЫ ТРИГГЕРОВ

Отчет по лабораторной работе №4

по дисциплине «Электроника и схемотехника 2»

Вариант №5

Выполнил:

Студент гр. 710-2

_______ _____Кузьмина А.А.

__.05.2022

Принял: преподаватель каф. КИБЭВС

_______ А.С. Семенов

__.05.2022

Томск - 2022

2

1 Введение

Цель работы: является изучение основных типов триггеров, их принципы построения и работы.

Задание:

1.Составьте таблицы функционирования для схем из табл. 16 из методички согласно варианту. В таблице подпишите режимы работы триггера;

2.Соберите схемы заданных триггеров согласно варианту;

3.Промоделируйте работу всех схем в двух режимах и исследуйте минимальный порог длительности активного уровня управляющего сигнала.

Проведите анализ результатов моделирования разных режимов;

4.Сверьте результаты моделирования с составленными таблицами функционирования;

5.Повторите п. 2-4, только для описания устройств вместо схем на холстах .bdf используйте заданный вариантом HDL.

Задания по варианту:

1.RS/JK – s2-RS, И-НЕ;

2.T – d, ИЛИ-НЕ;

3.D – s1, ИЛИ-НЕ.

3

2 Ход работы

2.1 Триггер s2-RS с базисом И-НЕ Таблица истинности для триггера представлена ниже.

Таблица 1 – Таблица функционирования для двухступенчатого RS триггера.

|

Входы |

|

|

Выходы |

|

|

|

|

|

|

|

|

|

|

Режим |

R |

S |

C |

Q1(t) |

Q1(t+1) |

Q(t) |

Q(t+1) |

|

|

|

|

|

|

|

|

|

X |

X |

0 |

0/1 |

0/1 |

0/1 |

0/1 |

Хранение |

|

|

|

|

|

|

|

|

0 |

1 |

1 |

X |

1 |

X |

X |

Установка в 1 |

|

|

|

|

|

|

|

|

X |

X |

0 |

1 |

1 |

X |

1 |

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

X |

0 |

X |

X |

Установка в 0 |

|

|

|

|

|

|

|

|

X |

X |

0 |

0 |

0 |

X |

0 |

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

X |

X |

X |

X |

Запрещённый |

|

|

|

|

|

|

|

|

Формулы к базису И-НЕ:

|

|

̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅ |

|||||

Q(t + 4) = S̅(t + 3) ∩ Q̅(t + 3) |

|||||||

|

|

2 |

|

|

|

|

|

̅ |

|

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|||||

Q(t + 4) = R2(t + 3) ∩ Q(t + 3) |

|||||||

̅ |

|

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|||||

(t + 3) |

|

|

|

̅̅̅̅̅̅̅ |

|||

R2 |

= Q1(t + 2) ∩ C(t + 2) |

||||||

|

|

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|||||

S̅(t + 3) |

= Q |

|

|

̅̅̅̅̅̅̅ |

|||

(t + 2) ∩ C(t + 2) |

|||||||

2 |

|

1 |

|

|

|

|

|

|

|

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|||||

Q |

|

|

|

|

̅̅̅̅̅̅̅̅ |

||

(t + 2) = S̅(t + 1) ∩ Q |

(t + 1) |

||||||

1 |

|

|

1 |

|

1 |

|

|

̅̅̅̅̅̅̅̅̅̅̅̅ |

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

||||||

Q1 |

(t + 2) = R1(t + 1) ∩ Q1(t + 1) |

||||||

|

|

̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|||||

S̅(t + 1) |

|

̅ |

|

(t) ∩ C(t) |

|||

= (t) ∩ Q |

|||||||

1 |

|

|

|

1 |

|

|

|

̅ |

|

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ |

|||||

(t + 1) = S(t) ∩ Q1(t) ∩ C(t) |

|||||||

R1 |

|||||||

4

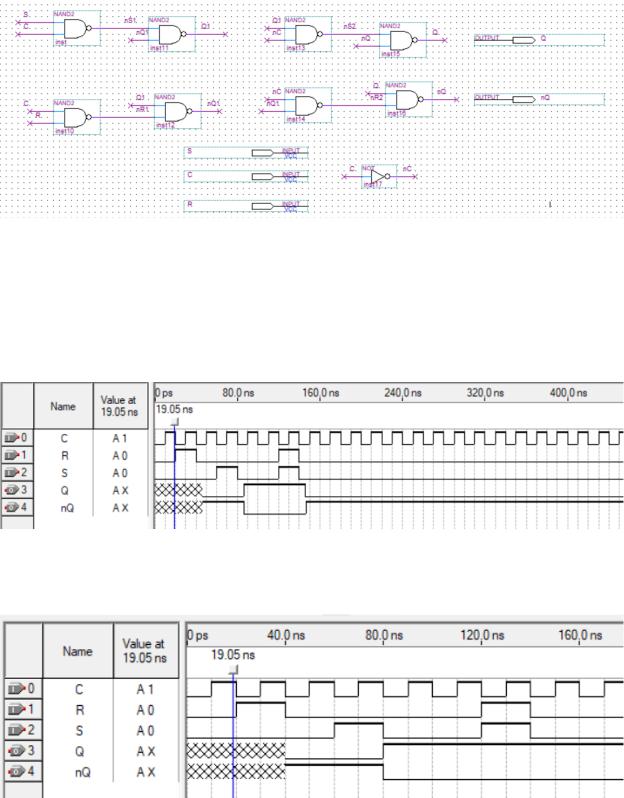

На рисунке 1 изображена схема двухступенчатого RS триггера.

Рисунок 1- Схема двухступенчатого RS триггера.

После построения схемы было проведено моделирование в двух режимах timing и functional. Результаты моделирования представлены на рисунках 2 и 3.

Рисунок 2 – Результат моделирования в режиме timing.

Рисунок 3 – Результат моделирования в режиме function.

5

Был написан код для двухступенчатого RS триггера на VHDL. Код представлен ниже на рисунке 4.

Рисунок 4 – Код на VHDL для двухступенчатого RS триггера.

После компиляции кода было проведено моделирование в двух режимах timing и functional. На рисунках 5 и 6 представлено моделирование в двух режимах.

Рисунок 5 – Результат моделирования в режиме timing.

Рисунок 6 – Результат моделирования в режиме function.

6

2.2 Динамический Т триггер

Таблица истинности для триггера представлена ниже.

Таблица 2 – Таблица функционирования T триггера

Вход |

|

Выход |

|

|

|

|

|

|

Режим |

C |

Q(t) |

|

Q(t+1) |

|

|

|

|||

|

|

|

|

|

0 |

0/1 |

|

0/1 |

Хранение |

|

|

|

|

|

1 |

1 |

|

0 |

Счётный из 1 в 0 |

|

|

|

|

|

1 |

0 |

|

1 |

Счётный из 0 в 1 |

|

|

|

|

|

Формулы для базиса ИЛИ-НЕ

( ) ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

+ 2 = 1( + 1) ( + 1)

̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

( + 2) = ( + 1) 1( + 1)

̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

1( + 1) = 1( + 1) ( + 1)

̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅

1( + 1) = 1( + 1) ( + 1)

̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

2( ) = ( ) 1( + 1)

̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

2( ) = 1( ) ( )

7

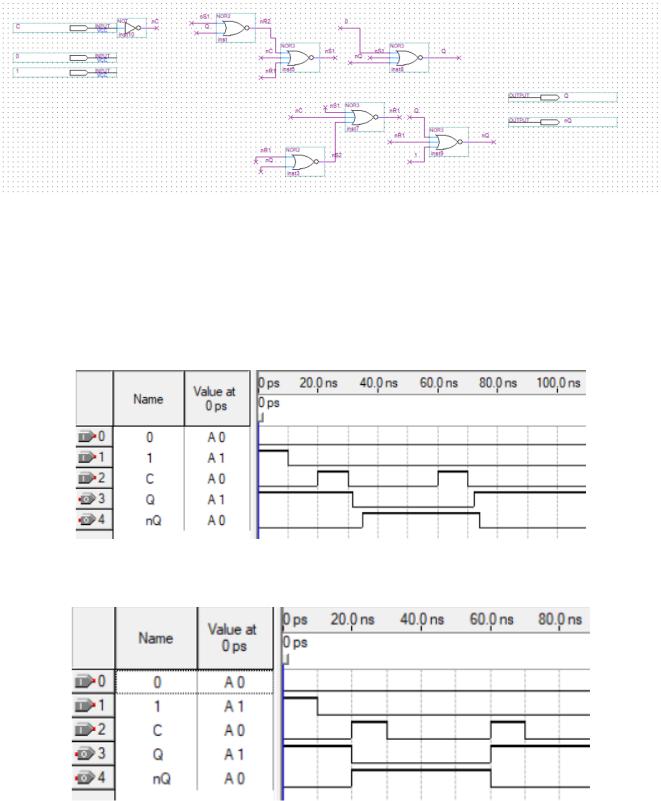

На рисунке 7 изображена схема d-T триггера.

Рисунок 7 – Схема d-T триггера.

После построения схемы было проведено моделирование в двух режимах timing и functional. Результаты моделирования представлены на рисунках 8 и 9.

Рисунок 8 – Результат моделирования в режиме timing.

Рисунок 9 – Результат моделирования в режиме function.

8

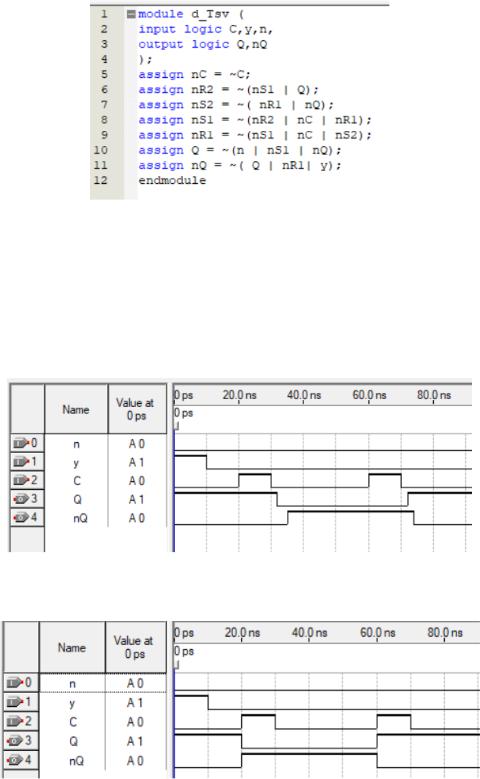

Был написан код для d-T триггера на VHDL. Код представлен ниже на рисунке 10.

Рисунок 10 – Код на VHDL для d-T триггера.

После компиляции кода было проведено моделирование в двух режимах timing и functional. На рисунках 11 и 12 представлено моделирование в двух режимах.

Рисунок 11 – Результат моделирования в режиме timing.

Рисунок 12 – Результат моделирования в режиме function.

9

2.3 s1-D триггер

Таблица истинности для триггера представлена ниже.

Таблица 3 – Таблица функционирования D триггера.

Входы |

|

|

Выходы |

|

||

|

|

|

|

|

|

Режим |

D |

|

C |

Q(t) |

|

Q(t+1) |

|

|

|

|

|

|

|

|

X |

|

0 |

0/1 |

|

0/1 |

Хранение |

|

|

|

|

|

|

|

0 |

|

1 |

X |

|

0 |

Установка в 0 |

|

|

|

|

|

|

|

1 |

|

1 |

X |

|

1 |

Установка в 1 |

|

|

|

|

|

|

|

Формулы для базиса ИЛИ-НЕ:

̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

1( + 1) = ( ) ( )

( ) ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

+ 2 = 1( + 1) ( + 1)

̅̅̅̅̅̅̅̅̅̅̅

( + 2) =

̅̅̅̅̅̅̅̅̅̅̅̅̅

1( + 1) =

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

1( + 1) ( + 1)

̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅

1( ) ( )

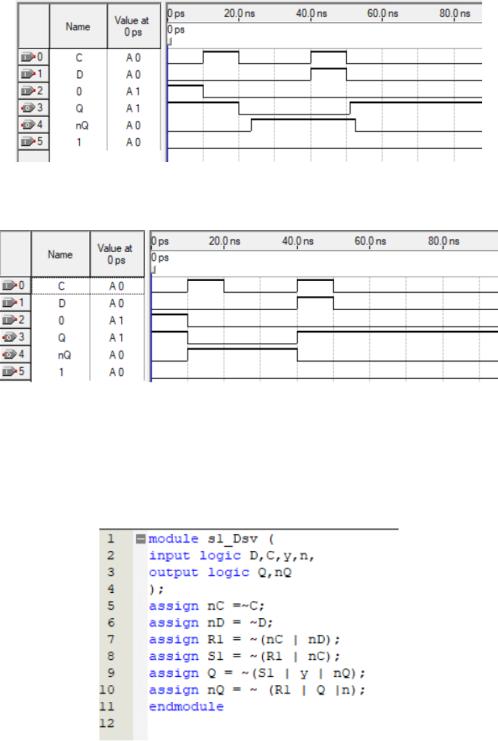

На рисунке 13 изображена схема s1-D триггера.

Рисунок 13 – Схема одноступенчатого D триггера.

10

После построения схемы было проведено моделирование в двух режимах timing и functional. Результаты моделирования представлены на рисунках 14 и 15.

Рисунок 14 – Результат моделирования в режиме timing.

Рисунок 15 – Результат моделирования в режиме function.

Был написан код для одноступенчатого D триггера на VHDL. Код представлен ниже на рисунке 16.

Рисунок 16 – Код на VHDL для одноступенчатого D триггера.