- •Методические указания

- •1. Лабораторная работа № 1 проектирование функциональных узлов комбинационного типа на языке vhdl

- •1.1. Общие указания по выполнению лабораторной работы

- •1.2. Домашние задания и методические указания по их выполнению

- •1.3. Вопросы к домашнему заданию

- •1.4. Лабораторные задания и методические указания по их выполнению

- •1.5. Контрольные вопросы

- •2. Лабораторная работа № 2 проектирование иерархических модулей на языке vhdl

- •2.1. Общие указания по выполнению лабораторной работы

- •2.2. Домашние задания и методические указания по их выполнению

- •2.3. Вопросы к домашнему заданию

- •2.4. Лабораторные задания и методические указания по их выполнению

- •2.5. Контрольные вопросы

- •3. Лабораторная работа № 3 проектирование компаратора кода с использованием иерархических модулей и многоразрядных шин данных на языке vhdl

- •3.1. Общие указания по выполнению лабораторной работы

- •3.2. Домашние задания и методические указания по их выполнению

- •3.3. Вопросы к домашнему заданию

- •3.4. Лабораторные задания и методические указания по их выполнению

- •3.5. Контрольные вопросы

- •4. Лабораторная работа № 4 проектирование структуры оперативного запоминающего устройства статического типа на языке vhdl

- •4.1. Общие указания по выполнению лабораторной работы

- •4.2. Домашние задания и методические указания по их выполнению

- •4.3. Вопросы к домашнему заданию

- •4.4. Лабораторные задания и методические указания по их выполнению

- •4.5. Контрольные вопросы

- •Указания по оформлению отчёта

- •Библиографический список

- •Содержание

- •394026 Воронеж, Московский просп., 14

4.3. Вопросы к домашнему заданию

1.3.1. Перечислить основные типы и параметры ЗУ.

1.3.2. Статические ОЗУ и их классификация.

1.3.3. Какие основные структуры запоминающих устройств вы знаете?

4.4. Лабораторные задания и методические указания по их выполнению

Задание 1. На завершающем этапе лабораторного практикума осуществляется построение модели адресного ОЗУ статического типа. Студенты должны построить, отладить и продемонстрировать работоспособность модели ОЗУ на логическом уровне используя полученные в ходе лабораторных работ модели отдельных ее модулей, опираясь на пример приведенный в домашнем задании.

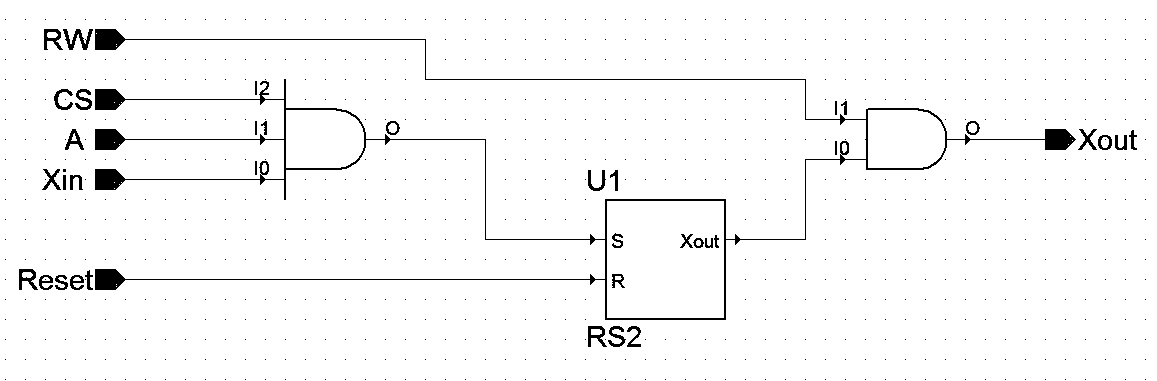

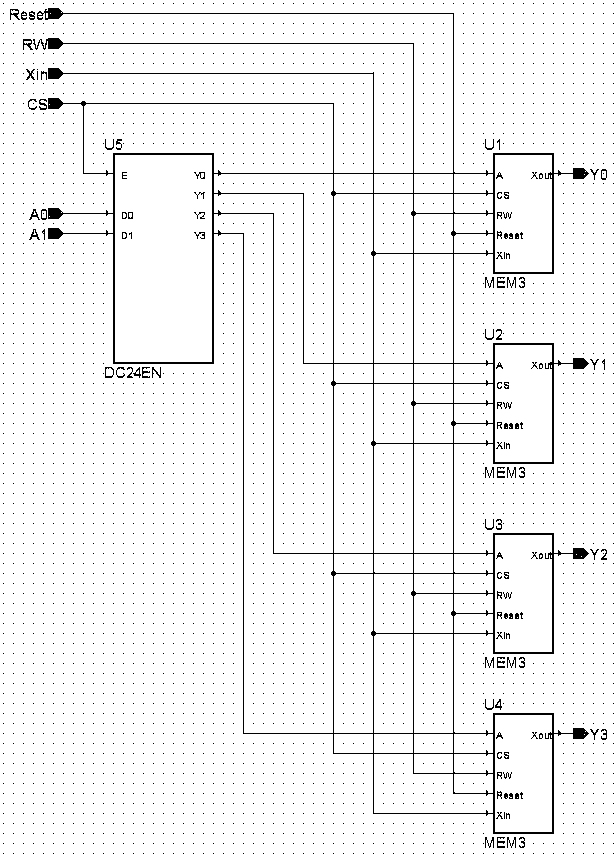

В первом задании необходимо реализовать модель ОЗУ статического типа построенного по схеме однокоординатной выборки (см. рис. 24). Для решения данной задачи используется запоминающая ячейка с одним адресным входом (см. рис. 23).

Рис. 23. Запоминающая ячейка ОЗУ статического типа с однокоррдинатной выборкой

В качестве дешифратора адреса используется построенный ранее дешифратор «2-4» с разрешающим входом «E». Спроектированную ячейку проверить на работоспособность, последовательно выполняя итерации, приведенные в таблице ниже.

Порядок работы запоминающей ячейки

Вход |

Итерация 1 |

Итерация 2 |

Итерация 3 |

Итерация 4 |

Итерация 5 |

Итерация 6 |

Reset |

1 |

0 |

0 |

0 |

1 |

0 |

RW |

0 |

1 |

0 |

1 |

0 |

1 |

CS |

0 |

0 |

1 |

0 |

0 |

0 |

A |

0 |

0 |

1 |

0 |

0 |

0 |

Xin |

0 |

0 |

1 |

0 |

0 |

0 |

|

Сброс ячейки |

Режим чтения |

Режим записи |

Режим чтения |

Сброс ячейки |

Режим чтения |

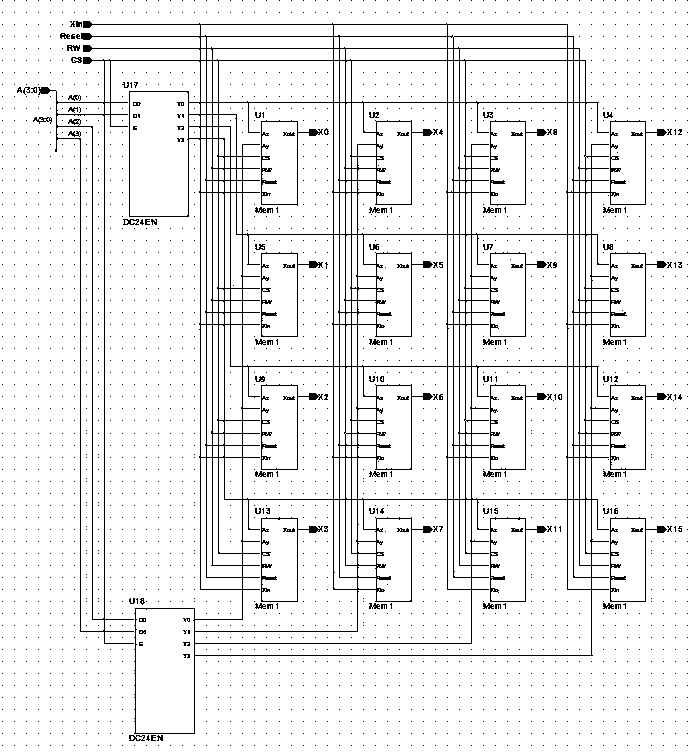

Задание 2. Опираясь на схему двухкоординатной выборки, представленной в домашнем задании, необходимо построить модель с использованием 16 запоминающих ячеек (см. рис. 25). Ячейки памяти в данном случае будут соответствовать схеме рис. 22 и иметь два адресных входа.

Рис. 24. Схема ОЗУ статического типа на 4 запоминающие ячейки

В качестве двух дешифраторов адреса используется построенные ранее дешифраторы «2-4» с разрешающим входом «E». Полученные модели ОЗУ необходимо откомпилировать и проверить их работоспособность. Реализовать циклы запись/чтение запоминающих ячеек в соответствии со следующими итерациями: Сброс (RESET), включение схемы (CS), адресная запись 1 бита информации в каждую ячейку памяти, адресное считывание данных, сброс ячеек (RESET).

Рис. 25. Схема ОЗУ статического типа на 16 запоминающих ячеек

4.5. Контрольные вопросы

1.5.1. Какова цель лабораторной работы?

1.5.2. В чем заключается лабораторное задание? Пояснить ход его выполнения.

1.5.3. Какие данные являлись исходными для выполнения работы?

1.5.4. Пояснить работу полученных моделей ОЗУ, продемонстрировать запись/чтение данных.

1.5.5. Сформулируйте выводы по данной лабораторной работе.