- •Введение

- •1. Методология проектирования

- •2. Техническое задание для проектирования Интегральных схем

- •3. Этапы выполнения опытно-конструкторской работы

- •4. Технические условия

- •5. Проектирование

- •6. Типовой комплект разработки

- •6.1. Основные функции pdk

- •6.2. Геометрические термины топологии в pdk

- •7. Состав pdk

- •8. Правила проектирования

- •9. Контрольные вопросы

- •Заключение

- •Библиографический список

- •Оглавление

- •394026 Воронеж, Московский просп., 14

ФГБОУ ВПО

«Воронежский государственный технический университет»

Ю.С. Балашов И.А. Сафонов

Методология проектирования

аналоговых устройств сверхбольших

интегральных схем

Утверждено Редакционно-издательским советом

университета в качестве учебного пособия

Воронеж 2011

УДК 621.396.6

Балашов Ю.С. Методология проектирования аналоговых устройств сверхбольших интегральных схем: учеб. пособие. / Ю.С. Балашов, И.А. Сафонов. Воронеж: ФГБОУ ВПО «Воронежский государственный технический университет», 2011. 80 с.

В учебном пособии рассматривается методология проектирования сложных заказных сверхбольших интегральных схем (СБИС), объединяющая два подхода проектирования («снизу-вверх» и «сверху-вниз»), взяв от первого доступ к точной информации о реализации компонентов схемы на кристалле, а от второго – эффективность и возможность высокоуровневой верификации. Также рассмотрены этапы проектирования и влияние технологического процесса на схемотехническое проектирование. Даны правила проектирования КМОП цифровых устройств и правила проектирования цифровых блоков ввода/вывода, а также правила электрических параметров КМОП цифровых устройств.

Издание соответствует требованиям Федерального государственного образовательного стандарта высшего профессионального образования по направлению 211000 «Конструирование и технология электронных средств», магистерской программе 211000.68 «Информационные технологии проектирования электронных средств, выполненных по субмикронной технологии», дисциплине «Методология проектирования аналоговых устройств сверхбольших интегральных схем». Учебное пособие также предназначено для слушателей профессиональной переподготовки специалистов (программа «Схемотехническое проектирование аналоговых устройств сверхбольших интегральных схем (СБИС) с топологическими нормами 90 нм»).

Предназначено студентам очной формы обучения.

Учебное пособие подготовлено в электронном виде в текстовом редакторе MS Word XP и содежится в файле Сафонов Уч.пособ.doc.

Ил. 7., табл.2. Библиогр.: 7 назв.

Рецензенты: ОАО «Концерн Созвездие» (директор

Центра системного проектирования В.И. Конопкин);

канд. техн. наук, проф. Б.В. Матвеев

© Балашов Ю.С., Сафонов И.А., 2011

© Оформление. ФГБОУ ВПО «Воронежский

государственный технический университет», 2011

Введение

Схемотехническое проектирование аналоговых устройств в топологическом базисе 90 нм и меньше представляет собой сложную инженерную задачу, требующую системного подхода, и определенной методологии. Проектирование начинается с определения требований к устройству, формировании системной модели, схемотехническому проектированию и моделированию, разработки топологии и верификации. Все эти этапы представлены в маршруте проектирования СБИС, которые поддерживают современные САПР, такие как Cadence IC, платформа Virtuose.

В основе методологии проектирования аналоговых устройств лежат: маршрут проектирования, комплект разработчика (PDK - Process Design Kit), среда или платформа проектирования. Традиционно, первой методологией проектирования «снизу-вверх», при которой сначала создаются низкоуровневые ячейки, потом блоки и схемы, которые в конечном счете объединяются в целый кристалл. Впоследствии, когда сложность разработок возросла, стал активно развиваться методология «сверху-вниз», при котором проект начинается с создания полной поведенческой модели системы. Связано это с тем, что процесс проектирования снизу-вверх, хотя и обеспечивает возможность учета всех особенностей реализации компонентов схемы на кристалле,- слишком медленный. К тому же в больших проектах на стадии разработок ячеек трудно предвидеть проблемы общесистемного уровня. При проектировании заказных СБИС предпочтительно объединять обе эти методологии, взяв от первого доступ к точной информации о реализации компонентов схемы на кристалле, а от второго – эффективность и возможность высокоуровневой верификации. Проектирование должно идти одновременно сверху-вниз и снизу-вверх так, чтобы в промежуточной точке, когда оба этих процесса состыкуются, получился оптимальный результат. Такая «meet-in-the-middle» методология представляется наиболее разумной и перспективной при проектировании.

PDK для проектирования содержит в себе формализованное для разработки описание технологического процесса, интегрированного в среду проектирования. Это описание представлено в виде технологических библиотек, шаблонов, описаний слоев, устройств и их моделей, правил проектирования и верификации.

1. Методология проектирования

Существующие системы автоматизированного проектирования заказных СБИС формировались в рамках традиционных методологий проектирования. Изначально в них поддерживалась методология проектирования «снизу-вверх», при которой сначала создаются низкоуровневые ячейки, потом блоки и схемы, которые, в конечном счете, объединяются в целый кристалл. Впоследствии, когда сложность разработок возросла, стал активно развиваться подход «сверху-вниз», при котором проект начинается с создания полной поведенческой модели системы. Связано это с тем, что процесс проектирования снизу-вверх, хотя и обеспечивает возможность учета всех особенностей реализации компонентов схемы на кристалле,- слишком медленный. К тому же в больших проектах на стадии разработок ячеек трудно предвидеть проблемы общесистемного уровня. В то же время при работе сверху-вниз более-менее точная информация о конкретной реализации компонентов схемы часто появляется слишком поздно. Такой подход вполне приемлем для чисто цифровых устройств, но для сложных заказных схем, в силу влияния физических эффектов (например, электромиграция, шумы, индуктивность и т.д.), на последней стадии может оказаться, что проект полностью неработоспособен.

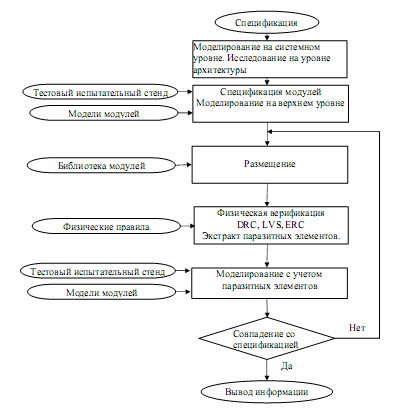

При проектировании заказных СБИС предпочтительно объединять оба подхода, взяв от первого доступ к точной информации о реализации компонентов схемы на кристалле, а от второго – эффективность и возможность высокоуровневой верификации. Проектирование должно идти одновременно сверху-вниз и снизу-вверх так, чтобы в промежуточной точке, когда оба этих процесса состыкуются, получился оптимальный результат. Такая «meet-in-the-middle» методология представляется наиболее разумной и перспективной при проектировании современных заказных систем на кристалле. Иллюстрация этого подхода представлена на рис. 1.1.

Рис. 1.1. Методология проектирования

Топология СБИС – множество геометрических фигур, расположенных в различных топологических слоях. Топологические слои объединяют фигуры, которые будут перенесены на один фотошаблон. Некоторое множество фигур в одном или в нескольких топологических слоях объединяются в топологическую группу. Топологическая группа кроме геометрических фигур может содержать в себе ссылки на другие группы, формируя иерархическое описание топологии. Топологическая группа может включать фигуры (примитивы) следующих типов: ортогональный прямоугольник, многоугольник, шина, текст, линия и т.д. Примитивы первых трёх типов имеют замкнутый контур и формируют рисунок на фотошаблоне. Примитивы типа текст и линия рисунка на фотошаблоне не формируют, они предназначены для создания поясняющих надписей и рисунков в топологии. Привязки групп могут быть двух типов – ячейки и итерации. Ячейка описывает единичную ссылку на группу. Итерация обеспечивает множественное обращение к ссылаемой группе в виде матрицы с заданным шагом и количеством повторений по осям координат. Топологическая группа имеет уникальное имя, каждый топологический слой имеет номер. Топологический чертёж является связующим звеном между проектировщиком и изготовителем СБИС.

Проектирование

топологии – процесс преобразования

электрической или логической схемы в

описание послойной реализации схемных

компонентов (транзисторов, диодов,

резисторов) и связей между ними в

многослойной

Верификация топологии включает в себя контроль проектных норм, экстракцию (восстановление) электрической схемы из описания топологии, сравнение с исходной схемой и средства анализа найденных нарушений. Для воплощения схемотехнического решения в кремний требуется редактор топологии, средства размещения и трассировки блоков, контроль геометрических (DRC) и электрических (ERC) проектных норм, сравнение топологической реализации схемы с её исходным описанием (LVS). Топологический редактор позволяет либо непосредственно строить топологию, либо формировать её из стандартных ячеек, содержащихся в библиотеке. Используя базу данных, редактор позволяет редактировать топологию ячеек в соответствии с конкретными требованиями. После разработки топологии отдельных фрагментов с помощью соответствующей программы в диалоговом режиме осуществляется их размещение и трассировка межсоединений. После ввода описания топологии осуществляется ее верификация. Программа контроля проектных норм работает непосредственно с топологией. Контроль осуществляется автоматически по значениям КТТ (DRC-контроль) для используемой технологии (проверочный файл предоставляется заводом-изготовителем). Любые нарушения ограничений помечаются непосредственно на изображении топологии, выводимом на экран дисплея. После завершения DRC-контроля программа восстановления электрической схемы (LVS) преобразует описание топологии в описание электрической схемы в виде таблицы цепей (например, текстовое описание в Spice-формате). Эта таблица передаётся в блок верификации логических и электрических схем, где проводится перекрёстная проверка описанной схемы на логическом и топологическом уровнях, а также повторное моделирование и верификация временных параметров. Таблица передаётся в программу контроля электрических проектных норм (ERC-контроль). Эта программа дополнительно использует ещё и значения параметров транзисторов, полученные при восстановлении электрической схемы из топологии. В результате её работы идентифицируются все нераспознанные или неправильно соединённые элементы, а также все нарушения электрических проектных норм. Конечная информация (топология кристалла) записывается в формате GDSII и передаётся на завод-изготовитель (фабрику). Завод изготавливает набор физических шаблонов и воплощает изделие в кремнии на своём оборудовании. Ответственность за функциональные характеристики СБИС полностью лежит на разработчике, в то время как завод гарантирует качество технологического процесса.

Основным понятием, на которое опирается методология проектирования, является маршрут проектирования, который в свою очередь, базируется на предоставляемых разработчику средствах проектирования.

Компания Cadence Design Systems, Inc поставляет сквозные интегрированные маршруты проектирования аналоговых, цифровых и аналого-цифровых СБИС.

В состав маршрута в зависимости от проекта входят: IC614, VSE-L, VSE-XL, ADE-L, ADE-XL, VLS-L, VLS-XL, VLS-GXL, FINALE71, IUS81, MMSIM70, ASSURA32, EXT71, ANLS71, SOC71.

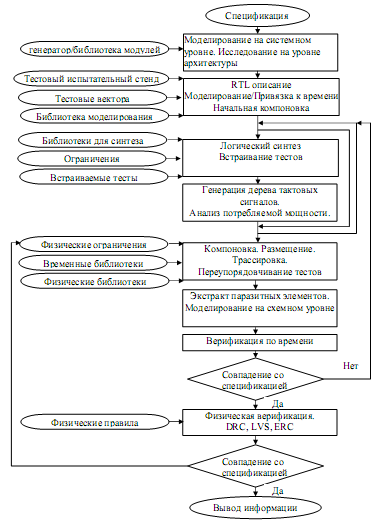

Основные этапы разработки, представленные на рис. 1.1, 1.2:

1. Спецификация проекта, моделирование на системном уровне (поведенческое моделирование).

2. Формирование библиотеки проекта и правил проектирования

3. Разработка схемы или ее синтез для цифровых УБИС, совместно с схемотехническим или логическим моделированием.

4. Топологическое проектирование

5. Экстракция паразитных параметров и верификация

6. Подготовка к производству.

Для разработки СБИС под конкретную технологию с необходимыми правилами проектирования применяются комплекты разработки (PDK), содержащие в себе формализованное для разработки описание технологического процесса, интегрированного в среду проектирования. Это описание представлено в виде технологических библиотек, шаблонов, описаний слоев, устройств и их моделей, правил проектирования и верификации. Их применение позволяет при проектировании учитывать все технологические особенности производства.

Рис. 1.2. Методология проектирования аналоговых УБИС

Рис. 1.3. Методология проектирования цифровых СБИС