МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

«ВОРОНЕЖСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ»

(ФГБОУ ВПО «ВГТУ», ВГТУ)

Кафедра «Радиоэлектронные устройства и системы»

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

к лабораторным работам № 1-3

по дисциплине «Физическая верификация топологии и характеризация аналоговых устройств УБИС»

Воронеж 2011

Составители д-р физ.-мат.наук, проф. Ю.С.Балашов, аспирант Д.В.Шеховцов

УДК 621.396.66

Методические указания к лабораторной работе № 1 по дисциплине «Физическая верификация топологии и характеризация аналоговых устройств УБИС»/ Воронеж. гос.техн.ун-т; сост. Ю.С.Балашов, Д.В.Шеховцов. Воронеж, 2011. 33 с.

Лабораторные работы предназначены для освоения программ Diva, Calibre, Assura предназначенных для проведения полного цикла физической верификации, получения навыков настройки и работы со средой верификации, овладение полным циклом физической верификации в программах Diva, Calibre, Assura. Тематика лабораторных работ соответствует рабочей программе дисциплины «Физическая верификация топологии и характеризация аналоговых устройств УБИС».

Методические указания напечатаны в электронном виде в текстовом редакторе Word for Windows и содержаться в файле «Шеховцов Л.р. № 1.doc», объем файла 2,44 МБ.

Ил.6. Библиог.: 4 назв.

Рецензент канд.техн.наук, доц. Е.Д.Алперин.

Ответственный за выпуск зав.кафедрой д-р физ.-мат.наук, проф. Ю.С.Балашов

Издается по решению редакционно-издательского совета Воронежского государственного технического университета.

© Воронежский государственный технический университет, 2011.

Лабораторная работа № 1

«Физическая верификация и характеризация топологии аналоговых устройств в программе Diva»

1. общие указания

1.1. Цели работы

Ознакомление с программой физической верификации Diva, получение навыков настройки и работы со средой верификации, овладение полным циклом физической верификации в программе Diva.

1.2. Краткие теоретические сведения

Diva – это программный инструмент, предназначенный для проведения полного цикла физической верификации, как отдельных блоков, так и ИС любого размера, независимо от типа технологии, и извлечения из топологии списка соединений с паразитными элементами.

2. Домашние задания и методические указания по их выполнению

Методические указания по выполнению первого задания

1. Проверка норм проектирования и исправление ошибок

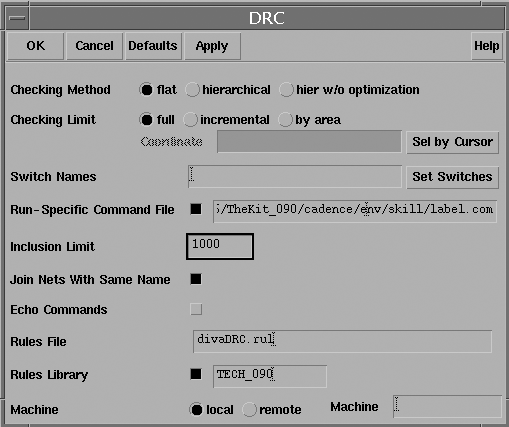

Для запуска приложения Diva DRC, предназначенного для проверки проектных норм, необходимо вызвать процесс в меню редактора топологии Virtuoso «Verify/DRC». В результате выполнения команды на экран выводится интерфейс, показанный на рисунке 1.

Перед запуском процесса проверки не обходимо указать место расположения управляющего файла проверки и его название

Также доступны следующие дополнительные настройки:

- Checking Method – метод проверки;

- Checking Limit - зона проверки;

- Join Nets With Same Name – соединение одноименных шин.

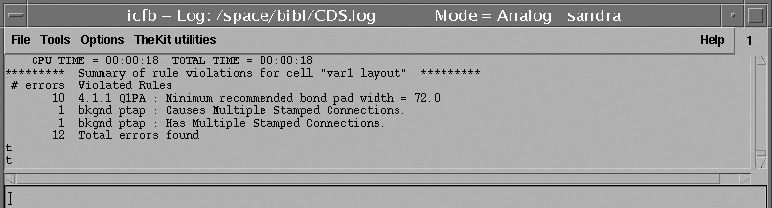

После завершения проверки проектных норм в окне icfb будет выведена информация о найденных ошибках в формате, показанном на рисунке 1.5.3.1.2.

Рис. 1. Интерфейс программы Diva DRC

Рис. 2. Сведения об обнаруженных ошибках КТТ

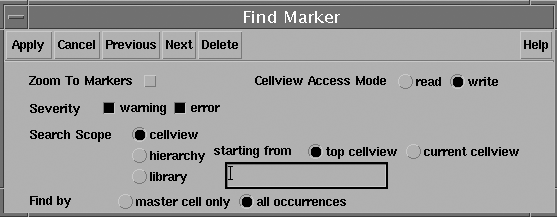

Для просмотра ошибок необходимо запустить интерфейс поиска ошибок, выбрав в меню команду «Verify/Marker/Find…». При выполнении команды откроется окно Find Marker, показанное на рис.3.

Основные установки, необходимые для просмотра и исправления ошибок:

- Zoom To Marker – увеличение места ошибки до размера экрана;

- Severity – выбор варианта просмотра (ошибки, предупреждения);

- Search Scope – границы поиска ошибок: cellview – в ячейке, hierarchy – иерархический поиск, library – в указанной библиотеке;

- Find by – поиск в: master cell only – только в верхней ячейке, all occurrences – во всех ячейках.

Рис. 3. Окно поиска ошибок Find Marker

После того как все настройки определены: при нажатии на кнопку «Next» будет осуществлен переход к месту следующей ошибки, при нажатии на кнопку «Previous» будет осуществлен переход к предыдущей ошибке. Сразу же после нахождения места первой ошибки открывается окно marker text, в котором будут указаны в текстовом виде:

- location: (библиотека, название ячейки, тип представления) – место нахождения ошибки;

- reason: правило – нарушенное правило.

При переходе к следующим ошибкам в окне marker text будут добавляться новые сведения об ошибках. После исправления ошибок процесс проверки производят до полного устранения всех ошибок.

2. Экстракция электрической схемы.

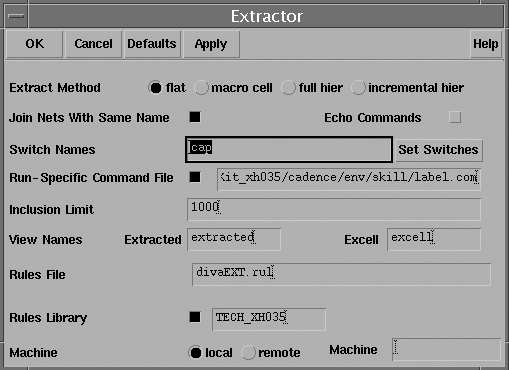

Для осуществления верификации необходимо извлечь электрическую схему из разработанной топологии. Экстракция выполняется с помощью приложения Diva EXT. Запуск приложения выполняется из меню «Verify/Extract».

Основные настройки программы-экстрактора:

- Extract Method – метод экстракции;

- Join Nets With Same Name – соединение одноименных сетей;

- Switch Names – переключатель, устанавливается в случаях, когда требуется отключение отдельных правил экстракции;

- Rules File – управляющий файл экстракции divaEXT.rul;

- Rules Library – техническая библиотека.

Экстракция запускается с помощью нажатия на кнопки «Ok» или «Apply».

После выполнения экстракции в рабочем каталоге появляется представление ячейки extracted, содержащее топологию с наложенной на нее электрической схемой.

Рис. 4. Окно экстракции приложения Diva Extractor

3. Верификация

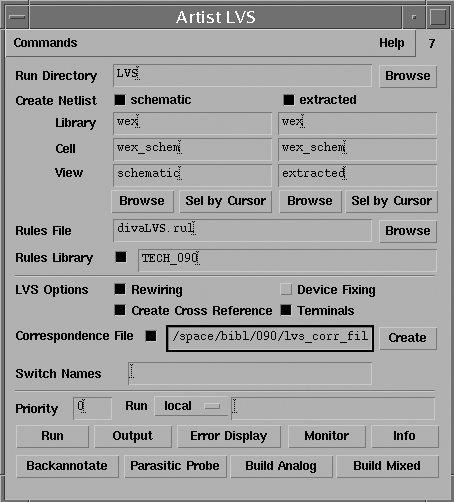

Для осуществления верификации топологии и электрической схемы в программе Diva, необходимо вызвать процесс «Verify/LVS…» в меню редактора топологии Virtuoso. В результате выполнения команды на экран выводится интерфейс, показанный на рисунке 5.

Основные настройки программы верификации Diva LVS:

- Run Directory – рабочая директория процесса верификации;

- Create Netlist – создание нетлиста из схемы и экстракта;

- Rules File – управляющий файл верификации divaLVS.rul;

- Rules Library – техническая библиотека;

- LVS Options – дополнительные опции LVS.

- Кнопки: Run – запуск процесса верификации, Output – отчет верификации, Error Display – запуск дисплея-указателя обнаруженных ошибок.

Рис. 5. Окно программы верификации Diva LVS

Рис. 6. Окно поиска ошибок Probe

Поиск обнаруженных ошибок осуществляется с помощью приложения Diva Probing, запускаемого из меню «Verify/Probe…».

4. Содержимое окна Probing:

4.1. Probing Method – метод поиска ошибок:

- single w/o parasitics – выделение ошибки только в выбранном окне без паразитных элементов;

- single probe matched – выделение прошедших проверку сетей в выбранном окне;

- single probe all – выделение всех сетей в выбранном окне;

- cross probe matched – выделение сопоставленных сетей одновременно в окне схемы и окне экстракта;

- single probe unmatched – выделение ошибочных сетей в одном окне;

4.2. Клавиши: Add Dev – подсветить прибор; Remove Dev – снять выделение прибора, Add Net – выделить сеть, Remove Net – снять выделение с сети, Add Nets for Dev – выделить сети, подключенные к прибору, Remove Nets for Dev – снять выделение с сетей, подключенных к прибору, Add Devs for Net – выделить приборы, подключенные к сети, Remove Devs for Net – снять выделение с приборов, подключенных к сети, Remove All – снять выделение со всех приборов и сетей.

Программа Diva LVS выводит отчет о завершении процесса верификации в котором подробно указаны:

- данные по приборам;

- данные по сетям;

- данные по терминалам;

Указываемые данные по сетям и приборам:

- не сопоставленные;

- прошедшие перестановку симметричные выводы;

- ошибочные размеры сопоставленных приборов;

- общее количество ошибочных сетей и приборов.

После нажатия соответствующей кнопки следует указать требуемую сеть или прибор, например, в схеме. В случае нахождения соответствия между электрической схемой и экстрактом выделится соответствующая сеть в экстракте, если сеть не была сопоставлена – она не будет выделена. Выделяя, таким образом, входы, выходы, приборы и сети находят среди них соответствующие друг другу, анализируя и сопоставляя схему и топологию не сопоставленных сетей и приборов, находят ошибки проектирования.

После исправления найденных ошибок производят повторный запуск процесса верификации до полного устранения всех ошибок.