- •Автоматизация измерений, контроля и испытаний

- •Введение. Основные определения и термины

- •1. Принципы построения измерительных систем

- •1.1. Ввод аналоговых сигналов в измерительных системах

- •1.1.1. Датчики измерительных систем и устройства согласования

- •1.1.2. Измерительные коммутаторы

- •1.1.3. Аналого-цифровые и цифро-аналоговые преобразователи

- •1.2. Оценка системных параметров многоканальных измерительных систем

- •1.3. Каналы передачи данных (интерфейс)

- •1.4. Устройства и системы ввода/вывода фирмы National Instruments

- •1.4.1. Системы согласования сигналов scxi и scc

- •1.4.2. Многофункциональные платы и устройства для сбора данных

- •1.4.3. Модульные измерительные системы стандарта pxi

- •1.4.4. Система распределенного ввода/вывода и промышленного управления FieldPoint

- •1.4.5. Реконфигурируемая контрольно-измерительная система CompactRio

- •1.5. Система дистанционного измерения и сбора измерительно-диагностической информации

- •1.5.1. Общая структура системы

- •1.5.2. Измерительная часть автоматизированной системы дистанционных измерений

- •1.5.3. Алгоритмы работы автоматизированной системы дистанционных измерений

- •1.5.4. Разработка схем подключения средств измерения

- •2. Сигналы и методы их исследования

- •2.1. Общие характеристики электрических сигналов

- •2.2. Методы исследования прохождения сигналов

- •2.3. Динамические модели преобразователей сигналов

- •2.4. Механические, тепловые и электрические аналогии

- •2.4.1. Механические элементы

- •2.4.2. Тепловые элементы

- •2.4.3. Электрические элементы

- •2.5. Фильтры

- •2.5.1. Фильтры нижних частот

- •2.5.2. Фильтры верхних частот

- •2.5.3. Полосовые фильтры

- •2.5.4. Полосно-подавляющие фильтры

- •3. Аналоговая обработка сигналов

- •3.1. Операционные усилители. Основные свойства

- •3.2. Параметры и характеристики оу

- •3.3. Обратная связь в усилителях

- •3.4. Влияние ос на параметры усилителей

- •3.5. Применение операционных усилителей

- •3.5.1. Инвертирующий усилитель

- •3.5.2. Неинвертирующий усилитель

- •3.5.3. Суммирующий усилитель

- •3.5.4. Дифференциальный усилитель

- •3.5.5. Измерительный усилитель

- •3.5.6. Интеграторы

- •3.5.7. Дифференциаторы

- •3.5.8. Нелинейные преобразователи на оу

- •3.6. Активные фильтры

- •4. Цифро-аналоговые и аналого-цифровые преобразователи

- •4.1. Электронные ключи и коммутаторы

- •4.2. Цифро-аналоговые преобразователи

- •4.2.1. Общие положения

- •4.2.2. Цап с суммированием токов

- •4.2.3. Цап с внутренними источниками тока

- •4.2.4. Сегментированные цап

- •4.4.5. Цифровые потенциометры

- •4.2.6. Цап прямого цифрового синтеза

- •4.2.7. Параметры цап

- •4.3. Аналого-цифровые преобразователи

- •4.3.1. Общие положения

- •4.3.3. Ацп последовательного приближения

- •4.3.4. Последовательно-параллельные ацп конвейерного типа

- •4.3.5. Сигма-дельта ацп

- •5. Цифровая обработка сигналов

- •5.1. Общая характеристика цифровых сигналов и цифровых микросхем

- •5.2. Основы алгебры логики

- •5.3. Логические элементы

- •5.3.1. Типы логических элементов

- •5.3.2. Параметры логических элементов

- •5.4. Построение комбинационной логической схемы по заданной функции. Минимизация логических функций

- •5.5. Типы выходных каскадов цифровых элементов

- •5.6. Сложные логические элементы

- •6. Функциональные устройства на цифровых микросхемах

- •6.1. Системы счисления

- •6.2. Дешифраторы и шифраторы

- •6.3. Мультиплексоры и демультиплексоры

- •6.4. Компараторы кодов

- •6.5. Сумматоры

- •6.6. Триггеры

- •6.7. Регистры

- •6.8. Счетчики импульсов

- •6.9. Автоматизированные измерительные системы

- •Заключение

- •Библиографический список

- •394026 Воронеж, Московский просп., 14

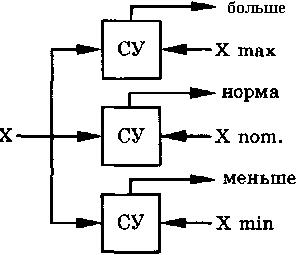

6.4. Компараторы кодов

Рис. 6.22. Принцип сравнения двух величин

(«больше», «меньше», «равно»)

Рис.

6.23. 4-х разрядный компаратор кодов СП1

![]()

Микросхемы компараторов кодов (англ. Comparator) применяют для сравнения двух входных кодов и выдачи на выходы сигналов о результатах этого сравнения (о равенстве или неравенстве кодов). На схемах компараторы кодов обозначаются двумя символами равенства: «= =». Код типа микросхемы компаратора кода в отечественных сериях — СП.

Примером такой микросхемы может служить СП1 — 4-х разрядный компаратор кодов, сравнивающий величины кодов и выдающий информацию о том, какой код больше, или о равенстве кодов (рис. 6.23).

Таблица 6.8 Таблица

истинности компаратора СП1

Входы сравниваемых

кодов

Входы наращивания

Выходы

A3, B3

A2, B2

A1, B1

A0, B0

A>B

A<B

A=B

A>B

A<B

A=B

A3>B3

×

×

×

×

×

×

1

0

0

A3<B3

×

×

×

×

×

×

0

1

0

A3=B3

A2>B2

×

×

×

×

×

1

0

0

A3=B3

A2<B2

×

×

×

×

×

0

1

0

A3=B3

A2=B2

A1>B1

×

×

×

×

1

0

0

A3=B3

A2=B2

A1<B1

×

×

×

×

0

1

0

A3=B3

A2=B2

A1=B1

A0>B0

×

×

×

1

0

0

A3=B3

A2=B2

A1=B1

A0<B0

×

×

×

0

1

0

A3=B3

A2=B2

A1=B1

A0=B0

1

0

0

1

0

0

A3=B3

A2=B2

A1=B1

A0=B0

0

1

0

0

1

0

A3=B3

A2=B2

A1=B1

A0=B0

×

×

1

0

0

1

A3=B3

A2=B2

A1=B1

A0=B0

1

1

0

0

0

0

A3=B3

A2=B2

A1=B1

A0=B0

0

0

0

1

1

0

Рис. 6.24. Каскадирование

компараторов кодов

Если используется одиночная микросхема, то для ее правильной работы достаточно подать единицу на вход A=B, а состояния входов A<B и A>B не важны, на них можно подать как нуль, так и единицу. Назначение выходов понятно из их названия, а полярность выходных сигналов положительная (активный уровень — единица). Если микросхемы компараторов кодов каскадируются (объединяются) для увеличения числа разрядов сравниваемых кодов, то надо выходные сигналы микросхемы, обрабатывающей младшие разряды кода, подать на одноименные входы микросхемы, обрабатывающей старшие разряды кода (рис. 6.24).