- •Автоматизация измерений, контроля и испытаний

- •Введение. Основные определения и термины

- •1. Принципы построения измерительных систем

- •1.1. Ввод аналоговых сигналов в измерительных системах

- •1.1.1. Датчики измерительных систем и устройства согласования

- •1.1.2. Измерительные коммутаторы

- •1.1.3. Аналого-цифровые и цифро-аналоговые преобразователи

- •1.2. Оценка системных параметров многоканальных измерительных систем

- •1.3. Каналы передачи данных (интерфейс)

- •1.4. Устройства и системы ввода/вывода фирмы National Instruments

- •1.4.1. Системы согласования сигналов scxi и scc

- •1.4.2. Многофункциональные платы и устройства для сбора данных

- •1.4.3. Модульные измерительные системы стандарта pxi

- •1.4.4. Система распределенного ввода/вывода и промышленного управления FieldPoint

- •1.4.5. Реконфигурируемая контрольно-измерительная система CompactRio

- •1.5. Система дистанционного измерения и сбора измерительно-диагностической информации

- •1.5.1. Общая структура системы

- •1.5.2. Измерительная часть автоматизированной системы дистанционных измерений

- •1.5.3. Алгоритмы работы автоматизированной системы дистанционных измерений

- •1.5.4. Разработка схем подключения средств измерения

- •2. Сигналы и методы их исследования

- •2.1. Общие характеристики электрических сигналов

- •2.2. Методы исследования прохождения сигналов

- •2.3. Динамические модели преобразователей сигналов

- •2.4. Механические, тепловые и электрические аналогии

- •2.4.1. Механические элементы

- •2.4.2. Тепловые элементы

- •2.4.3. Электрические элементы

- •2.5. Фильтры

- •2.5.1. Фильтры нижних частот

- •2.5.2. Фильтры верхних частот

- •2.5.3. Полосовые фильтры

- •2.5.4. Полосно-подавляющие фильтры

- •3. Аналоговая обработка сигналов

- •3.1. Операционные усилители. Основные свойства

- •3.2. Параметры и характеристики оу

- •3.3. Обратная связь в усилителях

- •3.4. Влияние ос на параметры усилителей

- •3.5. Применение операционных усилителей

- •3.5.1. Инвертирующий усилитель

- •3.5.2. Неинвертирующий усилитель

- •3.5.3. Суммирующий усилитель

- •3.5.4. Дифференциальный усилитель

- •3.5.5. Измерительный усилитель

- •3.5.6. Интеграторы

- •3.5.7. Дифференциаторы

- •3.5.8. Нелинейные преобразователи на оу

- •3.6. Активные фильтры

- •4. Цифро-аналоговые и аналого-цифровые преобразователи

- •4.1. Электронные ключи и коммутаторы

- •4.2. Цифро-аналоговые преобразователи

- •4.2.1. Общие положения

- •4.2.2. Цап с суммированием токов

- •4.2.3. Цап с внутренними источниками тока

- •4.2.4. Сегментированные цап

- •4.4.5. Цифровые потенциометры

- •4.2.6. Цап прямого цифрового синтеза

- •4.2.7. Параметры цап

- •4.3. Аналого-цифровые преобразователи

- •4.3.1. Общие положения

- •4.3.3. Ацп последовательного приближения

- •4.3.4. Последовательно-параллельные ацп конвейерного типа

- •4.3.5. Сигма-дельта ацп

- •5. Цифровая обработка сигналов

- •5.1. Общая характеристика цифровых сигналов и цифровых микросхем

- •5.2. Основы алгебры логики

- •5.3. Логические элементы

- •5.3.1. Типы логических элементов

- •5.3.2. Параметры логических элементов

- •5.4. Построение комбинационной логической схемы по заданной функции. Минимизация логических функций

- •5.5. Типы выходных каскадов цифровых элементов

- •5.6. Сложные логические элементы

- •6. Функциональные устройства на цифровых микросхемах

- •6.1. Системы счисления

- •6.2. Дешифраторы и шифраторы

- •6.3. Мультиплексоры и демультиплексоры

- •6.4. Компараторы кодов

- •6.5. Сумматоры

- •6.6. Триггеры

- •6.7. Регистры

- •6.8. Счетчики импульсов

- •6.9. Автоматизированные измерительные системы

- •Заключение

- •Библиографический список

- •394026 Воронеж, Московский просп., 14

6.2. Дешифраторы и шифраторы

Рис.

6.3. Функции дешифратора (слева) и шифратора

(справа)

На выходе дешифратора всегда присутствует только один сигнал (унитарный позиционный код), причем номер этого сигнала однозначно определяется входным кодом. Выходной код шифратора однозначно определяется номером входного сигнала.

Рис. 6.4. Примеры микросхем дешифраторов

В стандартные серии входят дешифраторы на 4 выхода (2 разряда входного кода), на 8 выходов (3 разряда входного кода) и на 16 выходов (4 разряда входного кода). Они обозначаются соответственно как 2–4, 3–8, 4–16. Различаются микросхемы дешифраторов входами управления (разрешения/запрета выходных сигналов), а также типом выхода: 2С или ОК. Выходные сигналы всех дешифраторов имеют отрицательную полярность. Входы, на которые поступает входной код, называют часто адресными входами. Обозначают эти входы 1, 2, 4, 8, где число соответствует весу двоичного кода (1 — младший разряд, 2 — следующий разряд и т. д.), или А0, А1, А2, А3. В отечественных сериях микросхемы дешифраторов обозначают буквами ИД. На рис. 6.4 показаны три наиболее типичных микросхемы дешифраторов.

Таблица 6.3 Таблица

истинности дешифратора 3–8 (ИД7)

Входы

Выходы

C1

4

2

1

0

1

2

3

4

5

6

7

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

0

1

1

1

1

1

1

1

0

0

0

1

0

1

1

0

1

1

1

1

1

1

0

0

0

1

1

1

1

1

0

1

1

1

1

1

0

0

1

0

0

1

1

1

1

0

1

1

1

1

0

0

1

0

1

1

1

1

1

1

0

1

1

1

0

0

1

1

0

1

1

1

1

1

1

0

1

1

0

0

1

1

1

1

1

1

1

1

1

1

0

![]()

![]()

![]() ,

,

![]() объединены по функции И и имеют указанную

на рисунке полярность. Для примера в

табл. 6.3 приведена таблица истинности

дешифратора ИД7 (3–8). Существуют и

дешифраторы 4–10, которые обрабатывают

не все возможные 16 состояний входного

кода, а только первые 10 из них.

объединены по функции И и имеют указанную

на рисунке полярность. Для примера в

табл. 6.3 приведена таблица истинности

дешифратора ИД7 (3–8). Существуют и

дешифраторы 4–10, которые обрабатывают

не все возможные 16 состояний входного

кода, а только первые 10 из них.

Первые три строки таблицы соответствуют запрету выходных сигналов. Разрешением выхода будет единица на входе С1 и нули на входах и . Символ «» обозначает безразличное состояние данного входа (неважно, нуль или единица). Нижние восемь строк соответствуют разрешению выходных сигналов. Номер активного выхода (на котором формируется нулевой сигнал) определяется кодом на входах 1, 2, 4, причем вход 1 соответствует младшему разряду кода, а вход 4 — старшему разряду кода.

Таблица

6.4

Таблица

переключений трехразрядного

дешифратора

x1

x2

x3

f0

f1

f2

f3

f4

f5

f6

f7

0

0

0

0

1

1

1 1

0

0

1

1

0

0

1 1

0

1

0

1

0

1

0 1

1

0

0

0

0

0

0 0

0

1

0

0

0

0

0 0

0

0

1

0

0

0

0 0

0

0

0

1

0

0

0 0

0

0

0

0

1

0

0 0

0

0

0

0

0

1

0 0

0

0

0

0

0

0

1 0

0

0

0

0

0

0

0 1

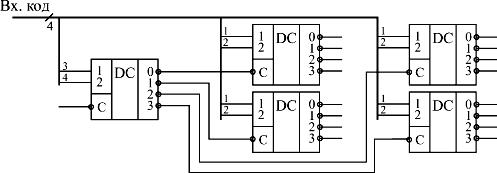

Рис. 6.5. Увеличение

количества разрядов дешифратора

Рис.

6.6. Схема дешифратора и его условное

обозначение

Рис.

6.6. Схема дешифратора и его условное

обозначение

Рассмотрим принцип построения дешифратора на примере трехразрядного двоичного кода. В таком дешифраторе должно быть три входа и восемь выходных шин, так как в трехразрядном двоичном коде имеется 23=8 различных кодовых комбинаций. Если обозначить входные переменные x1, x2, x3, а выходные f0, f1, …, f7, то при i-ом наборе входных переменных только на одном выходе будет «1» (fi=1), а на остальных выходах дешифратора будут «0» (табл. 6.4).

На основании табл. 6.4 можно составить булевы функции для каждого выхода:

![]()

Рис.

6.7. Схема дешифратора двоичного кода в

семисегментный

![]() )

и восемь трехвходовых логических

элементов И (рис. 6.6). Сигнал на выходе

соответствующего логического элемента

И появляется только тогда, когда на всех

его входах имеются логические 1, а это

будет только при кодовой комбинации,

указанной на каждом входе.

)

и восемь трехвходовых логических

элементов И (рис. 6.6). Сигнал на выходе

соответствующего логического элемента

И появляется только тогда, когда на всех

его входах имеются логические 1, а это

будет только при кодовой комбинации,

указанной на каждом входе.

В устройствах визуальной индикации десятичных цифр на световых табло, в которых используются светодиоды, индикаторы на жидких кристаллах, электролюминесцентные или электровакуумные приборы, широко применяют дешифраторы двоично-десятичных кодов в семисегментный код, рис. 6.7. Логическое функционирование такого дешифратора показано в табл. 6.5, где выходы y1—y7 соответствуют семи сегментам индикатора, причем каждый сегмент светится при потенциале, равном нулю (yi=0).

Таблица

6.5

Таблица

истинности дешифратора двоичного кода

в семисегментный

x1

x2

x3

f0

f1

f2

f3

f4

f5

f6

f7

0

0

0

0

1

1

1 1

0

0

1

1

0

0

1 1

0

1

0

1

0

1

0 1

1

0

0

0

0

0

0 0

0

1

0

0

0

0

0 0

0

0

1

0

0

0

0 0

0

0

0

1

0

0

0 0

0

0

0

0

1

0

0 0

0

0

0

0

0

1

0 0

0

0

0

0

0

0

1 0

0

0

0

0

0

0

0 1

Рис.

6.8. Селектирование кода на дешифраторах

![]() и

.

Применяя механические переключатели

выходов дешифраторов (тумблеры), можно

легко изменять код, селектируемый данной

схемой.

и

.

Применяя механические переключатели

выходов дешифраторов (тумблеры), можно

легко изменять код, селектируемый данной

схемой.

Рис. 6.9. Включение

дешифратора как демультиплексора

Как и для любых других цифровых микросхем, для дешифраторов наиболее критична ситуация одновременного или почти одновременного изменения входных сигналов. Например, если стробы С постоянно разрешают работу дешифратора, то в момент изменения входного кода на любом выходе дешифратора могут появиться паразитные отрицательные короткие импульсы. Это может быть связано как с неодновременным выставлением разрядов кода (из-за несовершенства микросхем источников кода или из-за разных задержек распространения по линиям связи), так и с внутренними задержками самих микросхем дешифраторов.

Рис. 6.10. Стробирование

выходных сигналов дешифратора

Рис. 6.11. Позиционная

индикация на дешифраторе с выходами

ОК

Шифраторы используются гораздо реже, чем дешифраторы. Это связано с более специфической областью их применения. Значительно меньше и выбор микросхем шифраторов в стандартных сериях. В отечественных сериях шифраторы имеют в названии буквы ИВ.

Рис. 6.12. Микросхемы

шифраторов

![]() ,

выход признака прихода любого входного

сигнала

,

выход признака прихода любого входного

сигнала

![]() ,

а также выход переноса

,

а также выход переноса

![]() ,

позволяющий объединять несколько

шифраторов для увеличения разрядности.

,

позволяющий объединять несколько

шифраторов для увеличения разрядности.

Таблица 6.6 Таблица

истинности шифратора ИВ1

Входы

Выходы

0

1

2

3

4

5

6

7

4

2

1

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

0

1

1

1

0

0

1

1

1

0

0

1

1

1

1

0

1

0

0

1

0

0

1

1

1

1

1

0

1

0

1

1

0

0

1

1

1

1

1

1

0

1

1

0

1

0

0

1

1

1

1

1

1

1

0

1

1

1

1

![]()

![]()

![]()

Как видно, на выходах кода 1, 2, 4 формируется инверсный двоичный код номера входной линии, на которую приходит отрицательный входной сигнал. При одновременном поступлении нескольких входных сигналов формируется выходной код, соответствующий входу с наибольшим номером, т. е. старшие входы имеют приоритет перед младшими. Поэтому такой шифратор называют приоритетным. При отсутствии входных сигналов (вторая строчка таблицы) формируется выходной код 111. Единичный сигнал (первая строчка) запрещает работу шифратора (все выходные сигналы устанавливаются в единицу). На выходе вырабатывается нуль при приходе любого входного сигнала, что позволяет, в частности, отличить ситуацию прихода нулевого входного сигнала от ситуации отсутствия любых входных сигналов. Выход становится активным (нулевым) при отсутствии входных сигналов, но разрешении работы шифратора сигналом .

Стандартное применение шифраторов состоит в сокращении количества сигналов. Например, в случае шифратора ИВ1 информация о восьми входных сигналах сворачивается в три выходных сигнала. Это очень удобно, например, при передаче сигналов на большие расстояния. Правда, входные сигналы не должны приходить одновременно. На рис. 6.13 показаны стандартная схема включения шифратора и временные диаграммы его работы.

Инверсия выходного кода приводит к тому, что при приходе нулевого входного сигнала на выходе формируется не нулевой код, а код 111, т. е. 7. Точно так же при приходе, например, третьего входного сигнала на выходе образуется код 100, т. е. 4, а при приходе пятого выходного сигнала — код 010, т. е. 2.

Рис. 6.13. Стандартное

включение шифратора

Рис. 6.14. Шифратор

16–4 на двух шифраторах 8–3

Задержка шифратора от входа до выхода кода примерно в полтора раза превышает задержку логического элемента, а задержка до выхода GS — примерно в два раза больше.