Учебное пособие 1492

.pdf

Алгоритм исследования.

Для проведения исследования необходимо:

1.Активировать пакет программ Design Center. Для этого необходимо открыть папку Micro Sim Design Lab.

2.Загрузить графический редактор Schematics.

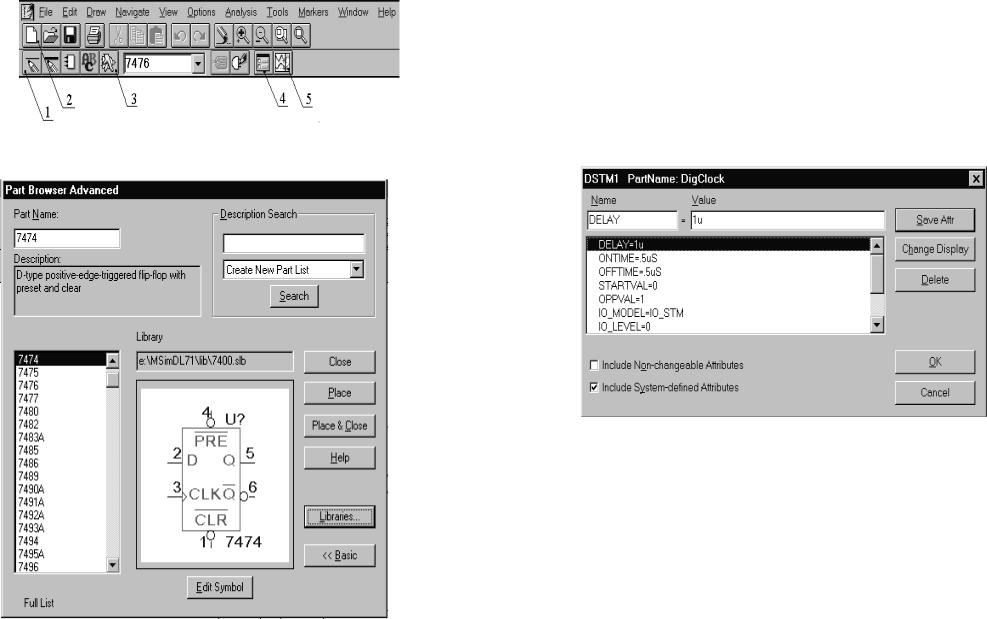

3.При необходимости создания новой схемы щелкнуть мышкой на кнопку 2, показанную на рис. 4.1.

4.Достать из библиотеки необходимые элементы. Для

этого:

а) щелкнуть мышкой на кнопку 3 (рис. 4.1);

Рис. 4.1 Панель инструментов Shematics

б) в появившемся окне, в строке Part Name записать условное обозначение элемента ( 7483А );

в) нажать кнопку Place;

г) чтобы из библиотеки достать генератор импульсов в строке Part Name нужно записать DigCloсk;

д) найти в библиотеке другие необходимые элементы; е) нажать кнопку Place&Close.

5.Расставить элементы в нужном порядке.

6.Провести соединительные линии. Для этого необходимо щелкнуть мышкой по кнопке 1 (рис. 4.1).

7.Задать параметры генераторов. Для этого

а) дважды щелкнуть мышкой по его изображению; б) в появившемся окне (рис. 4.2) выбрать необходимый

параметр;

Рис. 4.2 Окно параметров генератора

в) в строке Value записать его значение и нажать Enter ; г) после ввода всех необходимых параметров щелкнуть

по кнопке OK.

8.Расставить значки ( вольтметры ) с помощью клавиш Ctrl+M. Расставлять, начиная с младшего разряда на выходе.

( вольтметры ) с помощью клавиш Ctrl+M. Расставлять, начиная с младшего разряда на выходе.

9.Установить параметры анализа, щёлкнув по кнопке 4 (рис. 4.1).

10.Затем щелкнуть мышкой по кнопке Transient.

11.В появившемся окне, в строке Print Step записать 1u,

ав строке Final Time 50u

12.Нажать OK.

13.Нажать Close.

14.Запустить схему на анализ, щёлкнув мышкой по кнопке 5 (рис. 4.1).

15.Для составления таблицы счетной последовательности сумматора необходимо выполнить команду Cursor. Перемещая мышью или с помощью клавиатуры курсор по времен-

60 |

61 |

ным диаграммам, снимать с монитора искомые логические значения.

Рис.4.3 Четырехразрядный сумматор на элементе 7483А Временные диаграммы для данного сумматора представ-

лены на рис. 4.4.

Рис.4.4 Временные диаграммы для сумматора 7483А

Таблица истинности двоичного сложения представлена в табл. 4.1. В соответствующей таблице истинности представлены все возможные комбинации двоичных одноразрядных слагаемых А, В и сигнала переноса Сin

Таблица 4.1 Таблица истинности для двоичного сложения

|

Входы |

|

|

Выходы |

||

0 |

0 |

|

0 |

0 |

|

0 |

0 |

0 |

|

1 |

1 |

|

0 |

0 |

1 |

|

0 |

1 |

|

0 |

0 |

1 |

|

1 |

0 |

|

1 |

1 |

0 |

|

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

|

1 |

1 |

1 |

|

0 |

0 |

|

1 |

1 |

1 |

|

1 |

1 |

|

1 |

|

Перенос+В+ |

А |

|

Сумма |

|

Перенос |

4.2. ИССЛЕДОВАНИЕ СУММАТОРОВ И ВЫЧИТАТЕЛЕЙ

4.2.1. Схемотехническое моделирование четырёхразрядного двоичного сумматора на микросхеме 7483А

В данном исследовании задать следующие параметры генераторов:

для генератора DSTМ1 (А1)

DELAY = 1uS , ONTIME = 1uS , OFFTIME = 1uS;

для генератора DSТМ2 (А2)

DELAY = 2uS , ONTIME = 2uS , OFFTIME = 2uS;

для генератора DSТМ3 (А3)

DELAY = 4uS , ONTIME = 4uS , OFFTIME = 4uS;

для генератора DSТМ4 (А4)

DELAY = 8uS , ONTIME = 8uS , OFFTIME = 8uS;

для генератора DSТМ5 (B1)

DELAY = 0.5uS , ONTIME = 1uS , OFFTIME = 1uS;

62 |

63 |

для генератора DSТМ6 (B2)

DELAY = 1.5uS , ONTIME = 2uS , OFFTIME = 2uS;

для генератора DSТМ7 (B3)

DELAY = 3.5uS , ONTIME = 4uS , OFFTIME = 4uS;

для генератора DSТМ8 (B4)

DELAY = 7.5uS , ONTIME = 8uS , OFFTIME = 8uS;

Для всех генераторов задать STARTVAL=0, OPPVAL=1.

4.2.2.Индивидуальные задания Схемотехническое моделирование различных сумма-

торов, построенных на логических элементах

Раздел 4.2.2 содержит два варианта. Номер варианта взять четным или нечетным в зависимости от номера ПЭВМ.

4.2.2.1Схемотехническое моделирование полусумматора

иполного сумматора

Полусумматором называется комбинационное логическое, предназначенное для сложения двух одноразрядных кодов, имеющее два входа и два выхода и формирующее из сигналов входных слагаемых сигналы суммы и переноса в старший разряд.

Для обеспечения требуемого логического уровня на выходе суммы необходим только один 2-входовый логический элемент ИЛИ.

Логическая схема полусумматора составлена из 2- входового логического элемента исключающее ИЛИ и 2- входового логического элемента И. Полусумматор осуществляет сложение только в разряде единиц. Для двоичного сложения в разряде двоек, четверок и т.д. нужно использовать устройство, называемое полным сумматором. Полные сумматоры используются для сложения во всех двоичных разрядах, кроме разряда единиц. Они должны иметь дополнительный вход переноса.

Задание 1

Составить задание на моделирование полусумматора, схема измерения которого представлена на рис. 4.5. Функциональный состав сумматора задать согласно варианту раздела

4.2.2.5.

Рис.4.5 Схема измерения полусумматора

Задание 2

Снять временные диаграммы полусумматора.

Значения параметров генераторов задать согласно варианту раздела 4.2.2.5.

Задание 3

Заполнить таблицу переключений для полусумматора согласно форме, представленной в табл.4.2.

Таблица 4.2 Форма таблицы переключений для полусумматора

DS-A1 |

DS-B1 |

SumA |

CO |

Задание 4

Составить задание на моделирование полного сумматора, схема измерения которого представлена на рис. 4.6. Функцио-

64 |

65 |

нальный состав полного сумматора задать согласно варианту раздела 4.2.2.5.

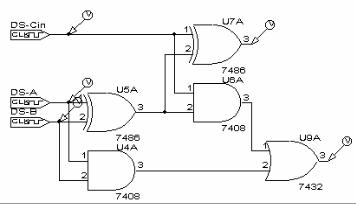

Рис. 4.6. Логическая схема полного сумматора

Задание 5

Снять временные диаграммы полного сумматора. Значения параметров генераторов задать согласно вари-

анту раздела 4.2.2.5.

Задание 6

Заполнить таблицу переключений для полного сумматора согласно форме, представленной в табл. 4.3.

|

|

|

|

Таблица 4.3 |

|

Форма таблицы переключений для полного сумматора |

|||||

DS-A |

DS-B |

DS-Cin |

U7A:Y |

U9A:Y |

|

4.2.2.2. Схемотехническое моделирование полувычитателя и полного вычитателя

Сумматоры и вычитатели очень похожи друг на друга, и, кроме того, полувычитатели и полные вычитатели используются аналогично полусумматорам и полным сумматорам. По-

рядок двоичного вычитания приведен в табл. 4.4. Видно, что В вычитается из А (А и В-входные сигналы), результат (разность) появляется на выходе Di. Если В больше А (как в строке 2 таблицы), нужно занять 1 в соседнем старшем разряде. Сигнал заема в столбце Во.

Таблица 4.4 Таблица истинности для полувычитателя

|

Входы |

|

Выходы |

|

А |

В |

Di |

|

Bo |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

|

1 |

1 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

|

А-В |

Разность |

|

Заем |

При вычитании многоразрядных двоичных чисел нужно принимать во внимание заем “единиц” в более старших разрядах и использовать полный сумматор. По аналогии с полным сумматором вычитатель можно собрать из двух полувычитателей и логического элемента ИЛИ.

Задание 1

Составить задание на моделирование полувычитателя, схема измерения которого представлена на рис. 4.7. Функциональный состав сумматора задать согласно варианту раздела

4.2.2.5.

Задание 2

Снять временные диаграммы полусумматора. Значения параметров генератора задать согласно варианту раздела

4.2.2.5.

Задание 3

Заполнить таблицу переключений для полувычитателя согласно форме, представленной в.табл.4.5.

66 |

67 |

|

|

|

|

Таблица 4.5 |

||

Форма таблицы переключений для полувычитателя |

||||||

DSTM1 |

DSTM2 |

U1A:Y |

U2A:Y |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4.7. Логическая схема полувычитателя

Задание 4

Составить задание на моделирование полного вычитателя, схема измерения которого представлена на рис. 4.8. Функциональный состав полного сумматора задать согласно варианту раздела 4.2.2.5.

Рис. 4.8. Логическая схема полного вычитателя

Задание 5

Снять временные диаграммы полного вычитателя. Значения параметров генераторов задать согласно вари-

анту раздела 4.2.2.5.

Задание 6

Заполнить таблицу переключений для полного вычитателя согласно форме, представленной в табл. 4.6.

Таблица 4.6 Форма таблицы переключений для полного вычитателя

DS-A |

DS-B |

DS-Bin |

DiA |

UBoA |

4.2.2.3. Схемотехническое моделирование 3-разрядного параллельного сумматора

Определенным образом, соединяя полусумматоры и полные сумматоры друг с другом, получают устройства, одновременно выполняющие сложение нескольких двоичных разрядов. Устройство, схема которого показана на рис. 4.9 складывает 3-разрядные двоичные числа (числа-слагаемые А2А1А0 и В2В1В0). Сигналы, соответствующие значением разряда единиц в слагаемых, поступают на входы сумматора разряда единиц (полусумматора). Входными сигналами для полного сумматора разряда двоек являются сигнал переноса с выхода полусумматора и значения А1и В1 разряда двоек. На двоичном выходе устройства индицируется искомая двоичная сумма. В результате сложения двух 3-разрядных чисел может получиться 4-разрядное число, поэтому на индикаторе суммы имеется дополнительный разряд восьмерок.

В параллельном сумматоре информационные биты всех разрядов на выходы поступают одновременно. Результат (сумма) появляется на выходе практически мгновенно.

Задание 1

Составить задание на моделирование 3-разрядного параллельного сумматора, представленного на рис. 4.9. Функ-

68 |

69 |

циональный состав сумматора задать согласно варианту раз-

дела 4.2.2.5.

Задание 2

Снять временные диаграммы параллельного сумматора. Значения параметров генератора задать согласно варианту раздела 4.2.2.5.

Задание 3

Заполнить таблицу переключений для данного сумматора согласно форме, представленной в табл.4.7.

Таблица 4.7 Форма таблицы переключений для параллельного 3-

разрядного сумматора

DS-A0 |

DS-A1 |

DS-A2 |

DS-B0 |

DS-B1 |

DS-B2 |

U15A |

U13A |

U14A |

U9A |

|

|

|

|

|

|

|

|

|

|

4.2.2.4. Схемотехническое моделирование 3-разрядного параллельного вычитателя

Соединяя друг с другом полувычитатель и полные вычитатели, получают устройства, называемые параллельными вычитателями. Вычитатель, представленный на рис. 4.10, называется параллельным, поскольку информационные биты всех разрядов в слагаемых поступают в этот вычитатель одновременно.

Схема вычитателя получена путем объединения одного полувычитателя и двух полных вычитателей. Полувычитатель осуществляет вычитание в разряде единиц. Один из выходов полувычитателя связан с вычитателя разряда двоек. Вообще выход заема каждого вычитателя связан со входом заема вычитателя соседнего старшего разряда.

Задание 1

Составить задание на моделирование параллельного вычитателя, представленного на рис.4.8. Функциональный состав вычитателя задать согласно варианту раздела 4.2.2.5.

Рис. 4.9. 3-разрядный параллельный сумматор

70 |

71 |

Задание 2

Снять временные диаграммы вычитателя. Значения параметров генератора задать согласно варианту раздела 4.2.2.5.

Задание 3

Заполнить таблицу переключений для параллельного вычитателя согласно форме, представленной в табл. 4.8.

В форме таблицы записаны наименования выходов элементов, с которых необходимо снимать значения.

Рис. 4.10. 3-разрядный параллельный вычитатель Таблица 4.8

Форма таблицы переключений для параллельного вычитателя

DS-A1 |

DS-A2 |

DS-A3 |

DS-B1 |

DS-B2 |

DS-B3 |

R1A |

R2A |

R3A |

U21A |

|

|

|

|

|

|

|

|

|

|

4.2.2.5. Параметры для моделирования Параметры для задания 4.2.2.1

В данном задании для моделирования полусумматора используются 2 импульсных генератора (DigClock), а также логические элементы исключающее ИЛИ типа 7486 и И типа 7408. Эти элементы достают из библиотек. Для реализации задания необходимо выполнить последовательность действий раздела 4.1 (начиная с пп.3) с учетом используемых элементов в данном задании. Параметры генераторов можно задавать любыми (желательно различными), например,

параметры для генератора DS-А :

DELAY = 1uS , ONTIME = 2uS , OFFTIME = 2uS;

параметры для генератора DS-В :

DELAY = 3uS , ONTIME = 1uS , OFFTIME = 1uS.

Для моделирования полного сумматора используются схемы двух полусумматоров и одного логического элемента ИЛИ типа 7432, а также 3 импульсных генератора.

Параметры генераторов для полного сумматора можно задавать любыми, например:

параметры для генератора DS-Cin :

DELAY = 8uS , ONTIME = 8uS , OFFTIME = 8uS;

параметры для генератора DS-А :

DELAY = 4uS , ONTIME = 4uS , OFFTIME = 4uS;

параметры для генератора DS-В :

DELAY = 2uS , ONTIME = 2uS , OFFTIME = 2uS.

Работоспособность устройства проверяется исходя из условия, что сумма чисел на входе должна ровняться числу на выходе.

72 |

73 |

Параметры для задания 4.2.2.2 В данном задании для моделирования полувычитателя

используются 2 импульсных генератора, инвертор типа 7404, а также логические элементы исключающее ИЛИ типа 7486 и И типа 7408. Эти элементы достают из библиотек. Для реализации задания необходимо выполнить последовательность действий раздела 4.1 (начиная с пп.3) с учетом используемых элементов в данном задании. Параметры генераторов можно задавать любыми (желательно различными), например,

параметры для генератора DSTM1 :

DELAY = 4uS , ONTIME = 4uS , OFFTIME = 4uS;

параметры для генератора DSTM2 :

DELAY = 2uS , ONTIME = 2uS , OFFTIME = 2uS.

Для моделирования полного вычитателя используются схемы двух полувычитателей и одного логического элемента ИЛИ типа 7432, а также 3 импульсных генераторов.

Параметры генераторов для полного вычитателя можно задавать любыми, например:

параметры для генератора DS-Bin :

DELAY = 2uS , ONTIME = 2uS , OFFTIME = 2uS;

параметры для генератора DS-А :

DELAY = 4uS , ONTIME = 4uS , OFFTIME = 4uS;

параметры для генератора DS-В :

DELAY = 8uS , ONTIME = 8uS , OFFTIME = 8uS.

Работоспособность устройства проверяется исходя из условия, что разность A-B-Bin на входе должна равняться числу на выходе.

Параметры для задания 4.2.2.3 В данном задании используются 6 импульсных генера-

торов, а также два полных сумматора (их функциональный состав описан в разделе 4.2.2.3) и один полусумматор (его

функциональный состав описан в разделе 4.2.2.3). Для выполнения задания необходимо выполнить последовательность действий раздела 4.1 (начиная с пп.3) с учетом используемых элементов в данном задании.

Параметры генераторов для параллельного сумматора можно задавать любыми (желательно различными), например:

параметры для генератора DS-А0 :

DELAY = 2uS , ONTIME = 2uS , OFFTIME = 2uS;

параметры для генератора DS-А1 :

DELAY = 4uS , ONTIME = 4uS , OFFTIME = 4uS;

параметры для генератора DS-A2 :

DELAY = 8uS , ONTIME = 8uS , OFFTIME = 8uS.

параметры для генератора DS-B0 :

DELAY = 1.5uS , ONTIME = 2uS , OFFTIME = 2uS;

параметры для генератора DS-B1 :

DELAY = 3.5uS , ONTIME = 4uS , OFFTIME = 4uS;

параметры для генератора DS-B2 :

DELAY = 7.5uS , ONTIME = 8uS , OFFTIME = 8uS.

Работоспособность устройства проверяется исходя из условия, что сумма чисел на входе должна ровняться числу на выходе.

Параметры для задания 4.2.2.4 В данном задании используются 6 импульсных генера-

торов, а также два полных вычитателя (их функциональный состав описан в разделе 4.2.2.2) и один полувычитатель (его функциональный состав описан в разделе 4.2.2.2). Для выполнения задания необходимо выполнить последовательность действий раздела 4.1 (начиная с пп.3) с учетом используемых элементов в данном задании.

Параметры генераторов для параллельного вычитателя можно задавать любыми (желательно различными), например,

параметры для генератора DS-А1 :

DELAY = 17uS , ONTIME = 16uS , OFFTIME = 16uS;

параметры для генератора DS-А2 :

74 |

75 |

DELAY = 8uS , ONTIME = 8uS , OFFTIME = 8uS;

параметры для генератора DS-A3 :

DELAY = 3uS , ONTIME = 4uS , OFFTIME = 4uS.

параметры для генератора DS-B1 :

DELAY = 18uS , ONTIME = 16uS , OFFTIME = 16uS;

параметры для генератора DS-B2 :

DELAY = 9uS , ONTIME = 8uS , OFFTIME = 8uS;

параметры для генератора DS-B3 :

DELAY = 4uS , ONTIME = 4uS , OFFTIME = 4uS.

Работоспособность устройства проверяется, исходя из условия, что разность между уменьшаемым и вычитаемым на входе должна ровняться разности на выходе.

4.3.СОДЕРЖАНИЕ ОТЧЕТА

1.Схемы измерения сумматоров или вычитателей.

2.Значения параметров цифровых сигналов.

3.Значения параметров анализа переходных характеристик

(Transient).

4.Временные диаграммы работы сумматоров (вычитателей).

5.Таблицы счетных последовательностей.

6.Обсуждение результатов, выводы по работе.

5. КОМПЬЮТЕРНЫЙ АНАЛИЗ D- И RS-ТРИГГЕРОВ

Цель исследования. Приобрести навыки схемотехнического моделирования RS и D – триггеров с помощью ПЭВМ с использованием программной системы Design Center.

Содержание исследования. В процессе исследования выполняется схемотехническое моделирование D – триггеров (микросхема 7474), RS – триггеров, построенных на логических элементах И – НЕ, RS – триггеров – на логических элементах ИЛИ – НЕ. Кроме того, осуществляется схемотехническое моделирование стартстопного устройства, выполненного на RS – триггере и управляемом им вентиле. Вводимые параметры генераторов выбираются из раздела 5.3.

Подготовительный этап. Триггером называется электронное устройство, имеющее два устойчивых состояния равновесия и способное скачком переходить из одного состояния в другое под воздействием внешнего управляющего сигнала. Чаще триггер применяется в качестве элемента памяти.

Проработать разделы "Математическое описание цифро-

вых устройств" [1, с.553-556], "Триггеры" [11, с. 194-221] и "Интегральные триггеры" [8, с. 351-354; 11, с. 222-224].

5.1.ОБЩИЕ УКАЗАНИЯ ПО ПРОВЕДЕНИЮ АНАЛИЗА

1.Загрузить графический редактор Shematics.

2.При необходимости создания новой схемы, щелкнуть мышкой на кнопку 2 показанную на рис. 5.1.

3.Извлечь из библиотеки необходимые элементы. Для этого:

а) щелкнуть мышкой на кнопку 3 (рис. 5.1); в) нажать кнопку Place;

г) чтобы из библиотеки достать генератор импульсов в строке Part Name нужно записать DigCloсk;

д) нажать кнопку Place&Close

76 |

77 |

4. Расставить элементы в нужном порядке.

5. Провести соединительные линии. Для этого необходимо щелкнуть мышкой по кнопке 1 (рис. 5.1).

6. Задать параметры генераторов. Для этого:

а) дважды щелкнуть мышкой по его изображению (рис.

5.2);

б) в появившемся окне (рис. 5.3) выбрать необходимый

параметр;

Рис. 5.1. Панель инструментов Schematics

Рис. 5.3 Окно параметров генератора

в) в строке Value записать его значение и нажать Enter; г) после ввода всех необходимых параметров щелкнуть

по кнопке OK.

7. Расставить значки (вольтметры) с помощью клавиш Ctrl+M.

(вольтметры) с помощью клавиш Ctrl+M.

8. Установить параметры анализа, щёлкнув по кнопке 4 (рис. 5.1).

9. Затем щелкнуть мышкой по кнопке Transient.

Рис. 5.2. Окно содержания элементов в библиотеках

78 |

79 |