Учебное пособие 1492

.pdf

|

|

Таблица 1.4 |

|

Основная номенклатура микросхем серии К155, КМ155 |

|||

Функция |

Микросхемы |

||

Отечественные |

Зарубежные |

||

|

|||

|

ЛН1 ЛН2(ОК) |

04 05 06 16 |

|

Инверторы |

ЛН3 ЛН5(ОК) |

||

366 |

|||

|

ЛН6(Z) |

||

|

|

||

Повторитель |

ЛП4(ОК) |

17 |

|

2 – И |

ЛИ1 |

08 |

|

2 - И – НЕ |

ЛА3 ЛА8(ОК) |

00 01 26 37 |

|

ЛА11(ОК) ЛА12 |

|||

|

|

||

3 - И – НЕ |

ЛА4 ЛА10(ОК) |

10 12 |

|

4 - И – НЕ |

ЛА6 ЛА7(ОК) |

40 22 |

|

8 - И – НЕ |

ЛА2 |

30 |

|

2 – ИЛИ |

ЛЛ1 |

32 |

|

2 – ИЛИ – НЕ |

ЛЕ1 ЛЕ5 ЛЕ6 |

02 28 128 |

|

3 – ИЛИ – НЕ |

ЛЕ4 |

27 |

|

4 – ИЛИ – НЕ |

ЛЕ2 ЛЕ3 |

23 25 |

|

Исключающее ИЛИ |

ЛП5 |

86 |

|

D – Триггеры |

ТМ2 ТМ5 ТМ7 |

74 77 75 175 |

|

ТМ8 |

|||

|

|

||

JK – Триггеры |

ТВ1 ТВ15 |

72 109 |

|

Счетчики |

ИЕ2 ИЕ4 ИЕ5 |

90 92 93 192 |

|

ИЕ6 ИЕ7 ИЕ8 |

|||

193 97 160 |

|||

|

ИЕ9 |

||

|

|

||

Регистры |

ИР1 ИР13 |

95 198 173 |

|

ИР15(ОК) |

|||

|

|

||

Дешифраторы |

ИД1 ИД10(ОК) |

141 145 |

|

Дешифраторы / Демуль- |

ИД3 ИД4 |

154 155 |

|

типлексоры |

|||

ИВ1 |

|

||

Шифраторы |

148 |

||

Селекто- |

КП1 КП2 КП5 |

150 153 152 |

|

ры/Мультиплексоры |

КП7 |

151 |

|

|

|

|

|

Таблица 1.5 Обозначения основных логических элементов

Логическая |

Обозначение по |

Обозначение по |

|

функция эле- |

стандарту |

ГОСТ |

|

мента |

MIL/ANSI |

||

|

|||

Буфер |

|

|

Инвертор

И

И – НЕ

ИЛИ

ИЛИ – НЕ

Исключающее

ИЛИ

20 |

21 |

Таблица 1.6 Соответствие отечественных и зарубежных серий циф-

ровых микросхем

Зарубежная |

Отечественная серия |

Имя библиотеки |

серия |

|

|

74H |

K131 |

74H.slb |

74 |

K155 |

7400.slb |

74L |

K134 |

74L.slb |

74S |

K531 |

74S.slb |

74LS |

K555 |

74LS.slb |

|

|

|

74F |

K1531 |

74F.slb |

74ALS |

K1533 |

74ALS.slb |

|

|

|

1.2 ИССЛЕДОВАНИЕ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

1.2.1 Схемотехническое моделирование логических элементов

Перечень конкретных исследований и порядок их выполнения изложены в разделе 1.1. Тип микросхемы, содержащей заданный логический элемент, взять на основании таблицы 1.8. Значения параметров генераторов DSTM1, DSTM2 взять из таблицы 1.9. Значения параметров моделирования взять из таблицы 1.10.

1.2.2. Схемотехническое моделирование логических элементов НЕ, И, И - НЕ, ИЛИ, ИЛИ - НЕ, исключающее ИЛИ.

При выполнении исследования использовать типы серий и порядок расположения элементов, приведенных в таблице 1.8. При этом в колонке «П» указан порядок следования элементов в схеме измерения сверху вниз. Например, на рисунке 1.11 порядок следующий: 1, 2, 3, 4, 5, 6. Значения параметров генераторов DSTM1, DSTM2 и значения параметров

моделирования взять такими же, как при выполнении задания

1.2.1.

Ниже приведен пример результатов исследования заданных микросхем. В работе использовались микросхемы, модели которых находятся в библиотеке 7400.slb:

7404 (отечественный аналог К155ЛН1), представляющая собой набор из шести элементов НЕ;

7408 (отечественный аналог К155ЛИ1), содержащая в себе четыре элемента И;

7400 (отечественный аналог К155ЛА3), в состав которой входит набор из четырех элементов И – НЕ;

7432 (отечественный аналог К155ЛП1), состоящая из четырех элементов ИЛИ;

7402 (отечественный аналог К155ЛЕ1), которая является набором из четырех элементов ИЛИ – НЕ;

7486 (отечественный аналог К155ЛП5), которая является набором из четырех элементов, исключающее ИЛИ.

Схема измерения для проведения данной работы приведена на рисунке 1.11.

Временные диаграммы работы логических элементов приведены на рисунке 1.12.

Таблица истинности - в таблице 1.7.

Таблица 1.7 Таблица истинности логических элементов

DSTM1 A |

DSTM2 B |

U1AY(НЕ) |

U2AY (И) |

U3AY (И - НЕ) |

U4AY (ИЛИ) |

U5AY (ИЛИ - НЕ) |

1 |

|

|

|

|

|

|

1 |

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

22 |

23 |

Рис. 1.11. Схема измерения логических элементов

Рис. 1.12. Временные диаграммы работы логических элементов

Таблица 1.8 Типы серий и порядок расположения элементов

|

|

Группа |

|

Подгруппа |

|

п |

|

Логиче- |

п/ |

|

ский эле- |

№ |

|

|

|

мент |

|

|

|

|

1 |

|

04 (НЕ) |

|

|

|

2 |

|

08 (И) |

|

|

|

3 |

|

00 |

|

(И–НЕ) |

|

|

|

|

4 |

|

32 (ИЛИ) |

|

|

|

5 |

|

02 (ИЛИ– |

|

НЕ) |

|

|

|

|

|

|

|

|

|

86 |

6 |

|

(искл. |

|

|

ИЛИ) |

|

|

|

|

1 |

|

|

|

|

|

2 |

|

|

|

|

|

3 |

|

|

|

1 |

|

|

2 |

1 |

|

2 |

|

|

1 |

|

|

2 |

||||

Серия |

П |

Серия |

П |

Серия |

П |

Серия |

|

П |

Серия |

|

П |

|

Серия |

|

П |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74ALS |

1 |

74 |

5 |

74 |

4 |

74LS |

|

5 |

74ALS |

|

2 |

|

74 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74LS |

4 |

74ALS |

|

1 |

74ALS |

2 |

74 |

|

6 |

74LS |

|

4 |

|

74 |

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74ALS |

2 |

74 |

|

2 |

74 |

1 |

74ALS |

|

2 |

74LS |

|

5 |

|

74ALS |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74 |

5 |

74LS |

|

3 |

74LS |

5 |

74 |

|

1 |

74 |

|

3 |

|

74LS |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74LS |

3 |

74ALS |

|

6 |

74 |

6 |

74ALS |

|

3 |

74LS |

|

1 |

|

74LS |

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

74 |

6 |

74ALS |

|

4 |

74 |

3 |

74LS |

|

4 |

74ALS |

|

6 |

|

74ALS |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

24 |

25 |

Таблица 1.9 Значения вводимых параметров генераторов

Номер варианта |

тип генератора |

DELAY |

ONTIME |

OFFTIME |

STARTVAL |

OPP VAL |

|

|

|

|

|

|

|

|

|

|

DSTM1 |

0.1us |

0.5us |

0.5us |

0 |

1 |

|

1 |

|

|

|

|

|

|

|

|

DSTM2 |

0.1us |

1us |

1us |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

DSTM1 |

0.2us |

0.2us |

0.8us |

0 |

1 |

|

2 |

|

|

|

|

|

|

|

DSTM2 |

0.2us |

1.7us |

0.3us |

0 |

1 |

||

|

|||||||

|

|

|

|

|

|

|

|

|

DSTM1 |

1us |

0.8us |

0.2us |

0 |

1 |

|

3 |

|

|

|

|

|

|

|

DSTM2 |

1us |

0.3us |

1.7us |

0 |

1 |

||

|

|||||||

|

|

|

|

|

|

|

|

|

DSTM1 |

0.5us |

0.3us |

0.7us |

0 |

1 |

|

4 |

|

|

|

|

|

|

|

DSTM2 |

0.5us |

1.3us |

0.7us |

0 |

1 |

||

|

|||||||

|

|

|

|

|

|

|

|

|

DSTM1 |

0.3us |

0.7us |

0.3us |

0 |

1 |

|

5 |

|

|

|

|

|

|

|

DSTM2 |

0.3us |

0.7us |

1.3us |

0 |

1 |

||

|

|||||||

|

|

|

|

|

|

|

|

|

Таблица 1.10 |

|

Значения параметров моделирования |

|||

Номер варианта |

Тип параметра |

Значение |

|

1 |

Print Step |

0.1u |

|

Final Time |

4u |

|

|

|

|

||

2 |

Print Step |

0.1u |

|

Final Time |

5u |

|

|

|

|

||

3 |

Print Step |

0.15u |

|

Final Time |

4.5u |

|

|

|

|

||

4 |

Print Step |

0.05u |

|

Final Time |

5.5u |

|

|

|

|

||

5 |

Print Step |

0.2u |

|

Final Time |

3.5u |

|

|

|

|

||

1.3.СОДЕРЖАНИЕ ОТЧЁТА

1.Задание на моделирование в графической форме.

2.Значение параметров генераторов цифровых сигна-

лов DSTM1, DSTM2.

3.Типы исследуемых микросхем с указанием отечественных аналогов.

4.Таблица графических назначений исследуемых логических элементов с использованием отечественных и зарубежных стандартов.

5.Временные диаграммы работы логических элемен-

тов.

6.Обсуждение результатов, выводы по работе.

26 |

27 |

2. КОМПЬЮТЕРНЫЙ АНАЛИЗ ШИФРАТОРОВ И ДЕШИФРАТОРОВ

Цель исследования. Приобрести навыки схемотехнического моделирования дешифратора, преобразующего двоичный n-разрядный код в унитарный код “1 из 10” или “1 из 16”,

атак же шифратора десятичных кодов при помощи ПЭВМ в среде Design Center/

Содержание исследования. Ниже изложен алгоритм схемотехнического моделирования шифраторов и дешифраторов, согласно которому выполняется моделирование дешифратора SN7442А на ПЭВМ. Схемотехническое моделирование включает четыре основных этапа: составление задания на моделирование, ввод параметров генераторов, снятие временных диаграмм и построение таблиц истинности. Кроме того, по указанному алгоритму производится исследование ряда других комбинационных интегральных устройств согласно индивидуальному заданию.

Подготовительный этап Проработать разделы, посвященные принципам построения, схемотехнике и функционированию различных видов шифраторов и дешифраторов[1, с. 544-550; 7, с.115-130; 11, с. 108-125].

Дешифратор представляет собой функциональный узел, преобразующий двоичный n-разрядный код в унитарный код

“1 из N”. В общем случае дешифратор с n адресными входами имеет 2 n выходов, каждый из которых принимает значение, равное 1 при единственной комбинации входных сигналов. В данной работе используются микросхемы ТТЛ из серии SN74,

аименно - 7442А, 7443А, 7444А, 74141, представляющие собой дешифраторы “из 4 в 1 из 10”, а так же дешифратордемультиплексор 74154.

Шифратор предназначен для преобразования унитарного кода (в данной работе - “1 из 7” и “1 из 9”) в n-разрядный код. В данной работе используются микросхемы ТТЛ из се-

рии SN74, а именно - 74148 и 74147.

Исследования предусматривает выполнение схемотехнического моделирования дешифратора на микросхеме 7442А,

а также моделирование других устройств согласно индивидуальному заданию. На входы микросхем подаются логические импульсы при помощи стандартных генераторов из библиотеки SOURCE. Для того, чтобы обеспечить поступление на вход всех возможных комбинаций сигналов, необходимо задать периоды импульсов и пауз генераторов в виде геометрической прогрессии со знаменателем 2 - например: 1,2,4,8,16 мкс. Временные зависимости входного и выходного напряжений просматриваются при помощи программы Probe среды PSpice.

2.1.ОБЩИЕ УКАЗАНИЯ ПО ПРОВЕДЕНИЮ АНАЛИЗА

1.Запустить программу Schematics

2.Войти в библиотеку элементов, для чего нажать мышью кнопку  .

.

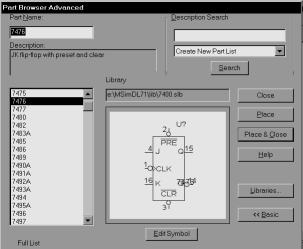

3.Нажать мышью кнопку «Libraries». При этом должно появиться окно, показанное на рис. 2.1.

Рис.2.1 Окно библиотек

4.В колонке «Library» выбрать библиотеку 7400.

5.В колонке «Part» выбрать номер микросхемы, нажать

«OK» и «Place&Close».

28 |

29 |

6.Установить изображение элемента на нужное место и зафиксировать его щелчком мыши.

7.Аналогично пп.2-6 выбрать в библиотеке «SOURCE» генератор логических импульсов DigClock и установить по одному генератору напротив каждого входа дешифратора.

8.Ввести параметры генераторов, для чего дважды щелкнуть мышью на изображении каждого генератора. В появившемся окне (рис.2.2) ввести время задержки DELAY=0, длительность сигнала логической единицы ONTIME и логического нуля OFFTIME. Импульсы прямоугольные, длительность импульса равна длительности паузы. При каждом вводе нажимать «SaveAttr»; в конце нажать «CLOSE».

Рис.2.2 Окно параметров генератора

9.Соединить выходы генераторов с соответствующими вхо-

дами дешифратора, для чего нажать кнопку  и провести линию соединения, отмечая щелчками мыши начало и конец проводника, а также точки излома.

и провести линию соединения, отмечая щелчками мыши начало и конец проводника, а также точки излома.

10.Пометить точки, напряжения в которых следует отразить в виде графиков в редакторе Probe. Для этого войти в меню

Markers, выбрать Mark Voltage/Level и установить метки на нужные узлы, причем в том порядке, в котором они должны быть отражены, а именно: входные узлы - от старшего разряда к младшему, выходные - от нулевого к n- му. Данная операция может быть пропущена, так как в графическом постпроцессоре Probe предусмотрена возможность выбора выводимых на экран параметров анализа независимо от наличия меток в исходной цепи.

Установить параметры анализа, для чего нажать кнопки

, «Transient» и в строке Print Step установить шаг вывода данных - порядка 0,1мкс, а в строке Final Time - полное время анализа, равное самому большому периоду входных генераторов, нажать «OK» и «Close».

, «Transient» и в строке Print Step установить шаг вывода данных - порядка 0,1мкс, а в строке Final Time - полное время анализа, равное самому большому периоду входных генераторов, нажать «OK» и «Close».

11.Запустить программу PSpice А_D, для чего нажать кнопку

. При отсутствии ошибок в схеме будет создан лист соединений (Netlist) и запущен графический постпроцес-

. При отсутствии ошибок в схеме будет создан лист соединений (Netlist) и запущен графический постпроцес-

сор Probe.

12.Если при вводе схемы не были указаны метки, то необходимо определить те величины, графики которых должны быть выведены на экран. Для этого следует нажать кнопку

, после чего на экране появится окно со списком параметров и наименованиями узлов, в которых эти параметры необходимо снять. В этом списке (в левой колонке) необходимо выбрать входные и выходные узлы (обычно они маркируются в виде <обозначение элемента на схеме>:<обозначение узла>, например U1:A – сигнал на входе А элемента U1, U1:Y0 – сигнал на входеY0 элемента U1 и т.д. ) При выборе того или иного сигнала его наименование записывается в строку внизу экрана.

, после чего на экране появится окно со списком параметров и наименованиями узлов, в которых эти параметры необходимо снять. В этом списке (в левой колонке) необходимо выбрать входные и выходные узлы (обычно они маркируются в виде <обозначение элемента на схеме>:<обозначение узла>, например U1:A – сигнал на входе А элемента U1, U1:Y0 – сигнал на входеY0 элемента U1 и т.д. ) При выборе того или иного сигнала его наименование записывается в строку внизу экрана.

30 |

31 |

13.Для построения таблицы истинности нажать кнопку  и перемещая появившийся курсор слева направо выписать значения на входе и соответствующие им наборы значений на выходе. Состояние каждого узла описывается цифрой у вертикальной оси.

и перемещая появившийся курсор слева направо выписать значения на входе и соответствующие им наборы значений на выходе. Состояние каждого узла описывается цифрой у вертикальной оси.

2.2.ИССЛЕДОВАНИЕ ШИФРАТОРОВ И ДЕШИФРАТО-

РОВ

2.2.1. Исследование дешифратора 7442А

Рассмотрим схемотехническое моделирование микросхем на примере интегральной микросхемы 7442а (отечественный аналог К555ИД6), представляющей собой дешифратор, преобразующий двоичный четырехразрядный код в унитарный код “1 из 10”. Входные рабочие сигналы - высокого уровня, выходные - низкого.

Назначение выводов микросхемы: А-D-входы, Y0-Y9- выходы. Схема измерения дешифратора приведена на рис.2.3.

Рис.2.3 - Схема измерения дешифратора

Для составления задания на моделирование следует согласно п.1.10 раздела 2.1 ввести в графическом режиме схему изме-

рения и установить параметры генераторов, к примеру, следующим образом:

Х1: ONTIME = OFFTIME = 1us; Х2: ONTIME = OFFTIME = 2us; Х3: ONTIME = OFFTIME = 4us; Х4: ONTIME = OFFTIME = 8us.

Остальные параметры принимаются по умолчанию. Далее согласно пп.11,12 раздела 2.3 следует установить

время анализа равным не менее 16 us с шагом около 0,1 us и войти в графический постпроцессор Probe программы PSpice А_D. Там согласно п.13 раздела 2.3 выбрать входные и выходные узлы микросхемы и, выведя временные диаграммы (рис.2.4), используя указания п.13 раздела 2.1 снять таблицы переключения в виде табл.2.1.

Рис.2.4 Временные диаграммы сигналов дешифратора

SN7442A

Таблица 2.1 Таблица истинности дешифратора 7442a

32 |

33 |

D |

C |

B |

A |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

Y8 |

Y9 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

2.3 ИНДИВИДУАЛЬНЫЕ ЗАДАНИЯ ДЛЯ СХЕМОТЕХНИЧЕСКОГО МОДЕЛИРОВАНИЯ

2.3.1.Провести схемотехническое моделирование дешифратора 7443а

Микросхема 7443а (отечественный аналог отсутствует) представляет собой дешифратор, преобразующий двоичный четырехразрядный код в унитарный код “1 из 10”. Входные рабочие сигналы - высокого уровня, выходные - низкого.

Назначение выводов микросхемы: А-D-входы, Y0-Y9- выходы. Схема измерения дешифратора приведена на рис.

2.5.В процессе выполнения работы должны быть получены временные диаграммы входных и выходных сигналов, а также таблица истинности - в виде табл.2.1.

2.3.2.Провести схемотехническое моделирование дешифратора 7444а

Микросхема 7444а (отечественный аналог отсутствует) пред-

ставляет собой дешифратор, преобразующий двоичный четырехразрядный код в унитарный код “1 из 10”. Входные

Рис.2.5 Схема измерения дешифратора

рабочие сигналы - высокого уровня, выходные - низкого. Следует отметить, что при дешифрации номер выхода, на котором появляется сигнал, не всегда соответствует двоичному числу на входе, поэтому ряд состояний является нерабочими.

Рис.2.6 Схема измерения дешифратора

34 |

35 |

Назначение выводов микросхемы: А-D-входы, Y0-Y9- выходы. Схема измерения дешифратора приведена на рис.2.6. В процессе выполнения работы должны быть получены временные диаграммы входных и выходных сигналов, а также таблица истинности - в виде табл.2.1.

2.3.3 Провести схемотехническое моделирование дешифратора 74141

Микросхема 74141 (отечественные аналоги К155ИД1, КМ155ИД1) представляет собой дешифратор, преобразующий двоичный четырехразрядный код в унитарный код “1 из 10”. Входные и выходные рабочие сигналы - высокого уровня.

Рис.2.7 Схема измерения дешифратора

Назначение выводов микросхемы: А-D-входы, О0-О9- выходы. Схема измерения дешифратора приведена на рис2.7. В процессе выполнения работы должны быть получены временные диаграммы входных и выходных сигналов, а также таблица истинности - в виде табл.2.1, заменив соответственно

Y0..Y9 на O0..O9.

2.3.4. Провести схемотехническое моделирование дешифратора - демультиплексора 74154

Микросхема 74154 (отечественные аналоги К155ИД4, К1533ИД4) представляет собой дешифратор - демультиплексор. Для обеспечения работы схемы в качестве дешифратора, преобразующего двоичный четырехразрядный код в унитарный код “1 из 16” на входы G1 и G2 необходимо подать сигналы низкого уровня, для чего к ним подсоединяются порты низкого уровня Lo из библиотеки Port. Входные рабочие сигналы - высокого уровня, выходные - низкого.

Назначение выводов микросхемы: А-D-адресные входы, Y0-Y15-выходы, G1,G2-информационные входы. При работе в режиме дешифрации на информационные входы подаются сигналы низкого уровня, распределяемые по выходам в соответствии с сигналами на адресных входах, которые при этом и являются фактически входами дешифратора. Схема измерения дешифратора - демультиплексора приведена на рис.2.8. В процессе выполнения работы должны быть получены временные диаграммы входных и выходных сигналов, а также таблица истинности - в виде табл.2.2.

Рис.2.8 Схема измерения дешифратора-демультиплексора Таблица 2.2

36 |

37 |

Таблица истинности дешифратора 74154

YYYYYY DCBAY0Y1Y2Y3Y4Y5Y6Y7Y8Y9101112131415

2.3.5. Провести схемотехническое моделирование дешифратора “из 3 в 8”, составленного из логических элементов

Для выполнения задания необходимо ввести схему дешифратора, преобразующего трехразрядный двоичный код в унитарный код “1 из 8”, составленную из логических элемен-

тов библиотеки «DigitalPrim» (рис.2.9).

Схема включения элементов приведена на рис.2.9. Назначение выводов схемы: X1-X3 - входы, Y0-Y7-выходы. В процессе выполнения работы должны быть получены временные диаграммы входных и выходных сигналов, а также таблица истинности - в виде табл.2.3.

Таблица 2.3 Таблица истинности дешифратора

Y7 |

Y6 |

Y5 |

Y4 |

Y3 |

Y2 |

Y1 |

Y0 |

X3 |

X2 |

X1 |

|

|

|

|

|

|

|

|

|

|

|

2.3.6. Провести схемотехническое моделирование шифратора 74147

Микросхема 74147 (отечественный аналог К555ИВ3) представляет собой шифратор, преобразующий унитарный код “1 из10” в двоичный четырехразрядный. Входные рабочие сигналы - низкого уровня, выходные - высокого.

Рис.2.10 Схема измерения шифратора

Рис.2.9 Схема дешифратора

Назначение выводов микросхемы: A-D - входы, IN1-IN9 - выходы. Схема измерения шифратора приведена на рис.2.10.

38 |

39 |