Методические указания к лабораторным работам по дисциплине «Архитектура построения и средства защиты СПЦС». Мордовин А.И., Остапенко А.Г

.pdfФГБОУ ВПО «Воронежский государственный технический университет»

Кафедра систем информационной безопасности

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

к лабораторным работам по дисциплине «Архитектура построения и средства защиты СПЦС» для студентов специальности

090302 «Информационная безопасность телекоммуникационных систем» очной формы обучения

Воронеж 2014

Составитель аспирант А.И. Мордовин

УДК 004.056

Методические указания к лабораторным работам по дисциплине «Архитектура построения и средства защиты СПЦС» для студентов специальности 090302 «Информационная безопасность телекоммуникационных систем» очной формы обучения / ФГБОУ ВПО «Воронежский государственный технический университет»; сост. А.И. Мордовин. Воронеж, 2014. 25 с.

Методические указания посвящены исследованию архитектуры, систем команд и методов программирования СПЦС.

Методические указания подготовлены в электронном виде в текстовом редакторе MSWord 2013 и содержатся в файле Мордовин_ЛР_АПиСЗ СПЦС.pdf.

Ил. 4. Библиогр.: 7 назв.

Рецензент д-р техн. наук, проф. А.Г. Остапенко

Ответственный за выпуск зав. кафедрой д-р техн. наук, проф. А.Г. Остапенко

Издается по решению редакционно-издательского совета Воронежского государственного технического университета

© ФГБОУ ВПО «Воронежский государственный технический университет», 2014

Лабораторная работа №1 Устройство аналого-цифрового 12-разрядного преобразователя микропроцессора МКC8051F120

Цель лабораторной работы заключается в изучении работы аналого-цифрового 12-разрядного преобразователя.

Задачи лабораторной работы:

изучить структуру 12-разрядного АЦП;

исследовать режимы работы 12-разрядного АЦП;

пошагово выполнить запуск преобразования и схему слежения.

Теоретические сведения

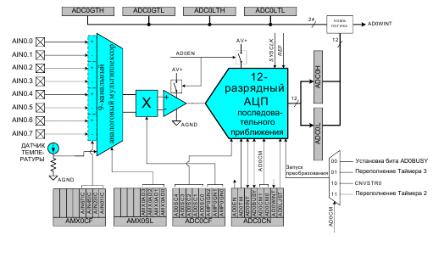

Модуль АЦП0 МК C8051F120 состоит из 9-канального программируемого аналогового мультиплексора (AMUX0), программируемого усилителя (PGA0), 12-разрядного АЦП последовательного приближения с производительностью до 100 тыс. преобразований в секунду, устройства выборкихранения (УВХ) и программируемого детектора диапазона (рис. 1). AMUX0, PGA0, режимы преобразования и детектор диапазона настраиваются программным путем при помощи регистров специального назначения. Модуль АЦП0 (АЦП0, УВХ и PGA0) включен только тогда, когда бит AD0EN регистра управления АЦП0 (ADC0CN) установлен в 1. Сброс этого бита в 0 переводит АЦП0 в режим пониженного энергопотребления [1].

Рис. 1. Структура 12-разрядного АЦП

Восемь каналов AMUX могут использоваться для измерения внешних сигналов, девятый канал подключен к внутреннему датчику температуры. Каждая пара входов AMUX могут быть запрограммированы на работу в однофазном или дифференциальном режимах. Это позволяет пользователю выбрать наиболее подходящий режим измерения, и даже производить изменение режимов “на лету”. При сбросе все каналы AMUX настраиваются как однофазные входы. Для управления AMUX используются два регистра: регистр выбора канала AMX0SL и регистр конфигурации AMX0CF. PGA усиливает выходной сигнал AMUX с коэффициентом усиления, определяемым битами AMP0GN2-0 регистра управления АЦП0 ADC0CF. Коэффициент усиления может быть программно выбран из следующего ряда значений: 0.5, 1 (устанавливается при сбросе), 2, 4, 8, 16 [2,3].

Бит AD0TM регистра ADC0CN управляет режимом выборки-хранения АЦП0. По умолчанию состояние входа АЦП0 отслеживается непрерывно, за исключением момента преобразования. Установка в 1 бита AD0TM переводит АЦП0 в энергосберегающий режим выборки-хранения. В этом

2

режиме каждому преобразованию предшествует (после сигнала запуска преобразования) период выборки, равный трем периодам сигнала дискретизации АЦП. Если для запуска преобразования в энергосберегающем режиме выборкихранения используется сигнал CNVSTR0, то АЦП0 отслеживает входной сигнал только тогда, когда на входе CNVSTR0 присутствует сигнал низкого уровня; преобразование запускается нарастающим фронтом сигнала на входе CNVSTR0. Кроме этого слежение может быть запрещено (отключено), когда весь МК переведен в мало потребляющие режимы ожидания или остановки. Энергосберегающий режим выборки-хранения также полезен в том случае, когда параметры AMUX и PGA часто изменяются, чтобы гарантировать, что время установления соответствует заданным требованиям [3].

Задание на лабораторную работу

Запуск преобразования АЦП0 может быть осуществлен одним из четырех способов, в зависимости от состояния битов режима запуска преобразования АЦП0 (AD0CM1, AD0CM0) в регистре ADC0CN.

Преобразование АЦП0 может быть инициировано:

1)установкой в 1 бита AD0BUSY в регистре ADC0CN;

2)переполнением Таймера 3 (т.е. непрерывное по времени преобразование);

3)нарастающим фронтом внешнего сигнала запуска преобразования АЦП (CNVSTR0);

4)переполнением Таймера 2 (т.е. непрерывное по времени преобразование).

Бит AD0BUSY устанавливается в 1 во время преобразования и сбрасывается в 0 после окончания преобразования. При сбросе бита AD0BUSY инициируется прерывание (если оно разрешено) и устанавливается флаг

3

прерывания AD0INT (ADC0CN.5). Преобразованные данные доступны в регистрах старшего и младшего слова данных АЦП0, ADC0H и ADC0L соответственно. В регистровой паре ADC0H:ADC0L преобразованные данные могут быть выровнены либо вправо, либо влево в зависимости от состояния бита AD0LJST в регистре ADC0CN.

Если преобразование инициируется установкой в 1 бита AD0BUSY, то для определения окончания преобразования следует опрашивать флаг AD0INT (можно также использовать прерывания от модуля АЦП0).

Ниже приведена рекомендуемая процедура опроса: Шаг 1: Сброс в 0 бита AD0INT.

Шаг 2: Установка в 1 бита AD0BUSY.

Шаг 3: Опрос битаAD0INT до тех пор, пока он не станет равен 1.

Шаг 4: Обработка данных АЦП0.

Контрольные вопросы:

1)Структура модуля АЦП.

2)Основные регистры АЦП.

3)Описание бита управления режимом АЦП

4

Лабораторная работа №2

Анализ источников сброса микропроцессора С8051F120

Цель лабораторной работы заключается в исследовании различных источников сброса микропроцессора С8051F120.

Задачи лабораторной работы:

рассмотреть сброс при включении питания;

изучить сброс работы микропроцессора при отключении питания;

провести анализ источников внешнего сброса работы микропроцессора.

Теоретические сведения

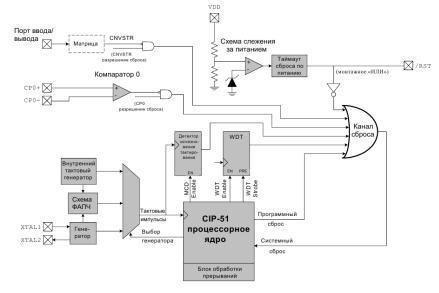

Схема сброса позволяет легко перевести МК в предопределенное по умолчанию состояние. При переходе к этому состоянию сброса происходит следующее:

-CIP-51 останавливает выполнение программы;

-регистры SFR инициализируются значениями по умолчанию;

-выводы внешних портов устанавливаются в известное состояние;

-прерывания и таймеры запрещаются [3].

Все регистры SFR принимают значения по умолчанию. В подробном описании каждого регистра SFR приведено значение, загружаемое в этот регистр при сбросе. Содержимое внутренней памяти данных не изменяется при сбросе и ранее сохраненные данные остаются неизменными. Однако, так как регистр указателя стека сбрасывается, стек фактически теряется, хотя данные в нем не изменяются [1].

Защелки портов ввода/вывода сбрасываются в состояние 0xFF (все логические единицы), активируя внутренние слаботоковые подтяжки в течение и после сброса. Если источником сброса является схема слежения за

5

напряжением питания, то на выводе /RST удерживается низкий логический уровень до истечения таймаута сброса по питанию[2].

При выходе из состояния сброса программный счетчик (РС) сбрасывается и МК использует (по умолчанию) внутренний тактовый генератор, работающий на минимальной тактовой частоте. Сторожевой таймер включен и настроен на максимальный таймаут. Выполнение программы начинается с адреса 0x0000 после выхода источника системного тактового сигнала на стабильный режим работы.

Семь источников могут перевести МК в состояние сброса: включение/исчезновение питания, внешний вывод /RST, внешний сигнал CNVSTR0, программный сброс, компаратор 0, детектор исчезновения тактирования, сторожевой таймер [1,4].

МКC8051F120 содержат схему слежения за напряжением питания, которая удерживает МК в состоянии сброса, пока напряжение питания VDD не превысит в процессе включения уровень VRST.

В течение таймаута схемы слежения за напряжением питания (100 мс) на выводе /RST удерживается низкий логический уровень, что позволяет напряжению питания стабилизироваться. Для разрешения/запрещения сброса от схемы слежения за напряжением питания используется внешний вывод MOVEN. Если схема слежения за напряжением питания включена, то она выбирается в качестве источника сброса с помощью бита PORSF. Если значение в регистр RSTSRC записывается программным обеспечением, то для разрешения сброса от схемы слежения за напряжением питания бит PORSF (RSTSRC.1) следует установить в 1.

6

Рис. 2. Структурная схема источников сброса

При завершении сброса типа POR флаг PORSF (RSTSRC.1) аппаратно устанавливается в 1. Состояние всех других флагов сброса в регистре RSTSRC являются неопределенным. Флаг PORSF сбрасывается в 0 при сбросе от любого другого источника. Т.к. при сбросе любого типа выполнение программы начинается с одного и того же адреса (0x0000), программа может опросить флаг PORSF, чтобы определить, было ли включение питания причиной сброса. Содержимое внутренней памяти данных после сброса типа POR следует считать неопределенным [2].

Когда при выключении или сбое питания напряжение питания VDD опускается ниже уровня VRST, схема слежения за напряжением питания установит на выводе /RST низкий логический уровень и переведет CIP-51 в состояние сброса. Когда VDD превысит уровень VRST, CIP-51 выйдет из состояния сброса точно так же, как при сбросе типа POR. Следует иметь ввиду, что, хотя содержимое внутренней памяти данных и не изменяется при сбросе типа PFR,

7

невозможно определить, опускалось ли напряжение VDD ниже уровня, необходимого для сохранения данных. Если флаг PORSF установлен в 1, данные нельзя более считать действительными.

Задание на лабораторную работу

МК содержит программируемый сторожевой таймер (WatchdogTimer - WDT), работающий независимо от системного тактового сигнала. WDT переводит МК в состояние сброса в случае своего переполнения. Чтобы предотвратить сброс, WDT должен перезапускаться из прикладной программы до того, как произойдет его переполнение. Если в системе происходит программный/аппаратный сбой, не позволяющий программе перезапустить WDT, то WDT переполнится и вызовет сброс. Это предотвращает выход системы из под контроля.

После сброса любого типа WDT автоматически включается и запускается по умолчанию с максимальным таймаутом. При необходимости WDT можно программно отключить или заблокировать, предотвратив его случайное отключение. После блокировки WDT его нельзя отключить доследующего системного сброса. Состояние вывода /RST не влияет на сброс этого типа [3].

WDT состоит из 21-разрядного таймера, работающего с программируемой тактовой частотой. Этот таймер измеряет период между операциями записи определенных значений в его регистр управления. Если этот период превышает установленный предел, то генерируется сброс от WDT. WDT может быть программно разрешен или запрещен, кроме этого можно заблокировать функцию отключения WDT. Управление WDT осуществляется посредством регистра управления WDT (WDTCN).

WDT как включается, так и сбрасывается записью значения 0xA5 в регистр WDTCN. Программа пользователя должна периодически записывать значение 0xA5 в регистр

8