- •А.В. Строгонов а.В. Быстрицкий с.И. Давыдов м.С. Мотылев д.С. Шацких

- •Введение

- •Цифровые бис

- •Специализированные бис

- •1.2. Программируемые логические ис

- •1.3. Академические плис

- •1.4. Индустриальные плис фирмы Altera

- •1.4.1. Семейство плис max3000 и max7000

- •1.4.2. Семейство плис flex6000 и flex10k

- •1.4.3. Семейство плис apex20k

- •1.4.4. Семейство плис Stratix III

- •1.5. Программные средства проектирования плис

- •2. Трехмерные интегральные схемы 3d бис

- •2.1. Проблемы, связанные с проектированием бис по субмикронным проектным нормам, и методы их решения

- •2.2. Стековые 3d бис

- •2.3. Транзисторы для "Платформы 2015"

- •3. Проектирование плис типа ппвм

- •3.1. Разработка функциональной модели плис типа ппвм в сапр Quartus II с использованием технологии соединений multi-driver

- •3.2. Разработка модели плис типа ппвм с одноуровневой структурой межсоединений с использованием технологии соединений single-driver в системе визуально-иммитационного моделирования Matlab/Simulink

- •Заключение

- •394026 Воронеж, Московский просп., 14

1.3. Академические плис

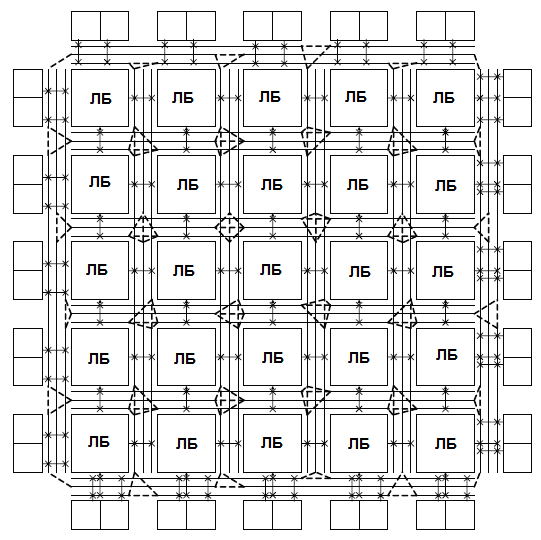

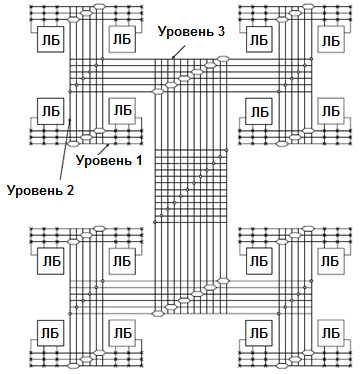

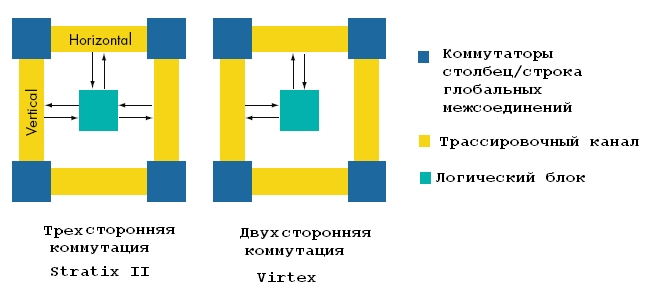

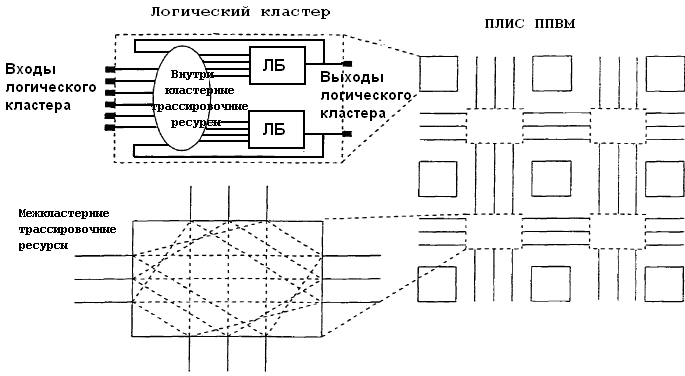

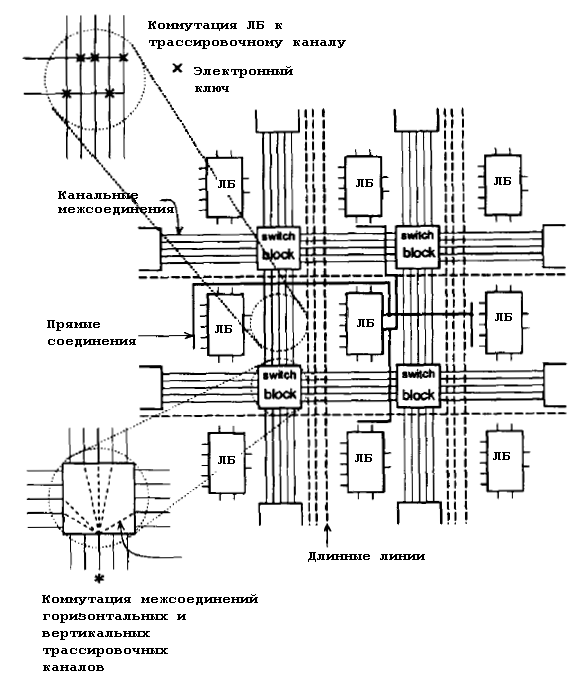

Большинство коммерческих архитектур ПЛИС типа ППВМ (программируемые пользователем вентильные матрицы, FPGA) по технологии СОЗУ имеет одноуровневую структуру, когда логические блоки окружены с четырех сторон межсоединениями горизонтальных и вертикальных трассировочных каналов, равномерно распределенных по всей площади кристалла (рис.1.7) или многоуровневую структуру (рис.1.8). В ПЛИС семейств Stratix используется трехсторонняя трассировочная структура, а в ПЛИС Virtex-5 - двухсторонняя (рис.1.9). Уровень 1 использует прямые соединения, а уровень 2 и 3 программируемые соединения, которые отмечены кружками в пересечениях соединений. С повышением уровня соединений, при удалении от логических блоков, возрастает ширина трассировочных каналов.

Большинство фирм выпускает сложные одноуровневые ПЛИС, располагая LUT-таблицы входящие в состав ЛБ в виде квадратной матрицы на площади кристалла, при этом связи между LUT-таблицами выполняются в виде соединений (треков или дорожек), разделенных на отдельные участки (сегменты) электронными ключами (рис.1.7).

Иерархическая (многоуровневая) организация ПЛИС позволяет улучшить их технические характеристики (рис.1.8). Функциональные преобразователи в этом случае группируются в блоки (например, в логический блок ПЛИС семейства FLEX фирмы Altera входит 8 логических элементов), имеющие свою собственную локальную шину межсоединений. Логические блоки обмениваются сигналами через шины межсоединений верхнего уровня. Межсоединения (проводники) в каналах непрерывны (т.е. не разделены на сегменты электронными ключами), что обеспечивает малые задержки распространения сигналов между логическими блоками и позволяет существенно сократить количество электронных ключей.

Рис.1.7. Одноуровневая структура ПЛИС типа ППВМ

Рис.1.8. Многоуровневая структура ПЛИС типа ППВМ (FLEX10K, APEX, APEX II фирмы Altera)

Рис.1.9. Трассировочная структура межсоединений в ПЛИС типа ППВМ Stratix фирмы Altera и Virtex фирмы Xilinx

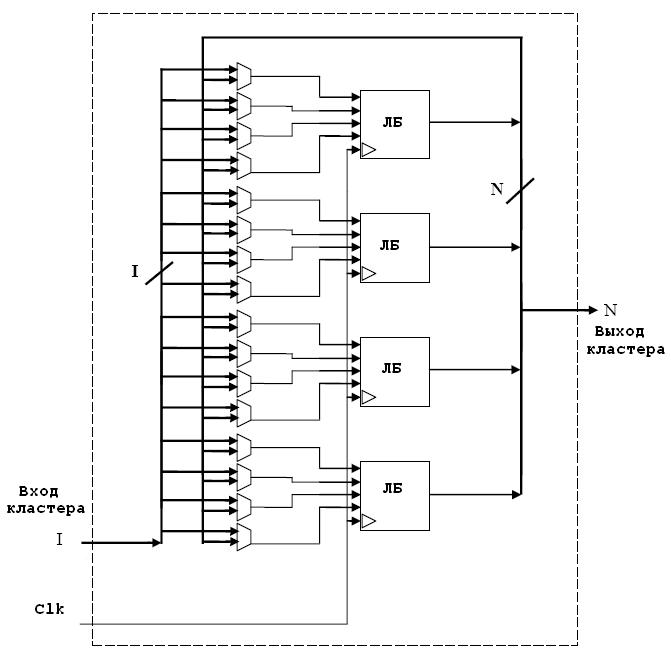

Для одноуровневой и многоуровневой структуры ПЛИС логические блоки зачастую выгодно объединять в кластеры (рис.1.10). Так, под терминологией конфигурируемый логический блок фирмы Altera подразумевается кластер из 8 логических блоков (для ПЛИС серии FLEX10K).

Для ранних архитектур ПЛИС Xilinx серий XC3000 и XC4000 (рис.1.11) характерно: наличие канальных межсоединений разделенных электронными ключами в коммутационном блоке; прямые межсоединения, соединяющие выходы логического блока (ЛБ) со входами/выходами четырех соседних ЛБ; длинные горизонтальные и вертикальные линии проходящие вдоль всего кристалла; сеть тактовых синхросигналов, охватывающая весь кристалл, подключаемая к синхровходам триггеров ЛБ.

а)

б)

Рис.1.10. Объединение логических блоков в кластеры (а) и использование кластеров в одноуровневых ПЛИС типа ППВМ (б)

Рис.1.11. Архитектура ПЛИС типа ППВМ Xilinx 3000

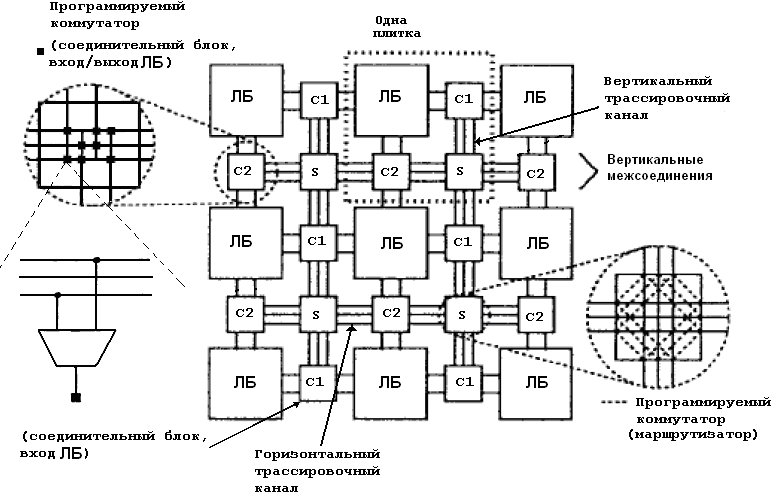

ПЛИС с одноуровневой структурой межсоединений представляют массив логических блоков (логических элементов) подключаемых с помощью соединительных блоков C1 и C2 к вертикальным и горизонтальным трассировочным каналам межсоединений (рис.1.12). Блок С1 подключает один из входов (второй) LUT-таблицы и сигнал set/reset к вертикальному каналу, а блок С2 подключает один из входов (третий) и выход ЛЭ к горизонтальному каналу. Соединительные блоки C1 и C2 представляют собой программируемые коммутаторы на мультиплексорных структурах, позволяющие подключать любое межсоединение из горизонтального или вертикального трассировочных каналов на один из входов логического блока. Блок С2 подключает любое межсоединение из канала к входу in3, а блок C1 подключает любое межсоединение из канала к входу in2. Для коммутации выходов ЛБ в блоке C2 используются коммутаторы (демультиплексоры) типа track-to-pin (один n-МОП ключ на каждое соединение) на проходных n-МОП ключах. В соединительных блоках C1 и C2 в качестве буферных элементов используются два последовательно соединенных инвертора.

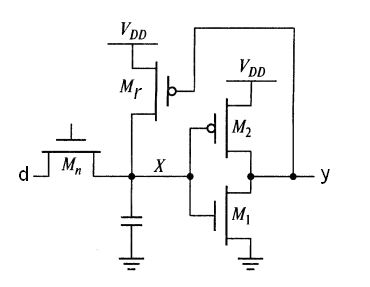

Коммутация межсоединений в каналалах осуществляется с помощью программируемого коммутатора-маршрутизатора (S-блок) представляющего из себя два шеститранзисторных n-МОП ключа, два непрерывных прямых горизонтальных каналов и два вертикальных канала. Совместно с n-МОП ключем применяется буфер восстановления уровня сигнала (рис.1.13), т.к. при использовании n-МОП ключей высокий уровень в цепочке снижается после каждого элемента на величину порогового напряжения. Буфер с восстановлением уровня с p-МОП транзистором в обратной связи широко используется в коммутаторах межсоединений коммерческих ПЛИС, например, серии Flex, Stratix фирмы Altera.

Рис.1.12. Архитектура академических ПЛИС

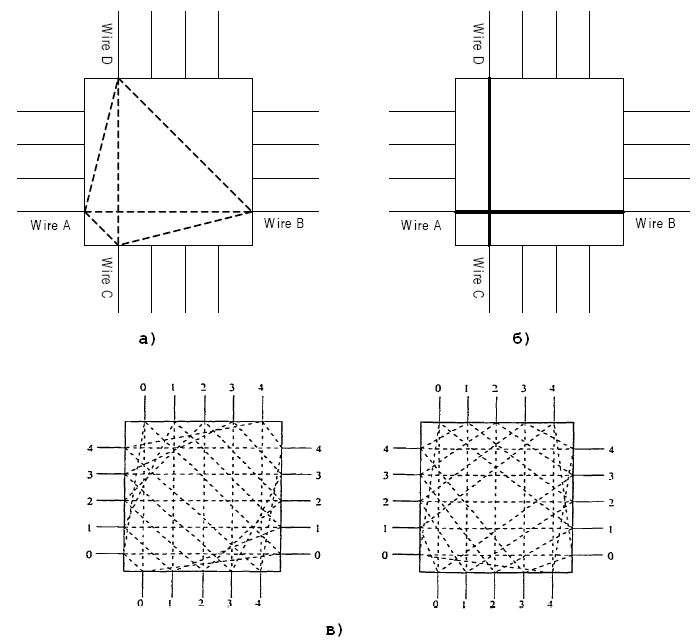

Замена программируемого межсоединения на жесткое, показано на рис.1.14. Пунктиром показаны направления коммутации межсоединений определяемые конфигурационными ключами. Что позволяет уменьшить число конфигурационных ячеек памяти, буферов восстановления уровня сигнала и существенно увеличить быстродействие ПЛИС.

Рис.1.13. Схема буфера с восстановлением уровня с p-МОП транзистором (фиксатором) в положительной обратной связи

Рис.1.14. Замена программируемого соединения (а) на жесткое (б) высокоскоростное соединение и различные варианты реализации коммутационного блока (в)