- •Функциональные узлы вычислительной техники методические указания

- •Состав и задачи цикла работ

- •2.2. Функциональные схемы коммутаторов

- •2.3. Реализации коммутаторов сообщений

- •3. Порядок выполнения лабораторной работы

- •3.1. Предварительное задание

- •3.2. Рабочее задание

- •4. Контрольные вопросы

- •2.2 Преобразование триггеров

- •3. Порядок выполнения лабораторной работы

- •3.1. Предварительное задание

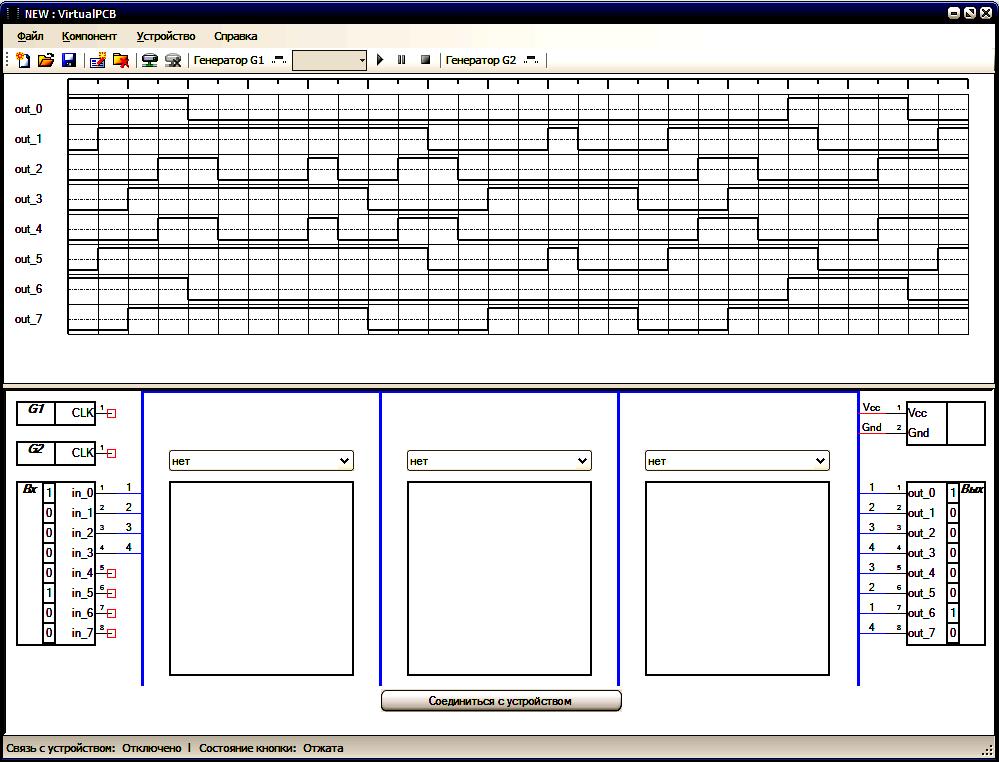

- •3.2. Рабочее задание

- •4. Контрольные вопросы

- •2.2. Специальные счетчики и делители

- •2.3. Микросхема ие7

- •2.4. Делители на базе счетчика ие7

- •3. Порядок выполнения лабораторной работы

- •3.1. Предварительное задание

- •3.2. Рабочее задание

- •4. Контрольные вопросы

- •3. Порядок выполнения работы

- •3.1. Предварительное задание

- •3.2. Рабочее задание

- •4. Контрольные вопросы

- •Библиографический список

- •Содержание

- •394026 Воронеж, Московский просп., 14

ФГБОУ ВПО «Воронежский государственный технический университет»

Кафедра электропривода, автоматики и управления в технических системах

Функциональные узлы вычислительной техники методические указания

к выполнению лабораторных работ № 4-6

по дисциплине «Вычислительная техника»

для студентов направления 221000.62 «Мехатроника и робототехника»

(профиль «Промышленная и специальная робототехника»)

очной формы обучения

Воронеж 2014

Составитель канд. техн. наук М.И. Герасимов

УДК 681.3-181.48:621.865.8

Функциональные узлы вычислительной техники: методические указания к выполнению лабораторных работ № 4-6 по дисциплине "Вычислительная техника" для студентов направления 221000.62 «Мехатроника и робототехника» (профиль «Промышленная и специальная робототехника») очной формы обучения / ФГБОУ ВПО «Воронежский государственный технический университет»; сост. М.И. Герасимов. Воронеж, 2014. 39 с.

Методические указания содержат теоретические сведения об устройстве и принципах работы исследуемых комбинационных и последовательностных узлов ВТ, предварительное и рабочее задания, определяющие порядок исследования, контрольные вопросы.

Предназначены для студентов 3 курса очной формы обучения.

Методические указания подготовлены в электронном виде в текстовом редакторе MS Word 2003 и содержатся в файле МУ_лаб_ВТ 4-6.doc.

Ил. 17. Библиогр.: 10 назв.

Рецензент канд. техн. наук, доц. В.А. Медведев

Ответственный за выпуск зав. кафедрой д-р техн. наук, проф. В.Л. Бурковский

Издается по решению редакционно-издательского совета Воронежского государственного технического университета

©

Состав и задачи цикла работ

Программа дисциплины "Вычислительная техника" предусматривает проведение для студентов очной формы обучения семи лабораторных работ (36 часов).

Наименование лабораторной работы |

Кол-во часов |

1. Изучение лабораторного стенда, овладение навыками коммутации схем на стенде |

4 |

2. Синтез комбинационного автомата |

4 |

3. Синтез и исследование двоичных шифраторов |

8 |

4. Исследование коммутаторов информационных потоков |

4 |

5. Исследование триггеров |

4 |

6. Исследование счетчика / делителя |

4 |

7. Синтез и исследование кольцевых коммутаторов |

8 |

ВСЕГО |

36 |

Содержание цикла лабораторных работ – изучение свойств основных функциональных узлов ВТ, выполненных на цифровых микросхемах. В результате студент должен научиться читать принципиальные схемы узлов ВТ, а также синтезировать эти узлы, приобрести начальные навыки их экспериментального исследования.

Проведение каждой лабораторной работы включает этапы подготовки, выполнения работы, оформления и защиты отчета. Каждая лабораторная работа требует ориентировочно 2 часа на подготовку к выполнению и 2 часа на оформление отчета и подготовку к его защите. Это время предусмотрено в учебном плане как самостоятельная работа.

Общие положения по организации лабораторных работ, общие положения по их подготовке и проведению, требования к оформлению отчета по работе, инструкция по технике безопасности, устройству лабораторного стенда, материалы для лабораторных работ 1-3 помещены в /1/. Данные Методические указания содержат материалы для лабораторных работ 4-7.

Лабораторная работа № 4 ИССЛЕДОВАНИЕ КОММУТАТОРОВ ИНФОРМАЦИОННЫХ ПОТОКОВ

1. ЦЕЛЬ РАБОТЫ

1.1. Изучить принципы функционирования мультиплексоров и демультиплексоров.

1.2. На примере схемы полного трехразрядного коммутатора получить практические навыки разработки функциональных узлов вычислительной техники.

2. ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

2.1. Определение коммутаторов информационных потоков

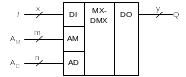

Определим одноканальные коммутаторы сообщений как комбинационные устройства, имеющие x информационных входов, y выходов, m адресных входов для выбора источника входной информации и n адресных входов для выбора одного из выходов и выполняющие передачу информации с одного выбранного двоичным адресным кодом входа на единственный выбранный выход. Графическое обозначение такого коммутатора будет иметь вид, приведенный на рис. 4.1.

Рис. 4.1

Рис. 4.1

В общем случае коммутаторы сообщений могут иметь также входы Е разрешения ввода, входы ОЕ разрешения вывода информации и входы/выходы других специальных сигналов. Коммутаторы сообщений могут быть многоканальными, в этом случае все группы входов или выходов управляются общими сигналами адреса и общими или раздельными сигналами Е, ОЕ. Количество адресных входов (разрядность коммутатора m, n) в зависимости от количества информационных входов/выходов определяется соотношениями

m = int (log2x), n = int (log2y),

где int означает округление в бóльшую сторону до целого числа.

Коммутаторы с m =log2x, n = log2y называют полными, а с m < log2 x, n < log2y – неполными.

Разновидность коммутаторов сообщений, которые имеют несколько информационных входов и один выход (многоканальные – несколько выходов) и которые обеспечивают передачу информации на выход со входа, выбранного адресным кодом, называют мультиплексорами, а также мультиплексорами-селекторами (или просто коммутаторами). Соответственно функциональное обозначение на УГО имеет вид MUX, MX или MS. Если обозначить информационный поток на входе 0 как I0, на входе 1 как I1, и т.д., а сигнал на выходе как Q, то, например, таблица функционирования мультиплексора 8-1 будет иметь вид

Н

А2

А1 А0 Q

0

0 0 I0

0

0 1 I1

0 1 0 I2

0 1 1 I3

1 0 0 I4

1 0 1 I5

1 1 0 I6

1 1 1 I7

Разновидность коммутаторов сообщений, которые имеют один информационный вход (многоканальные – несколько входов) и несколько выходов и которые обеспечивают передачу информации с входа на выход, выбранный адресным кодом, называют демультиплексорами. Их функциональное обозначение на УГО – DMX. Если обозначить информационный поток на входе как I, а сигналы на выходах как Q0...Q7, то таблица функционирования демультиплексора 1-8 будет иметь вид

А2 А1 А0 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

0 0 0 I 0 0 0 0 0 0 0

0 0 1 0 I 0 0 0 0 0 0

0 1 0 0 0 I 0 0 0 0 0

0 1 1 0 0 0 I 0 0 0 0

1 0 0 0 0 0 0 I 0 0 0

1 0 1 0 0 0 0 0 I 0 0

1 1 0 0 0 0 0 0 0 I 0

1 1 1 0 0 0 0 0 0 0 I

Неполные демультиплексоры используются, например, для получения сигналов, соответствующих десятичной цифре (n=10) или для опознавания адреса устройства (минимальное значение n=1).